LAPORAN LABORATORIUM

PROGRAM STUDI TEKNIK TELEKOMUNIKASI

Praktikum 02

GERBANG LOGIKA

NAMA PRAKTIKAN : M Syaiful Islam (3314130012)

NAMA REKAN KERJA : Fainaya Permatasari (3314130024)

KATA PENGANTAR

Puji dan Syukur Penulis Panjatkan ke Hadirat Tuhan Yang Maha Esa karena berkat limpahan Rahmat dan Karunia-Nya sehingga penulis dapat menyelesaikan laporan laboratorium teknik digital berjudul "Gerbang Logika". Laporan tentang gerbang logikaini disusun untuk memenuhi salah satu tugas mata kuliah laboratorium teknik digital.

Penulisan laporan ini memiliki tujuan agar bisa memberikan informasi tentang membuktikan tabel kebenaran dari setiap gerbang logika, mengenali dan memperagakan gerbang logika dan membuktikan fungsi logicnya.

Dalam penyusunan laporan ini, penulis banyak mendapat tantangan dan hambatan akan tetapi dengan bantuan dari berbagai pihak tantangan itu bisa teratasi. Inilah batasan kesanggupan penulis dalam menulis laporan ini.

Penulis mengucapkan terima kasih kepada semua pihak yang telah membantu dalam penyusunan laporan ini.

Depok, Maret 2015 Penulis

M Syaiful Islam

BAB I PENDAHULUAN

1 . Tujuan

BAB II DASAR TEORI

Gerbang universal adalah salah satu gerbang dasar yang dirangkai sehingga menghasilkan output yang sama dengan gerbang dasar lainnya. Adapun gerbang universal tersebut adalah NAND gate dan NOR gate.

2.1 NAND Gate sebagai Inverter (NOT Gate)

NOT gate dapat dibuat dengan menggunakan NAND gate (Gambar 2.1). Bila input diberi nilai logik 1 maka outputnya menjadi logik 0 begitu juga sebaliknya.

Gambar 2.1. NAND Gate sebagai OR Gate

Gambar dibawah ini adalah tabel kebenaran dari NOT GATE dimana apabila A (inputannya) sama dengan 0 (nol) maka outputnya sama dengan 1(satu). Dan sebaliknya.

2.2 Gambar Tabel kebenaran NOT Gate

gambar diatas adalah rumus dari NOT Gate dimana arti dari simbol A dengan garis diatas adalah Outputan merupakan Kebalikkan dari Inputan.

A

(input)

Y

(output)

0 1

2.2 NAND Gate Sebagai AND Gate

AND gate dapat dibuat dengan menggunakan NAND gate (Gambar 2.2). Output dari suatu rangkaian AND gate akan berada pada keadaan logik 1 jika semua inputnya pada keadaan logik 1 dan output akan berada pada. keadaan logik 0 apabila salah satu inputnya atau semuanya pada keadaan logik 0.

2.3 Gambar Gerbang NAND Sebagai Gerbang AND

Untuk tabel Logika dasar dari AND GATE dengan dua inputan adalah sebagai berikut

A

2.4 Gambar Tabel Kebenaran AND Gate

2.3 NAND Gate Sebagai OR Gate

2.5 Gambar Gerbang NAND Sebagai Gerbang OR

Tabel Kebenaran dari OR Gate adalah seperti gambar berikut

A

(input)

B

(input)

Y

(output)

0 0 0

0 1 1

1 0 1

1 1 1

2.6 Gambar Tabel Kebenaran OR Gate

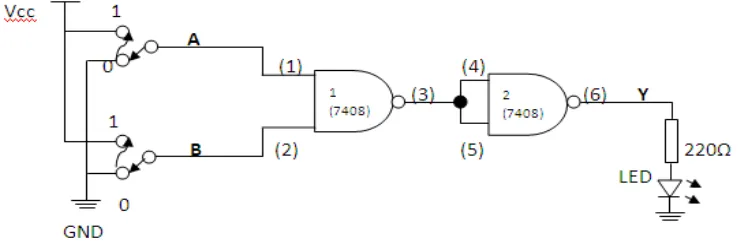

2.4. NAND Gate Sebagai NOR Gate

NOR gate dapat dibuat dengan menggunakan NAND gate (Gambar 2.4). NOR gate adalah gabungan dari suatu rangkaian NOT gate yang dipasang pada bagian output rangkaian OR gate. Output dari suatu rangkaian NOR gate akan berada pada keadaan logik 1 jika semua inputnya pada keadaan logik 1 dan output akan berada pada keadaan logik 0 apabila salah satu inputnya atau semuanya pada keadaan logik 0.

Sedangkan tabel kebenaran dari NAND Gate ini adalah seperti berikut

A

(input)

B

(input)

Y

(output)

0 0 1

0 1 1

1 0 1

1 1 0

BAB III PEMBAHASAN

3.1 Alat-Alat Yang Digunakan

NO Alat-Alat dan Komponen Jumlah

1. IC 7400 ( Quad 2 Input NAND Gate ) 1

2. Power Supply DC

(Pascal PS 1502A2 : 5VDC)

1

8 Kabel-kabel penghubung Secukupnya

3.2 Langkah-Langkah Percobaan

Langkah-langkah dalam melakukan percobaan gerbang universal adalah sebagai berikut :

E.1. NAND Gate sebagai Inverter (NOT Gate)

1. Lihat data sheet untuk IC 7400, catat kaki input, output serta pin Vcc dan Ground. 2. Atur tegangan power supply sebesar 5 Volt dengan cara menghubungkan

4. Berikan logik 0 dan/atau logik 1 pada input A sesuai tabel 6.1. 5. Amati LED serta ukur tegangan pada table 6.1.

E.2. NAND Gate sebagai AND Gate

1. Buat rangkaian seperti gambar 4.2.

2. Berikan logik 0 dan/atau logik 1 pada masing-masing input A dan input B sesuai tabel 6.2.

3. Amati LED serta ukur tegangan pada output Y. Catat hasilnya pada tabel 6.2.

E.3. NAND Gate sebagai OR Gate

1. Buat rangkaian seperti pada gambar 4.3.

2. Berikan logik 0 dan/atau logik 1 pada masing-masing input A dan input B sesuai tabel 6.3.

3. Amati LED serta ukur tegangan pada output Y. Catat hasilnya pada tabel 6.3.

E.4. NAND Gate sebagai NOR Gate

1. Buat rangkaian seperti pada gambar 4.4.

3. Amati LED serta ukur tegangan pada output Y. Catat hasilnya pada tabel 6.4.

F. PERTANYAAN DAN TUGAS

1. Apakah NOR Gate termasuk gerbang universal ? Jelaskan !

Ya ,NOR Gate termasuk gerbang universal.karena gerbang NOR Gate bisa menggantikan gerbang yang lain.

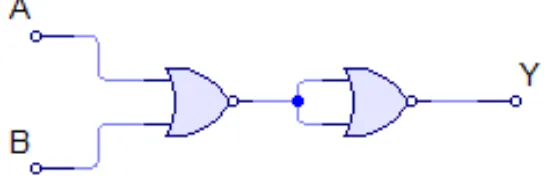

2. Dapatkah EX-OR Gate dibuat dari rangkaian NAND Gate, jelaskan !

EX-OR Gate dapat dibuat dengan menggunakan NAND Gate. EX-OR Gate adalah suatu rangkaian logik yang digunakan apabila diperlukan keadaan outputnya tinggi bila kedua input memiliki nilai logik yang berbeda dengan kata lain outputnya akan 1 dan outputnya

akan 0 apabila kedua input memiliki nilai logik yang sama.

Dapat, dan dapat dibuktikan dengan gambar di bawah ini:

A

Y

B

3. Buatlah rangkaian logika NOT Gate, AND Gate, NAND Gate, dan OR Gate dari rangkaian NOR Gate !

a. Gerbang NOT Menggunakan Gerbang Dasar NOR,

A B

b. Gerbang AND Menggunakan Gerbang Dasar NOR

d. Gerbang OR Menggunakan Gerbang Dasar NOR

4. Buatlah kesimpulan dari percobaan ini ! (Ada di BAB Penutup )

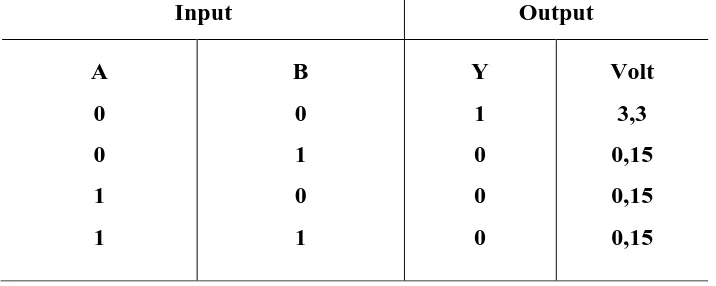

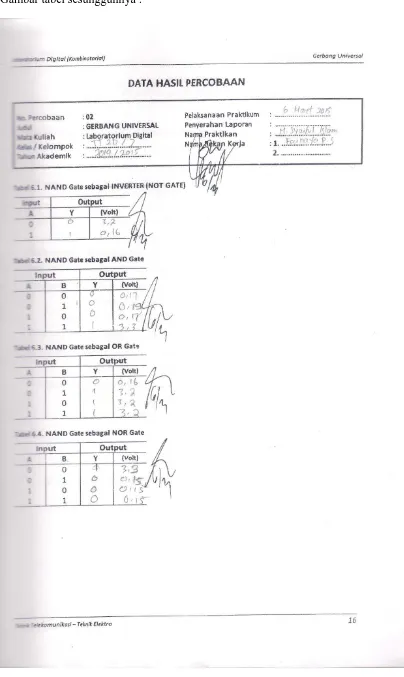

3.3 DATA HASIL PERCOBAAN

Tabel 6.1. NAND Gate sebagai Inverter (NOT GATE)

Tabel 6.2. NAND Gate Sebagai AND Gate

Tabel 6.2. NAND Gate Sebagai OR Gate

Tabel 6.2. NAND Gate Sebagai NOR Gate

BAB IV PENUTUP

4.1 Analisa Percobaan

1. NAND Gate sebagai Inverter (NOT GATE)

Saat inputan A di hubungkan ke ground dengan tegangan 0 V yang berarti

2. NAND Gate Sebagai AND Gate

Saat inputan A di hubungkan ke ground dengan tegangan 0 V yang berarti mendapatkan logik 0 dan inputan B di hubungkan ke ground dengan tegangan 0 V yang berarti mendapatkan logik 0, maka output yang di hasilkan bernilai logik 0 dengan tegangan sebesar 0,17 volt.

Saat inputan A di hubungkan ke vcc dengan tegangan 5 V yang berarti mendapatkan logik 1 dan inputan B di hubungkan ke ground dengan tegangan 0 V yang berarti mendapatkan logik 0, maka output yang di hasilkan bernilai logik 0 dengan tegangan sebesar 0,19 volt.

Saat inputan A di hubungkan ke ground dengan tegangan 0 V yang berarti mendapatkan logik 0 dan inputan B di hubungkan ke vcc dengan tegangan 5 V yang berarti mendapatkan logik 1, maka output yang di hasilkan bernilai logik 0 dengan tegangan sebesar 0,17 volt.

3. NAND Gate Sebagai OR Gate

Saat inputan A di hubungkan ke vcc dengan tegangan 0 V yang berarti mendapatkan logik 0 dan inputan B di hubungkan ke ground dengan tegangan 0 V yang berarti mendapatkan logik 0, maka output yang di hasilkan bernilai logik 0 dengan tegangan sebesar 0,16 volt.

Saat inputan A di hubungkan ke vcc dengan tegangan 5 V yang berarti mendapatkan logik 1 dan inputan B di hubungkan ke ground dengan tegangan 0 V yang berarti mendapatkan logik 0, maka output yang di hasilkan bernilai logik 1 dengan tegangan sebesar 3,2 volt.

Saat inputan A di hubungkan ke ground dengan tegangan 0 V yang berarti mendapatkan logik 0 dan inputan B di hubungkan ke vcc dengan tegangan 5 V yang berarti mendapatkan logik 1, maka output yang di hasilkan bernilai logik 1 dengan tegangan sebesar 3,2 volt.

Saat inputan A di hubungkan ke vcc dengan tegangan 5 V yang berarti mendapatkan logik 1 dan inputan B di hubungkan ke ground dengan tegangan 5 V yang berarti mendapatkan logik 1, maka output yang di hasilkan bernilai logik 1 dengan tegangan sebesar 3,3 volt.

4. NAND Gate Sebagai NOR Gate

Saat inputan A di hubungkan ke vcc dengan tegangan 0 V yang berarti mendapatkan logik 0 dan inputan B di hubungkan ke ground dengan tegangan 0 V yang berarti mendapatkan logik 0, maka output yang di hasilkan bernilai logik

1 dengan tegangan sebesar 3,3 volt.

Saat Saat inputan A di hubungkan ke ground dengan tegangan 0 V yang berarti mendapatkan logik 0 dan inputan B di hubungkan ke vcc dengan tegangan 5 V yang berarti mendapatkan logik 1, maka output yang di hasilkan bernilai logik 0 dengan tegangan sebesar 0,15 volt.

Saat inputan A di hubungkan ke vcc dengan tegangan 5 V yang berarti mendapatkan logik 1 dan inputan B di hubungkan ke ground dengan tegangan 5 V yang berarti mendapatkan logik 1, maka output yang di hasilkan bernilai logik 0 dengan tegangan sebesar 0,15 volt.

4.2 Kesimpulan