LAPORAN PRAKTIKUM

TEKNIK DIGITAL

MODUL I : RANGKAIAN GERBANG LOGIKA MODUL II : PENCACAH (COUNTER)

MODUL III : REGISTER

DISUSUN OLEH : Ahmad Khusnil Ibad

14101080

PARTNER PRAKTIKUM :

1. Lukman Fadhil Rizky .K (14101097) 2. Yusuf Budi Setyoso (14101117)

Dikumpulkan Tanggal : 20 Mei 2015

Asisten Praktikum : 1. Farah Izzah Fida Afifah 2. Lintang Setyo Palupi

3. Yusuf Ramli

LABORATORIUM

TEKNIK ELEKTRONIKA DAN TEKNIK DIGITAL SEKOLAH TINGGI TEKNOLOGI TELEMATIKA TELKOM

LAPORAN PRAKTIKUM

TEKNIK DIGITAL

MODUL I : RANGKAIAN GERBANG LOGIKA

DISUSUN OLEH : Ahmad Khusnil Ibad

14101080

PARTNER PRAKTIKUM : 1. Lukman Fadhil Rizky .K (14101097) 2. Yusuf Budi Setyoso (14101117)

Tanggal Praktikum : 27 April 2015

Asisten Praktikum : 1. Farah Izzah Fida Afifah 2. Lintang Setyo Palupi 3. Yusuf Ramli

LABORATORIUM

TEKNIK ELEKTRONIKA DAN TEKNIK DIGITAL SEKOLAH TINGGI TEKNOLOGI TELEMATIKA TELKOM

BAB I

KONFIGURASI SISTEM 1. Pengertian Gerbang Logika

Gerbang dasar logika merupakan suatu piranti elektronik berlogika biner dengan beberapa saluran masukan dan satu saluran keluaran. Keluaran gerbang AND berlogika 1 jika semua masukannya berlogika 1. Gerbang OR akan berlogika 1 jika sekurang-kurangnya salah satu masukannya berlogika 1. Sedangkan EXOR akan berlogika 1 jika masukannya berbeda. Gerbang NAND dan NOR berturut-turut merupakan lawan dari gerbang AND dan OR.

Gambar 1.1 Konfigurasi pin pada IC yang digunakan.

Total kombinasi yang memungkinkan adalah 2N, dimana N merupakan jumlah input, dalam hal ini maka N = 2 sehingga 22 = 4.

2. Macam-Macam Gerbang Logika a. Gerbang AND (AND GATE)

Gerbang AND mempunyai dua atau lebih sinyal masukan tetapi hanya mempunyai satu sinyal keluaran. Dalam gerbang AND, untuk menghasilkan sinyal keluaran tinggi maka semua sinyal masukan harus bernilai tinggi. Gerbang Logika AND pada Datasheet nama lainnya IC TTL 7408. Simbol gerbang AND ditunjukkan pada Gambar 2.1 Tabel kebenaran diperlihatkan pada Tabel 2.1

(a) Simbol (b) Persamaan Logika

Gambar 2.1 Gerbang AND

b. Gerbang OR (OR GATE)

Gerbang OR akan memberikan sinyal keluaran tinggi jika salah satu atau semua sinyal masukan bernilai tinggi, sehingga dapat dikatakan bahwa gerbang OR hanya memiliki sinyal keluaran rendah jika semua sinyal masukan bernilai rendah. Gerbang Logika OR pada Datasheet nama lainnya IC TTL 7432. Simbol gerbang OR ditunjukkan pada Gambar 2.2 Tabel kebenaran diperlihatkan pada Tabel 2.2.

(a) Simbol (b) Persamaan Logika Gambar 2.2 Gerbang OR

Tabel 2.2 Tabel Kebenaran Gerbang OR

c. Gerbang X-OR (-XOR GATE)

(a) Simbol (b) Persamaan Logika Gambar 2.3 Gerbang X-OR

Tabel 2.3 Tabel Kebenaran Gerbang X-OR

d. Gerbang NOT (NOT GATE)

Sebuah inverter (pembalik) adalah gerbang dengan satu sinyal masukan dan satu sinyal keluaran dimana keadaan keluarannya selalu berlawanan dengan keadaan masukannya. Gerbang Logika INV pada Datasheet nama lainnya IC TTL 7404. Simbol gerbang NOT ditunjukkan pada Gambar 2.4 Tabel kebenaran diperlihatkan pada Tabel 2.4.

7400. Simbol gerbang NAND ditunjukkan pada Gambar 2.5 Tabel kebenaran diperlihatkan pada Tabel 2.5.

(a) Simbol (b) Persamaan Logika Gambar 2.5 Gerbang NAND

Tabel 2.5 Tabel Kebenaran Gerbang NAND

f. Gerbang NOR (NOR GATE)

Gerbang NOR adalah suatu NOT-OR, atau suatu fungsi OR yang dibalikkan sehingga dapat dikatakan bahwa gerbang NOR akan menghasilkan sinyal keluaran tinggi jika semua sinyal masukannya bernilai rendah. Gerbang Logika NOR pada Datasheet nama lainnya IC TTL 7402. Simbol gerbang NOR ditunjukkan pada Gambar 2.6 Tabel kebenaran diperlihatkan pada Tabel 2.6.

(a) Simbol (b) Persamaan Logika

g. Gerbang X-NOR (EXNOR GATE)

Gerbang X-NOR akan menghasilkan sinyal keluaran tinggi jika semua sinyal masukan bernilai sama (kebalikan dari gerbang X-OR). Gerbang Logika X-NOR pada Datasheet nama lainnya IC TTL 74266. Simbol gerbang X-NOR ditunjukkan pada Gambar 2.7 Tabel kebenaran diperlihatkan pada Tabel 2.7.

(a) Simbol (b) Persamaan Logika Gambar 2.7 Gerbang X-NOR

Tabel 2.7 Tabel Kebenaran Gerbang X-NOR

BAB II HASIL DATA 1. Hasil Tabel Kebenaran Gerbang AND dan NAND

INPUT OUTPUT

Gambar 2.1.1 Hasil gerbang AND dan NAND ke 1

Gambar 2.1.2 Hasil gerbang AND dan NAND ke 2

Gambar 2.1.4 Hasil gerbang AND dan NAND ke 4

Gambar 2.1.5 Hasil gerbang AND dan NAND ke 5

Gambar 2.1.7 Hasil gerbang AND dan NAND ke 7

Gambar 2.1.8 Hasil gerbang AND dan NAND ke 8

Gambar 2.1.9 Hasil gerbang AND dan NAND ke 9

Gambar 2.1.11 Hasil gerbang AND dan NAND ke 11

Gambar 2.1.12 Hasil gerbang AND dan NAND ke 12

Gambar 2.1.13 Hasil gerbang AND dan NAND ke 13

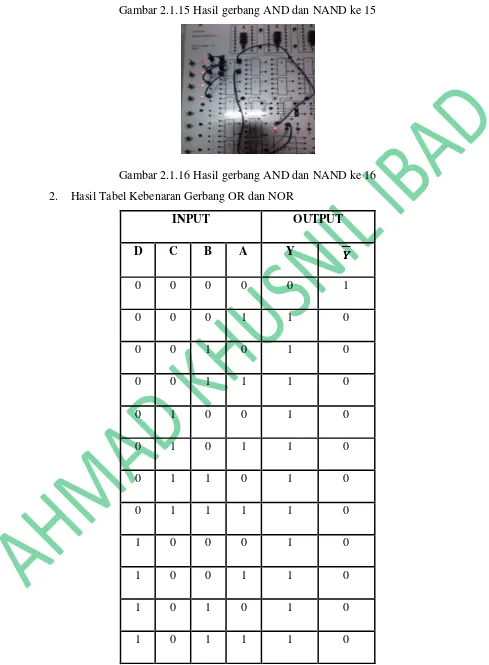

Gambar 2.1.15 Hasil gerbang AND dan NAND ke 15

Gambar 2.1.16 Hasil gerbang AND dan NAND ke 16 2. Hasil Tabel Kebenaran Gerbang OR dan NOR

INPUT OUTPUT

D C B A Y __𝒀

0 0 0 0 0 1

0 0 0 1 1 0

0 0 1 0 1 0

0 0 1 1 1 0

0 1 0 0 1 0

0 1 0 1 1 0

0 1 1 0 1 0

0 1 1 1 1 0

1 0 0 0 1 0

1 0 0 1 1 0

1 0 1 0 1 0

1 1 0 0 1 0

1 1 0 1 1 0

1 1 1 0 1 0

1 1 1 1 1 0

Hasil uji coba gerbang OR dan NOR

Gambar 2.2.1 Hasil gerbang OR dan NOR ke 1

Gambar 2.2.3 Hasil gerbang OR dan NOR ke 3

Gambar 2.2.4 Hasil gerbang OR dan NOR ke 4

Gambar 2.2.5 Hasil gerbang OR dan NOR ke 5

Gambar 2.2.7 Hasil gerbang OR dan NOR ke 7

Gambar 2.2.8 Hasil gerbang OR dan NOR ke 8

Gambar 2.2.9 Hasil gerbang OR dan NOR ke 9

Gambar 2.2.11 Hasil gerbang OR dan NOR ke 11

Gambar 2.2.12 Hasil gerbang OR dan NOR ke 12

Gambar 2.2.13 Hasil gerbang OR dan NOR ke 13

Gambar 2.2.15 Hasil gerbang OR dan NOR ke 15

Gambar 2.2.16 Hasil gerbang OR dan NOR ke 16 3. Hasil Tabel Kebenaran dari Aljabar Boole

C B A Y

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 0

1 0 1 1

1 1 0 0

1 1 1 0

Hasil uji coba Aljabar Boole diatas

Gambar 2.3.1 Hasil Aljabar Boole ke 1

Gambar 2.3.2 Hasil Aljabar Boole ke 2

Gambar 2.3.4 Hasil Aljabar Boole ke 4

Gambar 2.3.5 Hasil Aljabar Boole ke 5

Gambar 2.3.6 Hasil Aljabar Boole ke 6

Gambar 2.3.8 Hasil Aljabar Boole ke 8

4. Hasil Tabel Kebenaran dan Persamaan Aljabar Boole dari Rangkaian Half Adder

Y X Sum Carry

0 0 0 0

0 1 1 0

1 0 1 0

1 1 0 1

Hasil uji coba rangkaian Half Adder

Gambar 2.4.2 Hasil rangkaian Half Adder ke 2

Gambar 2.4.3 Hasil rangkaian Half Adder ke 3

Gambar 2.4.4 Hasil rangkaian Half Adder ke 4 5. Hasil Tabel Kebenaran Gerbang OR dari IC 7400 (NAND 2 Input)

B A Y

0 0 0

0 1 1

1 1 1

Hasil uji coba gerbang OR dari IC 7400 (NAND 2 Input)

Gambar 2.5.1 Hasil gerbang OR dari IC 7400 ke 1

Gambar 2.5.2 Hasil gerbang OR dari IC 7400 ke 2

Gambar 2.5.4 Hasil gerbang OR dari IC 7400 ke 4 6. Hasil Tabel Kebenaran Gerbang EX-OR dari IC 7400 (NAND 2 Input)

B A Y

0 0 0

0 1 1

1 0 1

1 1 0

Hasil uji coba gerbang EX-OR dari IC 7400 (NAND 2 Input)

Gambar 2.6.2 Hasil gerbang EX-OR dari IC 7400 ke 2

Gambar 2.6.3 Hasil gerbang EX-OR dari IC 7400 ke 3

BAB III

ANALISA DAN PEMBAHASAN

Pada praktikum modul satu ini membahasa tentang rangkaian gerbang logika. Praktikum kali ini dengan menggunakan Digital Experimenter dan sebagai penyambungnya adalah Kabel Conector. Rangkaian logika terbentuk dari hubungan beberapa gerbang (gate) logika. Rangkaian logika bekerja secara digital. Output dari

suatu rangkaian logika ditentukan oleh karakterisitik dan hubungan dari

gerbang-gerbang yang digunakan.

Gerbang logika atau gerbang logik adalah suatu entitas dalam elektronika dan matematika boolean yang mengubah satu atau beberapa masukan logik menjadi sebuah sinyal keluaran logik. Gerbang logika terutama diimplementasikan secara elektronis menggunakan transistor atau dioda, akan tetapi dapat dibangun dengan menggunakan susunan komponen-komponen yang memanfaatkan sifat-sifat elektromagnetik. Logika merupakan dasar dari semua penalaran. Untuk menyatukan beberapa logika, di membutuhkan operator logika dan untuk membuktikan kebenaran dari logika, dapat menggunakan tabel kebenaran. Tabel kebenaran dapat menampilkan hubungan antara nilai kebenaran dari proposisi atomik. Dengan tabel kebenaran tersebut, suatu persamaan logika atau proposisi bisa dicari nilai kebenarannya. Tabel kebenaran ini mempunyai banyak aplikasi yang dapat diterapkan. Salah satu dari aplikasi tersebut yaitu dapat mendesain suatu rangkaian logika.

sistem yang mempresentasikan sinyal sebagai nilai diskrit. Dalam sebuah sirkuit digital,sinyal direpresentasikan dengan satu dari dua macam kondisi yaitu 1 (high) dan 0 (low).

Uji coba yang pertama yaitu gerbang AND dan NAND. Gerbang AND merupakan salah satu gerbang logika dasar yang memiliki 2 buah saluran masukan (input) atau lebih dan sebuah saluran keluaran (output). Gerbang AND akan menghasilkan sebuah keluaran biner tergantung dari kondisi masukan dan fungsinya. Output gerbang AND akan tinggi hanya jika semua input tinggi, dan jika salah satu atau lebih input berlogika rendah maka output akan rendah. Prinsip kerja dari gerbang AND adalah kondisi keluaran (output) akan berlogik 1 bila semua saluran masukan (input) berlogic 1. Selain itu output akan berlogik 0. Persamaan logika aljabar Boole gerbang AND adalah Y=A.B. Pada Aljabar Boole operasi gerbang AND diberi tanda ”kali” atau tanda ”titik”. Gerbang NAND merupakan kombinasi dari gerbang AND dengan gerbang NOT dimana keluaran gerbang AND dihubungkan ke saluran masukan dari gerbang NOT. Output akan berlogika tinggi jika salah satu atau lebih input-nya berlogika rendah, dan output akan berlogika rendah hanya pada saat semua input-nya berlogika tinggi. NAND keluaran dari gerbang AND di”NOT”kan maka prinsip kerja dari gerbang NAND merupakan kebalikan dari gerbang AND. Outputnya merupakan komplemen atau kebalikan dari gerbang AND, yakni memberikan keadaan level logik 0 pada outputnya jika dan hanya jika keadaan semua inputnya berlogika 1. Persamaan logika aljabar Boole untuk output gerbang NAND adalah Y= A . B.

Pada Gerbang NOR adalah gabungan dari gerbang OR dan NOT. Output gerbang NOR selalu kebalikan dari output gerbang OR untuk input yang sama. Output akan berlogika rendah apabila salah satu atau lebih inputnya berlogika tinggi, dan pada output akan berlogika tinggi hanya pada saat semua input berlogika rendah. Outputnya merupakan komplemen atau kebalikan dari gerbang OR, yakni memberikan keadaan level logik 0 pada outputnya jika salah satu atau lebih inputnya berlogika 1.Persamaan logika aljabar Boole untuk output gerbang NOR adalah Y = A + B. Uji coba yang ketiga membuat tabel kebenaran dari rangkaian aljabar boole. Inputannya berjumlah tiga A,B dan C untuk menghasilkan satu output yaitu Y. pada rangkaian aljabar boole tersebut menggunakan gerbang AND, OR, dan NOT. Gerbang NOT JUGA sering disebut dengan gerbang inverter. Gerbang ini merupakan gerbang logika yang paling mudah diingat. Gerbang NOT memiliki satu saluran masukan dan satu buah saluran keluaran. Output gerbang NOT selalu merupakan kebalikan dari input-nya. Bila pada saluran masukannya berlogik 1 maka pada saluran keluarannya akan berlogik 0 dan sebaliknya. Persamaan logika aljabar Boole untuk output gerbang NOT yaitu Y = A.

Tabel kebenaran pada persamaan aljabar boole dari rangkaian half adder

merupakan uji coba selanjutnya yaitu uji coba ke empat. Rangkaian Half adder

adalah suatu rangkaian penjumlah sistem bilangan biner yang paling sederhana atau rangkaian elektronik yang bekerja melakukan perhitungan penjumlahan dari dua buah bilangan binary, yang masing-masing terdiri dari satu bit. Rangkaian ini memiliki dua input dan dua buah output, salah satu outputnya dipakai sebagai tempat nilai pindahan dan yang lain sebagai hasil dari penjumlahan. Rangkaian ini hanya dapat digunakan untuk operasi penjumlahan data bilangan biner sampai 1 bit saja. Rangkaian half adder mempunyai 2 masukan dan keluaran yaitu Summary out (Sum) dan Carry out (Carry). Persamaan logika rangkaian half adder pada summary

BAB IV

KESIMPULAN DAN SARAN A. KESIMPULAN

1. Rangkaian digital adalah sistem yang mempresentasikan sinyal sebagai nilai diskrit.

2. Gerbang atau gate ini merupakan elemen dasar dari semua rangkaian yang menggunakan sistem digital

3. Suatu entitas dalam elektronika dan matematika boolean yang mengubah satu atau beberapa masukan logik menjadi sebuah sinyal keluaran logik merupakan gerbang logika.

4. Rangkaian Half adder adalah suatu rangkaian penjumlah sistem bilangan biner yang paling sederhana atau rangkaian elektronik yang bekerja melakukan perhitungan penjumlahan dari dua buah bilangan binary, yang masing-masing terdiri dari satu bit.

B. SARAN

1. Berdoa sebelum atau setelah selesai melakukan praktikum.

2. Sebelum melakukan praktikum persiapkan alat dan bahan yang akan dibutuhkan saat praktikum.

BAB V

DAFTAR PUSTAKA

Anonymous. (tahun). Landasan Teori. http://repository.usu.ac.id/bitstream/12345 6789/20664/4/Chapter%20II.pdf. 27 April 2015 (00:57).

Anonymous. (tahun). Rangkaian-Rangkaian Aritmetik. http://staff.uny.ac.id/sites /default/files/Rang%20Aritmetik.pdf. 28 April 2015 (09:57).

Asror, Mustaghfiri . (2014). Teori Gerbang Logika. https://www.scribd.com/doc/ 227789835/teori-gerbang-logika. 27 April 2015 (00:57).

Ningsih, Elsa Yuli. (2012). 1 Gerbang Logika. https://www.scribd.com/doc/ 98829771/1-Gerbang-Logika-Dasar. 27 April 2015 (00:32).

LAPORAN PRAKTIKUM

TEKNIK DIGITAL

MODUL II : PENCACAH (COUNTER)

DISUSUN OLEH : Ahmad Khusnil Ibad

14101080

PARTNER PRAKTIKUM :

1. Lukman Fadhil Rizky .K (14101097) 2. Yusuf Budi Setyoso (14101117)

Tanggal Praktikum : 04 Mei 2015

Asisten Praktikum : 1. Farah Izzah Fida Afifah 2. Lintang Setyo Palupi 3. Yusuf Ramli

LABORATORIUM

TEKNIK ELEKTRONIKA DAN TEKNIK DIGITAL SEKOLAH TINGGI TEKNOLOGI TELEMATIKA TELKOM

BAB I

KONFIGURASI SISTEM

Pencacah atau Counter merupakan jenis khusus dari register, yang dirancang guna mencacah/menghitung jumlah pulsa-pulsa detak yang tiba pada masukan-masukannya. Peranti ini terdiri dari satu atau lebih flip-flop yang dirangkai sedemikian rupa sehingga setiap pulsa masukan akan menambah cacahan. Pencacah dibedakan menjadi dua yaitu : pencacah sinkron dan pencacah tak sinkron. Perbedaan mendasar dari kedua jenis pencacah atau counter ini terletak pada cara memberikan sinyal detak pada tiap flip-flopnya. Karakteristik penting dari pencacah adalah Kerjanya sinkron atau tak sinkron, mencacah maju atau mundur, sampai beberapa banyak dapat mencacah (modulo pencacah).

Pencacah sinkron atau synchronous counter, yang beroperasi serentak dengan pulsa clock yang kadang-kadang disebut juga dengan pencacah deret atau series counter atau pencacah jajar. Pencacah sinkron adalah pencacah yang sinyal detaknya diberikan secara serentak (pararel) pada masing-masing input flip-flop.

Gambar 1. 1 Pencacah Sinkron 4 bit

Pencacah tak sinkron atau erial counter adalah pencacah yang pemberian sinyal detaknya secara seri artinya sinyal detak dihubungkan pada input flip-flop LSB (Less Significant Bit), sedangkan untuk flip-flop berikutnya diberikan oleh output flip-flop sebelumnya.

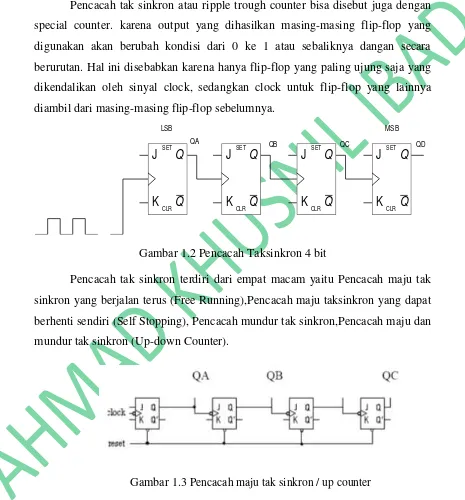

Pencacah tak sinkron atau ripple trough counter bisa disebut juga dengan special counter. karena output yang dihasilkan masing-masing flip-flop yang digunakan akan berubah kondisi dari 0 ke 1 atau sebaliknya dangan secara berurutan. Hal ini disebabkan karena hanya flip-flop yang paling ujung saja yang dikendalikan oleh sinyal clock, sedangkan clock untuk flip-flop yang lainnya diambil dari masing-masing flip-flop sebelumnya.

J

Gambar 1.2 Pencacah Taksinkron 4 bit

Pencacah tak sinkron terdiri dari empat macam yaitu Pencacah maju tak sinkron yang berjalan terus (Free Running),Pencacah maju taksinkron yang dapat berhenti sendiri (Self Stopping), Pencacah mundur tak sinkron,Pencacah maju dan mundur tak sinkron (Up-down Counter).

Gambar 1.3 Pencacah maju tak sinkron / up counter

Dasar dari gambar 1.3 rangkaian pencacah itu adalah T-Flip Flop. Bahwa

flip-flop yang pertama adalah flip-flip-flop yang dikendalikan oleh sinyal clock. Umpamakan

clock untuk B, begitu seterusnya sehingga output C (QC) yang akan menjadi sinyal

Gambar 2.1.1 Rangkaian Pencacahan sinkron modulo-8

Gambar 2.1.2 Hasil pencacahan sinkron biner modulo-8 ke 0

Gambar 2.1.3 Hasil pencacahan sinkron biner modulo-8 ke 1

Gambar 2.1.4 Hasil pencacahan sinkron biner modulo-8 ke 2

Gambar 2.1.6 Hasil pencacahan sinkron biner modulo-8 ke 4

Gambar 2.1.7 Hasil pencacahan sinkron biner modulo-8 ke 5

Gambar 2.1.8 Hasil pencacahan sinkron biner modulo-8 ke 6

Gambar 2.1.9 Hasil pencacahan sinkron biner modulo-8 ke 7

Gambar 2.1.11 Hasil pencacahan sinkron biner modulo-8 ke 9

Gambar 2.1.12 Hasil pencacahan sinkron biner modulo-8 ke 10 b. Pencacahan biner modulo-6

Tabel Kebenaran 2.1.2

Pulsa Klok Ke-

Keluaran

Qc Qb Qa

0 0 0 0

1 1 0 0

2 0 1 0

3 1 1 0

4 0 0 1

5 1 0 1

6 0 0 0

Gambar 2.1.13 Rangkaian Pencacahan sinkron modulo-6

Gambar 2.1.14 Hasil pencacahan sinkron biner modulo-6 ke 0

Gambar 2.1.15 Hasil pencacahan sinkron biner modulo-6 ke 1

Gambar 2.1.17 Hasil pencacahan sinkron biner modulo-6 ke 3

Gambar 2.1.18 Hasil pencacahan sinkron biner modulo-6 ke 4

Gambar 2.1.19 Hasil pencacahan sinkron biner modulo-6 ke 5

Gambar 2.1.21Hasil pencacahan sinkron biner modulo-6 ke 7 c. Pencacahan BCD (Binary Code Decimal)

Gambar 2.1.22 Rangkaian Pencacahan BCD (Binary Code Decimal)

Gambar 2.1.23 Hasil pencacahan BCD (Binary Code Decimal) ke 0

Gambar 2.1.24 Hasil pencacahan BCD (Binary Code Decimal) ke 1

Gambar 2.1.25 Hasil pencacahan BCD (Binary Code Decimal) ke 2

Gambar 2.1.27 Hasil pencacahan BCD (Binary Code Decimal) ke 4

Gambar 2.1.28 Hasil pencacahan BCD (Binary Code Decimal) ke 5

Gambar 2.1.29 Hasil pencacahan BCD (Binary Code Decimal) ke 6

Gambar 2.1.30 Hasil pencacahan BCD (Binary Code Decimal) ke 7

Gambar 2.1.32 Hasil pencacahan BCD (Binary Code Decimal) ke 9

Gambar 2.1.33 Hasil pencacahan BCD (Binary Code Decimal) ke 10

Gambar 2.1.34 Hasil pencacahan BCD (Binary Code Decimal) ke 11 8. Pencacahan Tak Sinkron

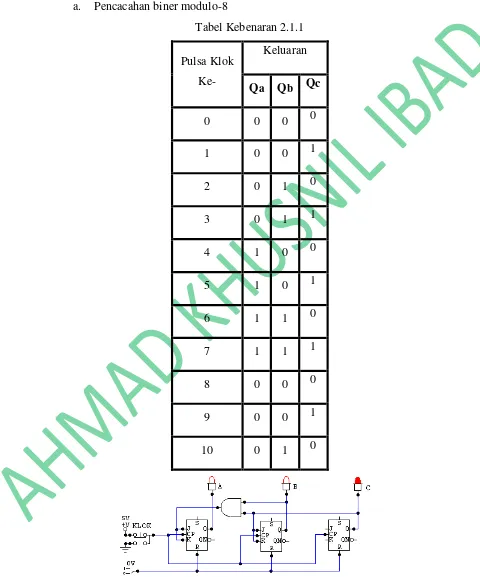

a. Pencacahan biner modulo-8

Tabel Kebenaran 2.2.1

Pulsa Klok Ke-

Keluaran

Qc Qb Qa

0 0 0 0

2 0 1 0

3 1 1 0

4 0 0 1

5 1 0 1

6 0 1 1

7 1 1 1

8 0 0 0

9 1 0 0

10 0 1 0

Gambar 2.2.1 Rangkaian Pencacahan tak sinkron modulo-8

Gambar 2.2.3 Hasil pencacahan tak sinkron biner modulo-8 ke1

Gambar 2.2.4 Hasil pencacahan tak sinkron biner modulo-8 ke 2

Gambar 2.2.5 Hasil pencacahan tak sinkron biner modulo-8 ke 3

Gambar 2.2.7 Hasil pencacahan tak sinkron biner modulo-8 ke 5

Gambar 2.2.8 Hasil pencacahan tak sinkron biner modulo-8 ke 6

Gambar 2.2.9 Hasil pencacahan tak sinkron biner modulo-8 ke 7

Gambar 2.2.11 Hasil pencacahan tak sinkron biner modulo-8ke 9

Gambar 2.2.12 Hasil pencacahan tak sinkron biner modulo-8 ke 10 b. Pencacahan biner modulo-6

Tabel Kebenaran 2.2.2

Pulsa Klok Ke-

Keluaran

Qc Qb Qa

0 0 0 0

1 1 0 0

2 0 1 0

3 1 1 0

4 0 0 1

6 0 0 0

7 1 0 0

8 0 1 0

Gambar 2.2.13 Rangkaian Pencacahan tak sinkron modulo-6 c. Pencacahan BCD (Binary Code Decimal)

8 0 0 0 1

9 1 0 0 1

10 0 0 0 0

11 1 0 0 0

BAB III

ANALISA DAN PEMBAHASAN

Modul dua ini kita praktikum tentang Pencacahan (counter). Pada pencacahan ini kita praktik pencacahan sinkron dan pencacahan tak sinkron.

Counter atau pencacahan ini merupakan sekumpulan FF yang berubah keadaan keluarannya dalam erespon pulsa-pulsa yang diberikan pada masukannya. Susunan beberapa FF tersebut menghasilkan bilangan biner ekivalen dari jumlah pulsa total yang diberikan pada saat itu. Pencacah banyak digunakan pada sistem digital, diantaranya sebagai penghitung pulsa, pembagi frekuensi, pewaktu, penunda waktu dan sebagainya. Berdasarkan Clock yang diberikan pada FF.

Pencacahan dibagi menjadi dua yaitu Pencacah tak sinkron atau tidak serempak (Asynchronous) dan sinkron atau serempak (Synchronous). Dua pencacahan tersebut sesuai dengan yang telah kita praktikkan sebelumnya. Pada sinkron atau serempak dibagi lagi menjadi tiga sesuai yang kita praktikkan. Pencacahan sinkron yang pertama adalah Pencacah biner modulo-8, yang kedua yaitu pencacahan sinkron biner modulo-6 dan pencacahan sinkron yang terkhir dipraktikan adalah Pencacah BCD (Binary Code Decimal).

Pencacah sinkron (synchronous), yang beroperasi serentak dengan pulsa clock

yang kadang-kadang disebut juga dengan pencacah deret atau series counter atau juga

pencacah jajar. Pencacah sinkron atau kata serempak (Synchronous) merupakan pencacah yang sinyal detaknya diberikan secara serentak (pararel) pada masing-masing input atau masukan flip-flop.

Pada pencacah biner modulo-8 itu termasuk kedalam pencacah sinkron (synchronous). Pada uji coba pencacah sinkron (synchronous) yang kita lakukan

pertama adalah pencacahan biner modulo-8. Uji coba yang dilakukan kita

munggunakan Digital Experimenter dengan penghubung-pengubungnya adalah Kabel

Conector. Uji coba pencacah biner modulo-8 itu benar jika kita menekan klok delapan

kali maka output atau lampu akan mati semua atau lamupu tidak nyala pada digital

experimenter. Seperti pada bab ke 2 hasil data gambar 2.1.10 Hasil pencacahan sinkron

biner modulo-8 ke 8. Pada gambar uji coba tersebut output bernilai 0 pada output a, 0

pada output b, dan 0 pada output c. pencacah biner modulo-8 outputnya bernilai 0

semua karena nilai tertingginya adalah biner delapan, jika lebih akan kembali lagi

pada a, output 0 pada b dan output 1 pada c. seperti pada biner satu. Pencacahan ini

yaitu pencacah biner modulo-8 hanya memiliki 3 (tiga) bit saja.

Jika pada pencacah biner modulo-8 outputnya bernilai 0 semua atau lampu

tidak nyala pada biner ke 8. Sedangkan pada praktikum selanjutnya adalah pencacahan

biner modulo-6, kali ini beda dengan modulo-8. Modulo-6 ini output bernilai 0 (nol)

semua atau lampu tidak nyala semua pada biner 6 (enam). Seperti pada bab dua hasil

data pada gambar 2.1.20 Hasil pencacahan sinkron biner modulo-6 ke 6. Sebab nilai pencacah biner modulo-6 ini biner tertingginya adalah biner 6 (enam) jika lebih maka

akan kembali ke biner pertama atau ke satu. Seperti pada gambar 2.1.21 Hasil pencacahan sinkron biner modulo-6 ke 7 di bab 2 hasil data. Pada gambar tersebut terlihat lampu outputnya hanya nyala 1 (satu) pada output c sehingga binernya 0,0,1 seperti pada biner 1 (satu). Pencacah modulo-6 ini termasuk dalam pencacah sinkron.

Pencacahan BCD (Binary Code Decimal) merupakan praktik selanjutnya setelah kita praktikkan pencacah biner modulo-6. Binary Code Decimal (BCD) adalah sebuah sistem sandi yang umum digunakan untuk menyatakan angka desimal

secara digital. BCD adalah sistem pengkodean bilangan desimal yang metodenya mirip

dengan bilangan biner biasa, hanya saja dalam proses konversi, setiap simbol dari

bilangan desimal dikonversi satu per satu, bukan secara keseluruhan seperti konversi

bilangan desimal ke biner biasa. BCD ( Binary Coded Decimal ) merupakan kode biner

yang digunakan hanya untuk mewakili nilai digit desimal saja, yaitu nilai angka 0

sampai dengan 9. BCD menggunakan kombinasi dari 4 bit, sehingga sebanyak 16

(24=16) kemungkinan kombinasi yang bisa diperoleh dan hanya 10 kombinasi yang

dipergunakan. Kode BCD yang orisinil sudah jarang dipergunakan untuk komputer

generasi sekarang, karena tidak dapat mewakili huruf atau simbol-simbol karakter

khusus. BCD dipergunakan untuk komputer generasi pertama.

Pencacahan BCD (Binary Code Decimal) termasuk dalam pencacah sinkron.

pada pecacah yang telah kita lakukan didapatkan hasilnya output bernilai 0 semua pada

biner 10 (sepuluh). Seperti pada gambar 2.1.33 Hasil pencacahan BCD (Binary Code

Decimal) ke 10 di bab dua hasil data, gambar tersebut lampu pada output tidak nyala

semua. Karena biner 10 nilai tertinggi pada pencacah BCD. Dan pada biner ke sebelas

Pencacah tak sinkron (asynchronous counter), yang beroperasi tidak serentak dengan pulsa clock atau pencacah kerut atau ripple counter. Pencacah

asynchronous atau pencacah tak sinkron ini merupakan praktik yang selanjutnya setelah pencacah sinkron. Pencacah tak sinkron (asynchronous counter) adalah pencacah yang pemberian sinyal detaknya secara seri artinya sinyal detak dihubungkan pada input flip-flop LSB (Less Significant Bit), sedangkan untuk flip-flop berikutnya diberikan oleh output flip-flip-flop sebelumnya.Pencacah tak sinkron output yang dihasilkan masing-masing flip-flop yang digunakan akan berubah kondisi dari 0 ke 1 atau sebaliknya dangan secara berurutan. Hal ini disebabkan karena hanya flip-flop yang paling ujung saja yang dikendalikan oleh sinyal clock, sedangkan clock untuk flip-flop yang lainnya diambil dari masing-masing flip-flop sebelumnya. Pada uji coba kali ini juga munggunakan Digital Experimenter dengan penghubung-pengubungnya adalah Kabel Conector.

Pada praktikum tak sinkron kita disuruh praktikum tiga pencacah yaitu

pencacah biner modulo-8, pencacah biner modulo-6 dan pencacah BCD. Namun hanya

praktikum satu pencacah yaitu pencach biner modulo-8. Ternyata hasilnya sama

dengan pencacah modulo-8 yang pencacah sinkron sehingga kita dapat simpulkan

pencacah modulo-8, pencacah modulo-6 dan pencacah BCD pada pencacah tak sinkron

sama dengan pencacah modulo-8, pencacah modulo-6 dan pencacah BCD pada

pencacah sinkron. hanya beda pada rangkaian kalau pada pencacah tak sinkron tidak

menggunakan penghubung gerbang AND sedangkan pada pencacah sinkron

sebaliknya yaitu menggunakan gerbang AND. Bisa dibedakan dengan melihat gambar

2.2.1 Rangkaian Pencacahan tak sinkron modulo-8 dengan gambar 2.1.1 Rangkaian

BAB IV

KESIMPULAN DAN SARAN C. KESIMPULAN

5. Counter atau pencacahan merupakan sekumpulan FF yang berubah keadaan keluarannya dalam erespon pulsa-pulsa yang diberikan pada masukannya.

6. Pencacah sinkron (synchronous) beroperasi serentak dengan pulsa clock. 7. Pencacah tak sinkron (asynchronous counter) beroperasi tidak serentak

dengan pulsa clock. Pencacah tak sinkron (asynchronous counter) adalah pencacah yang pemberian sinyal detaknya secara seri artinya sinyal detak dihubungkan pada input flip-flop LSB (Less Significant Bit), sedangkan untuk flip-flop berikutnya diberikan oleh output flip-flop sebelumnya 8. Pencacah biner modulo-8, pencacah biner modulo-6 dan pencacah BCD pada

pencacah tak sinkron sama dengan pencacah biner modulo-8, pencacah biner

modulo-6 dan pencacah BCD pada pencacah sinkron itu hasilnya sama. hanya

beda pada rangkaian kalau pada pencacah tak sinkron tidak menggunakan

penghubung gerbang AND sedangkan pada pencacah sinkron sebaliknya

yaitu menggunakan gerbang AND

D. SARAN

5. Berdoa sebelum atau setelah selesai melakukan praktikum.

6. Sebelum melakukan praktikum persiapkan alat dan bahan yang akan dibutuhkan saat praktikum.

BAB V

DAFTAR PUSTAKA

Amal. (2014). Binary Code Decimal. https://www.scribd.com/doc/222652683 /Binary-Code-Decimal-1ccW. 8 Mei 2015 (00:57).

Anonymous. (tahun). Counter. http://staff.unila.ac.id/junaidi/files/2013/06/COUN TE .pdf. 5 Mei 2015 (19 :57).

Anonymous. (tahun). Pencacah Dua Desimal. http://unhas.ac.id/tahir/BAHAN-KULIAH/PSD/MATERI-PSD/sp-psd-2004/Tugas_PSD_Nurwijayanto_D41

101777-2/Pencacah_2_Desimal_NURWIJAYANTO_D41101777-2.doc. 6 Mei 2015 (19:00).

Anonymous. (2014). Modul Counter Sinkron. https://www.scribd.com/doc/ 249462550/Modul-Counter-Sinkron. 5 Mei 2015 (22:32).

LAPORAN PRAKTIKUM

1. Lukman Fadhil Rizky .K (14101097) 2. Yusuf Budi Setyoso (14101117)

PraktikumTanggal : 13 Mei 2015

Asisten Praktikum : 1. Farah Izzah Fida Afifah 2. Lintang Setyo Palupi 3. Yusuf Ramli

LABORATORIUM

TEKNIK ELEKTRONIKA DAN TEKNIK DIGITAL

SEKOLAH TINGGI TEKNOLOGI TELEMATIKA TELKOM JL. DI. PANJAITAN 128 PURWOKERTO

BAB I

KONFIGURASI SISTEM

Register adalah kumpulan beberapa Flip-Flop yang digunakan untuk menyimpan data biner, tiap Flip-Flop dapat menyimpan data biner 1 bit. Pengisian Register berarti me-set atau me-reset masing-masing FF sehingga sesuai dengan bit data yang disimpan. Semakin panjang data biner yang disimpan oleh register, maka jumlah Flip-Flopnya juga semakin banyak. Register akan menyimpan data baru jika ada data baru diberikan pada masukan dan Clock register diaktifkan.

Ada dua cara untuk menyimpan atau mengambil data pada Register, yaitu bit per bit secara berurutan dengan sinkronisasi sebuah pulsa Clock, yang dinamakan serial dan beberapa bit secara serentak / paralel. Ada beberapa macam

register antara lain :

1. Register penampung merupakan register kerjanya hanya sebagai penyimpan sementara biner. Rangkaian ini primitif, yang diperlukan adalah pengendalian dari bit itu sendiri sampai siap untuk disimpan .

Gambar 1.1.1 Register penampung

Register penampung terkendali jika CLR menjadi tinggi maka semua flip – flop atau FF meriset serta kata keluaran menjadi q = 0000, ketika CLR rendah maka register siap bekerja.

2. Shift Register (register geser) adalah suatu register dimana informasi dapat bergeser (digeserkan). Dalam register geser flip-flop saling dikoneksi, sehingga isinya dapat digeserkan dari satu flipflop ke flip-flop yang lain, kekiri atau kekanan atas perintah denyut lonceng (Clock). Dalam alat ukur digit, register dipakai untuk mengingat data yang sedang ditampilkan. Ada 4 Shift Register yaitu:

a. Register SISO (Serial In Serial Out)

Register geser SISO menerima data secara serial, bit-per-bit. Selanjutnya mengeluarkan data tersebut secara serial pula, bit-per-bit setiap satu pulsa clock. Register geser SISO 4-bit yang dibangun dari 4 buah flip-flop D. Dapat menyimpan data sampai 4-bit, yang sekaligus menunjukkan kapasitas simpan, yaitu 4-bit.

Gambar 1.2.1 Rangkaian Register SISO.

b.

Register SIPO (Serial In Paralel Out)

Gambar 1.2.2 Rangkaian RegisterSIPO.

c. Register PISO (Paralel In Serial Out)

Pada register geser jenis PISO (Paralel-In-Serial-Out), bit-bit data dimasukkan secara pararel kedalam masing-masing flip-flop yang bersesuaian, selanjutnya data dikeluarkan secara serial bit-per-bit setiap satu pulsa clock. Gambar register geser PISO 4bit dengan 4 jalur masukan data, 1 jalur clock dan 1 jalur masukan untuk shift atau load.

12.Gambar 2.11 Rangkaian Register PISO. Gambar 1.2.3 Rangkaian RegisterPISO

d.

Register PIPO (Paralel In Paralel Out)

BAB II HASIL DATA 9. Register SISO (Serial Input – Serial Output)

Gambar 2.1.1 Rangkaian register

Tabel Kebenaran 2.1.1 Register SISO (Serial Input – Serial Output)

19 0 0 0 0 0 1

20 0 0 0 0 0 0

Gambar 2.1.2 Hasil Register SISO (Serial Input – Serial Output) klok 1 10. Register PIPO (Paralel Input – Paralel Output)

Tabel Kebenaran 2.2.1 Register PIPO (Paralel Input – Paralel Output)

INPUT PARALEL OUTPUT REGISTER E5 E4 E3 E2 E1 Q5 Q4 Q3 Q2 Q1

1 1 1 0 0 1 1 1 0 0

1 1 1 1 1 1 1 1 1 1

1 0 1 0 1 1 0 1 0 1

1 1 0 0 1 1 1 0 0 1

1 0 0 0 1 1 0 0 0 1

1 0 0 1 1 1 0 0 1 1

11. Register PISO (Paralel Input – Serial Output)

Tabel Kebenaran 2.3.1 Register PISO (Paralel Input – Serial Output)

KLOK INPUT PARALEL OUTPUT REGISTER E5 E4 E3 E2 E1 Q5 Q4 Q3 Q2 Q1

Gambar 2.3.1 Hasil Register PISO (Paralel Input – Serial Output) klok 0 12. Register SIPO (Serial Input – Paralel Output)

Tabel Kebenaran 2.4.1 Register SIPO (Serial Input – Paralel Output)

KLOK INPUT

SERIAL OE

- 0 0 1 0 1 0 1 0 0 0 0 0

0 1 0 0 0 0 0 0 0 0 0 0 0

1 0 0 0 0 0 0 0 0 0 0 0 0

2 1 0 1 0 1 0 1 0 0 0 0 0

3 0 0 0 1 0 1 0 0 0 0 0 0

4 1 0 1 0 1 0 1 0 0 0 0 0

5 0 0 0 1 0 1 0 0 0 0 0 0

- 1 0 0 1 0 1 0 0 0 0 0 0

BAB III

ANALISA DAN PEMBAHASAN

Register merupakan materi yang dipraktikan pada modul yang ketiga. Kumpulan beberapa Flip-Flop yang digunakan untuk menyimpan data biner, tiap Flip-Flop dapat menyimpan data biner 1 bit merupakan register. Register adalah suatu rangkaian logika yang berfungsi untuk menyimpan data yang berupa 1 (satu) atau beberapa flip-flop yang digabungkan menjadi 1 (satu). Alat yang digunakan pada praktikum register sama seperti yang digunakan pada praktikum Rangkaian Gerbang Logika dan Pencacah (Counter) yaitu Digital Experimenter dan Kabel Conector.

Pada praktikum Register kita menggunakan tombol dan gerbang logika lebih banyak pada digital experimenter. Bisa kita lihat pada gambar 2.1.1 Rangkaian register di bab dua. Seperti menggunakan gerbang NAND, Gerbang NOT dan gerbang AND. Kita juga menggunakan Sinyal Kontrol yaitu S : Aktivasi masukan paralel (Aktive Low), R : RESET (Aktive Low), T : Input sinyal pulsa / klok, OE : Aktivasi keluaran paralel (Aktive Low) pada Input (masukan) menggunakan E1 – E5 (data paralel), SE (data serial). Pada Output (keluaran) menggunakan Q1–Q5 (Output Flip-flop), O1-O5 (Output Register) dan pada praktikum register juga menggunakan sinyal clock T. sinyal clock T ini berfungsi untuk menggeser data masukan serial.

Sebuah register terdiri dari sekelompok atau kumpulan flip-flop atau FF. Setiap flip-flop mampu menyimpan 1 (satu) bit informasi. Sebuah n-bit register berisi sekelompok n flip-flop atau FF yang dapat mampu menyimpan n bit informasi biner. Selain flip-flop, register mempunyai gerbang-gerbang kombinasional yang melakukan tugas pemrosesan data-data tertentu.

Register pada arti yang lebih luas, sebuah register terdiri dari sekelompok flip-flop dan gate (gerbang) yang bisa mempengaruhi transisinya. Flip-flip-flop atau FF memegang informasi biner dan gerbang (gate) menentukan bagaimana informasi ditransfer ke dalam register tersebut.

pengendalian dari bit itu sendiri sampai siap untuk disimpan. Sedangkan pada Shift Register (register geser) adalah suatu register dimana informasi dapat bergeser (digeserkan). Dalam register geser flip-flop saling dikoneksi, sehingga isinya dapat digeserkan dari satu flip-flop (FF) ke flip-flop (FF) yang lain, kekiri atau kekanan atas perintah denyut lonceng (Sinyal Clock). Dalam alat ukur digit, register dipakai untuk mengingat data yang sedang ditampilkan.

Pada praktikum kita hanya menguji register geser (Shift Register) yaitu register

SISO (Serial In Serial Out), register PIPO (Paralel In Paralel Out), register PISO

(Paralel In Serial Out) dan register SIPO (Serial In Paralel Out). Keempaat register tersebut merupakan bagian dari register geser (Shift Register). Yang pertama adalah register SISO (Serial Input – Serial Output). Register geser SISO menerima data secara serial, bit-per-bit. Selanjutnya mengeluarkan data tersebut secara serial pula, bit-per-bit setiap satu pulsa clock. Cara kerja pengujiannya adalah sinyal clock T berfungsi untuk menggeser data masukan serial. Pertama yang dilakukan Atur kondisi awal sinyal kontrol R=1 dan OE=0, lalu masukan data serial pada SE sesuai pada tabel hasil percobaan yang disinkronkan dengan tombol T (tombol ditekan setelah penyetingan data pada SE). kemudian amati hasilnya sesuai perintahnya.

Register PIPO (Paralel Input – Paralel Output) merupakan uji coba selanjutnya setelah uji coba register SISO. Proses transfer data jenis ini adalah data dimasukkan secara paralel, kemudian dikeluarkan secara paralel juga. Cara kerjanya Dengan kondisi awal sinyal kontrol S=1, OE=0 dan R=1, kemudian kita beri masukan pada E5-E1 kemudaian ubah kondisi S=0. Dan yang terakhir kita Amati dan catat keluaran O1-O5 setelah kondisi OE=1. Hasil dari Register PIPO ini outputnya akan sama dengan inputnya seperti pada tabel kebenaran 2.2.1 Register PIPO (Paralel Input – Paralel Output).

bersesuaian, selanjutnya data dikeluarkan secara serial bit-per-bit setiap satu pulsa

clock.

BAB IV

KESIMPULAN DAN SARAN E. KESIMPULAN

9. Register adalah suatu rangkaian logika yang berfungsi untuk menyimpan data yang berupa 1 (satu) atau beberapa flip-flop yang digabungkan menjadi 1 (satu).

10. Register penampung merupakan register kerjanya hanya sebagai penyimpan sementara biner.

11. Shift Register (register geser) adalah suatu register dimana informasi dapat bergeser (digeserkan).

12. Output Register PIPO akan sama dengan Input Paralel PIPO. F. SARAN

9. Sebaiknya saat membuat rangkaian pada digital experimenter sebaiknya secara teliti dan runtut.

10. Sebelum melakukan praktikum harus memahami materi yang akan dipraktikkan.

11. Pastikan alat yang akan digunakan berfungsi secara baik.

BAB V

DAFTAR PUSTAKA Ibrahim, K. (1996). Teknik Digital. Yogyakarta: ANDI.

Maulana, Aldo. (2012). Register. https://www.scribd.com/doc/95932695/Lab-Register. 10 Mei 2015 (21:50).

Muis, S. (2007). Teknik Dasar Digital Pendekatan Praktis. Yogyakarta: Graha Ilmu.