1. Programmable Logic Device (PLD) 1. Programmable Logic Device (PLD) 1.1. Apa itu PLD ?

1.1. Apa itu PLD ?

PLD adalah suatu

PLD adalah suatu devicedevice digital dimana fungsi-fungsi digital dimana fungsi-fungsi logikanya dapat diprogram sesuai dengan kebutuhan dari pemakai. logikanya dapat diprogram sesuai dengan kebutuhan dari pemakai. Terdapat beberapa jenis PLD, yaitu :

Terdapat beberapa jenis PLD, yaitu : 1.

1. Simple PLD (SPLD)Simple PLD (SPLD) 2.

2. Complex PLD (CPLD)Complex PLD (CPLD) 3.

3. Field Programmable Gat Field Programmable Gate Array (FPGA)e Array (FPGA)

SPLD adalah PLD yang paling sederhana yang kira-kira ekivalen SPLD adalah PLD yang paling sederhana yang kira-kira ekivalen dengan

dengan sekitar sekitar 100-1000100-1000 gate gate.. Device y Device yang temasuk SPLD adalah :ang temasuk SPLD adalah : 1.

1. Programmable Arra Programmable Array Logic (PAL)y Logic (PAL) 2.

2. Gate Array Logic (GAL)Gate Array Logic (GAL) Struktur utama dari SPLD terdiri atas : Struktur utama dari SPLD terdiri atas :

1.

1. Product term array Product term array 2.

2. Macrocells Macrocells

Sebuah CPLD ekivalen dengan sekitar beberapa ratus sampai ribuan Sebuah CPLD ekivalen dengan sekitar beberapa ratus sampai ribuan gate. Sebuah memiliki semua yang dimiliki oleh CPLD ditambah gate. Sebuah memiliki semua yang dimiliki oleh CPLD ditambah dengan :

dengan : 1.

1. Programmable inter Programmable interconnectconnect 2.

2. Programmable I/O cells Programmable I/O cells

Pada dasarnya, sebuah CPLD dapat dianggap sebagai gabungan dari Pada dasarnya, sebuah CPLD dapat dianggap sebagai gabungan dari beberapa

beberapa SPLD SPLD yang yang saling saling dihubungkan dihubungkan dengandengan programmable programmable interconnect

interconnect ..

FPGA adalah yang paling kompleks diantara semua PLD. FPGA adalah yang paling kompleks diantara semua PLD. FPGA diutamakan untuk desain rangkain sequensial yang FPGA diutamakan untuk desain rangkain sequensial yang memerlukan banyak

1.2. Mengapa Memakai PLD ? 1.2. Mengapa Memakai PLD ?

Sebelum adanya PLD, IC-IC digital seri TTL mendominasi Sebelum adanya PLD, IC-IC digital seri TTL mendominasi semua desain rangkaian digital. Berbagai jenis IC TTL dibuat untuk semua desain rangkaian digital. Berbagai jenis IC TTL dibuat untuk mengimplementasikan gerbang-gerbang (NOT, AND, OR dan mengimplementasikan gerbang-gerbang (NOT, AND, OR dan XOR),

XOR), flip-flop flip-flop,, shit shit register register ,, counter counter , dan sebagainya. Prosedur, dan sebagainya. Prosedur desain menggunakan IC TTL

desain menggunakan IC TTL dapat dilihat pada dapat dilihat pada gambar dibawah inigambar dibawah ini

Spesifikasi Spesifikasi Desain Desain Truth Truth Table Table Persamaan Persamaan Logika Logika Optimasi Optimasi & & Desain Desain Skematik Skematik Implementasi Implementasi

Terdapat beberapa permasalah dalam desain menggunakan IC TTL, Terdapat beberapa permasalah dalam desain menggunakan IC TTL, yai

yaitu :tu :

1.

1. Kerumitan, semakin kompleks suatu desain makaKerumitan, semakin kompleks suatu desain maka semakin banyak persamaan logika yang dihasilkan. semakin banyak persamaan logika yang dihasilkan. 2.

2. MasalahMasalah fan-in fan-in dan dan fan-out fan-out , suatu gerbang TTL hanya, suatu gerbang TTL hanya dapat

di-dapat di-load load dengan gerbang lain dalam jumlah yang dengan gerbang lain dalam jumlah yang terbatas sebelum terjadi perubahan level tegangan yang terbatas sebelum terjadi perubahan level tegangan yang merusak.

merusak. 3.

3. MasalahMasalah delay propagationdelay propagation, dalam seuatu desain TTL, dalam seuatu desain TTL dimana beberapa IC dihubungkan, maka masalah

dimana beberapa IC dihubungkan, maka masalah delaydelay dapat membuat system tidak strabil.

dapat membuat system tidak strabil.

Dengan adanya permasalahan diatas, maka suatu desainer system Dengan adanya permasalahan diatas, maka suatu desainer system digital dengan TTL harus sangat berhati-hati dalam mewujudkan digital dengan TTL harus sangat berhati-hati dalam mewujudkan desainnya. Untuk suatu system yang sangat besar, bias jadi akan desainnya. Untuk suatu system yang sangat besar, bias jadi akan diperlukan waktu yang sangat

diperlukan waktu yang sangat lama untuk implementasinylama untuk implementasinya.a.

Dengan menggunakan PLD yang telah didesain sedemikian Dengan menggunakan PLD yang telah didesain sedemikian rupa oleh produsennya untuk mengatasi berbagai masalah yang rupa oleh produsennya untuk mengatasi berbagai masalah yang mungkin timbul dalam desain system digital maka proses desain mungkin timbul dalam desain system digital maka proses desain suatu rangkaian digital akan menjadi lebih mudah dan cepat. Dengan suatu rangkaian digital akan menjadi lebih mudah dan cepat. Dengan menggunakan PLD, seorang desainer tidak lagi harus menggunakan PLD, seorang desainer tidak lagi harus menghubungkan banyak IC-IC TTL sehingga desain akan menjadi menghubungkan banyak IC-IC TTL sehingga desain akan menjadi lebih kompak dan memiliki performansi yang tinggi.

lebih kompak dan memiliki performansi yang tinggi.

1.3. PAL 1.3. PAL

PAL adalah yang paling sederhana diantara semua PLD. PAL adalah yang paling sederhana diantara semua PLD. PAL tersusun dari

gerbang OR adalah tetap

gerbang OR adalah tetap (fixed)(fixed). Dibawah ini ditunjukkan symbol. Dibawah ini ditunjukkan symbol standar untuk gerbang AND 3 masukan dengan diagram logik standar untuk gerbang AND 3 masukan dengan diagram logik ekivalen pada PAL :

ekivalen pada PAL :

Gambar 2.

Gambar 2. Diagram logic PAL untuk gerbang AND 3 masukan Diagram logic PAL untuk gerbang AND 3 masukan

Pada gambar diatas, garis horizontal tunggal yang muncul dari Pada gambar diatas, garis horizontal tunggal yang muncul dari gerbang AND digunakan untuk merepresentasikan beberapa sinyal gerbang AND digunakan untuk merepresentasikan beberapa sinyal masukan. Garis-garis vertical merepresentasikan masukan A, B dan masukan. Garis-garis vertical merepresentasikan masukan A, B dan C. Tanda silang menunjukkan adanya hubungan antara masukan C. Tanda silang menunjukkan adanya hubungan antara masukan sinyal A, B dan C dengan masukan dari gerbang AND. Untuk lebih sinyal A, B dan C dengan masukan dari gerbang AND. Untuk lebih jelasnya, perh

jelasnya, perhatikan contoh rangkaiatikan contoh rangkaian dibawah ini beserta dian dibawah ini beserta diagramagram ekivalenny

Untuk memudahkan pembahasan, maka diambil contoh langsung Untuk memudahkan pembahasan, maka diambil contoh langsung sebuah

sebuah PAL yang PAL yang umum dipaumum dipakai, yaitu PALkai, yaitu PALCE22V10. CE22V10. KonfigKonfigurasiurasi pena beserta diagram blok struktur

pena beserta diagram blok struktur internal dari PALCE22V10 dapatinternal dari PALCE22V10 dapat dilihat pada gambar 4 sedangkan. Struktur internal mendetail untuk dilihat pada gambar 4 sedangkan. Struktur internal mendetail untuk PAL ini dapat dilihat pada gambar selanjutnya.

PAL ini dapat dilihat pada gambar selanjutnya.

Gambar 4.

Gambar 5.

PALCE22V10 memiliki sebuah pena masukan untuk PALCE22V10 memiliki sebuah pena masukan untuk clock

clock , 11 buah pena masukan logika dan 10 buah pena keluaran-, 11 buah pena masukan logika dan 10 buah pena keluaran-masukan (I/O). Struktur dari sebuah

masukan (I/O). Struktur dari sebuah input buffer input buffer PALCE22V10 PALCE22V10 dapat dilihat pada gambar berikut ini :

dapat dilihat pada gambar berikut ini :

Gambar 6.

Gambar 6. Input buffer Input buffer PALCE22V10PALCE22V10

Sedangkan struktur dari

Seperti yang telah ditulis sebelumnya, suatu

Seperti yang telah ditulis sebelumnya, suatu SPLD memilikiSPLD memiliki beberapa

beberapa macrocell macrocell . Struktur dari sebuah. Struktur dari sebuah macrocell macrocell PALCE22V10 PALCE22V10 adalah sebagai berikut :

adalah sebagai berikut :

Gambar 8.

Gambar 8. Macrocell Macrocell PALCE22V10 PALCE22V10

Macrocell

Macrocell dari PALCE22V10 adalah sangat fleksibel karena dapat dari PALCE22V10 adalah sangat fleksibel karena dapat diprogram menjadi dalam beberapa mode :

diprogram menjadi dalam beberapa mode : 1.

1. Mode kombinasional aktifMode kombinasional aktif highhigh 2.

2. Mode kombinasional aktifMode kombinasional aktif lowlow 3.

3. Mode teregistrasi aktMode teregistrasi aktifif highhigh 4.

4. Mode teregistrasi aktMode teregistrasi aktifif lowlow

Dibawah ini dapat dilihat mode-mode konfigurasi untuk

Dibawah ini dapat dilihat mode-mode konfigurasi untuk macrocell macrocell PALCE22V10.

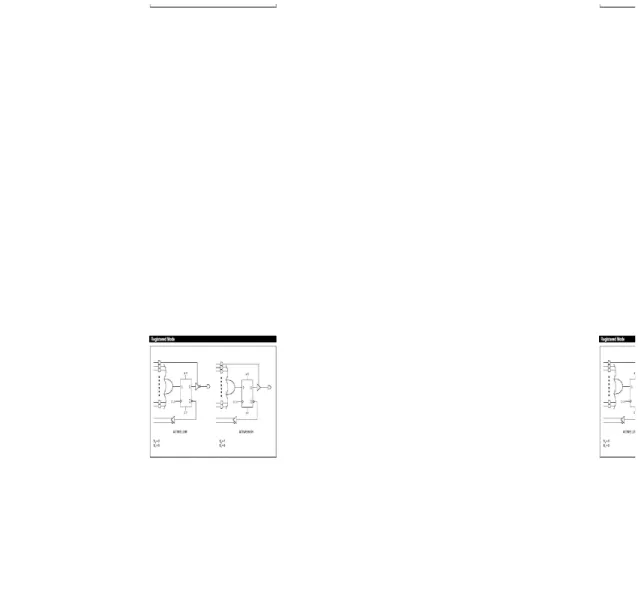

Gambar 9a.

Gambar 9a. Macrocell Macrocell PALCE22V10 dalam mode kombinasi PALCE22V10 dalam mode kombinasionalonal

Gambar 9b.

Untuk dapat memahami karakteristik dari PALCE22V10 Untuk dapat memahami karakteristik dari PALCE22V10 maka dibawah ini ditampilkan karakteristik

maka dibawah ini ditampilkan karakteristik switching switching dari dari PALCE22V10.

PALCE22V10.

Gambar 10.

Gambar 10. Karakteristik Karakteristik switching switching PALCE22V10 PALCE22V10

Untuk mengakhiri diskusi menganai PAL maka dibawah ini dapat Untuk mengakhiri diskusi menganai PAL maka dibawah ini dapat dilihat

1.4. CPLD 1.4. CPLD

Untuk memulai pembahasan mengenai CPLD, diambil Untuk memulai pembahasan mengenai CPLD, diambil contoh C

contoh CPLD XiliPLD Xilinx nx XC9500XV yXC9500XV yang memiliki ang memiliki struktur sebstruktur sebagaiagai berikut :

berikut :

Gambar 12.

Gambar 12. Struktur CPLD XC9500XV Struktur CPLD XC9500XV

Kemudian dapat dilihat pula kapasitas dari berbagai keluarga CPLD Kemudian dapat dilihat pula kapasitas dari berbagai keluarga CPLD XC9500XV pada table dibawah ini :

Tabel 1.

Tabel 1. Keluarga CPLD XC9500XV Keluarga CPLD XC9500XV

Untuk selanjutnya, struktur dari

Untuk selanjutnya, struktur dari function function block block dapat dilihat pada dapat dilihat pada gambar dibawah ini :

gambar dibawah ini :

Gambar 13.

Sedangkan struktur

Sedangkan struktur macrocellmacrocell dari CPLD tersebut adalah sebagidari CPLD tersebut adalah sebagi berikut :

berikut :

Gambar 14.

Gambar 14. Macrocell Macrocell CPLD XC9500XV CPLD XC9500XV

Struktur

Struktur programmable programmable interconnect interconnect dari CPLD XC9500XV dapat dari CPLD XC9500XV dapat dilihat pada gambar dibawah ini :

Gambar 15.

Gambar 15. Programm Programmable interconnect able interconnect CPLD XC9500XV CPLD XC9500XV

Untuk mengakhiri pembahasan mengenai CPLD, berikut ini Untuk mengakhiri pembahasan mengenai CPLD, berikut ini ditampilkan struktur blok I/O dari CPLD XC9500XV :

Gambar 16.

1.5. FPGA 1.5. FPGA

Teknologi FPGA diciptakan untuk meningkatkan kapasitas Teknologi FPGA diciptakan untuk meningkatkan kapasitas dan keandalan dari teknologi komponen digital terprogram dan keandalan dari teknologi komponen digital terprogram pendahuluny

pendahulunya. a. Secara Secara structural, structural, FPGA FPGA dan dan CPLD CPLD sangatlahsangatlah berbeda.

berbeda. Apabila Apabila CPLD CPLD terdiri terdiri atas atas kumpulankumpulan arrayarray OR dan AND OR dan AND serta

serta macrocell macrocell , maka FPGA terdiri atas sekumpulan sel-sel logika, maka FPGA terdiri atas sekumpulan sel-sel logika yang dikelilingi oleh sel-sel I/O yang saling dihubungkan oleh suatu yang dikelilingi oleh sel-sel I/O yang saling dihubungkan oleh suatu elemen terprogram.

elemen terprogram.

Gambar 17.

Gambar 17. Strukur FPGA pada umumnya Strukur FPGA pada umumnya 1.5.1. FPGA XC4000XL

1.5.1. FPGA XC4000XL

Arsitektur XC4000XL terdiri atas 3 komponen utama, yaitu Arsitektur XC4000XL terdiri atas 3 komponen utama, yaitu CLB

CLB (Configurable Logic Block),(Configurable Logic Block), IOB (IOB ( Input Input Output Output Block Block ), PI), PI (( Programm Programmable Interconect able Interconect ).).

Pengguna dapat menggunakan IOB untuk hubungan antar muka Pengguna dapat menggunakan IOB untuk hubungan antar muka dengan rangkaian eksternal, CLB untuk menyatakan fungsi logika dengan rangkaian eksternal, CLB untuk menyatakan fungsi logika yang diinginkan dan interkoneksi untuk menyatakan jaringan fungsi yang diinginkan dan interkoneksi untuk menyatakan jaringan fungsi logika dalam skala besar.

logika dalam skala besar.

Fungsi logika, interkoneksi dan penggunaan IOB ditentukan Fungsi logika, interkoneksi dan penggunaan IOB ditentukan oleh data yang tersimpan pada sel memori statik internal (keluarga oleh data yang tersimpan pada sel memori statik internal (keluarga XC4000 menggunakan teknologi SRAM untuk menyimpan data XC4000 menggunakan teknologi SRAM untuk menyimpan data konfiurasi).

konfiurasi). 1.5.1.1

1.5.1.1 CoConfnf igurigur abable le LL ogogic Blic Bl ocock (CLk (CL B)B)

Suatu array CLB merupakan elemen fungsional yang Suatu array CLB merupakan elemen fungsional yang menyusun fungsi logika dari pengguna. CLB disusun dalam bentuk menyusun fungsi logika dari pengguna. CLB disusun dalam bentuk matriks ditengah-tengah divais. Setiap CLB mempunyai bagian matriks ditengah-tengah divais. Setiap CLB mempunyai bagian logika kombinasional yang ada pada

logika kombinasional yang ada pada function function generator generator , elemen, elemen penyimpan, b

Setiap CLB dapat merealisasikan fungi-fungsi sebagai berikut : Setiap CLB dapat merealisasikan fungi-fungsi sebagai berikut :

1.

1. Sembarang fungsi dengan 4 input dan fungsi kedua denganSembarang fungsi dengan 4 input dan fungsi kedua dengan 4 input berbeda ditambah fungsi ketiga dengan input yang 4 input berbeda ditambah fungsi ketiga dengan input yang lain

lain. . (bila 3 (bila 3 fungsi fungsi berbeda berbeda dibuat, mdibuat, maka sebaka sebuah uah outputoutput fungsi harus di

fungsi harus di capturecapture keke flip-flop flip-flop internal internal CLB. CLB. Hanya Hanya 22 output

output function generator function generator yang dapat dibuat dari CLB). yang dapat dibuat dari CLB). 2.

2. Sembarang Sembarang satu fsatu fungsi hiungsi hingga 5 vngga 5 variabel.ariabel. 3.

3. Satu fungsi sembarang dengan 4 variabel ditambahSatu fungsi sembarang dengan 4 variabel ditambah beberapa fungsi

beberapa fungsi dengan 6 variabeldengan 6 variabel.. 4.

4. Beberapa fungsi hingga 9 variabel.Beberapa fungsi hingga 9 variabel.

Untuk lebih jelasnya maka dapat dilihat dari penjelasan isi CLB Untuk lebih jelasnya maka dapat dilihat dari penjelasan isi CLB sebagai berikut :

sebagai berikut :

F

F ununction Gection Genenerratoatorr

1.

1. Function Gener Function Generator F dan Gator F dan G

Masing-masing dapat menangani definisiMasing-masing dapat menangani definisi

boolean

boolean hingga 4 input. hingga 4 input.

Masing-masing memiliki 4 input dan 1Masing-masing memiliki 4 input dan 1

output. output.

Label kedua buah outputnya F’ dan G’.Label kedua buah outputnya F’ dan G’.

Propogation Propogation delaydelay-nya -nya tidaktidak

mempenga

mempengaruhi yang ruhi yang lainlain.. 2.

2. Function Gener Function Generator H ator H

Memiliki Memiliki 3 input 3 input dan dan 1 output. 1 output. DenganDengan

label outputnya H’ label outputnya H’

2 inputnya dapat diambilkan d2 inputnya dapat diambilkan d ari F’ danari F’ dan

G’.

G’. Atau dari Atau dari luar luar CLB (H0 CLB (H0 dan dan H2).H2).

1 input terakhir harus dari luar CLB (H1).1 input terakhir harus dari luar CLB (H1).

Flip-Flop Flip-Flop

Selain dapat dihubungkan ke

Selain dapat dihubungkan ke interconect network interconect network , output, output CLB juga dapat dihubungkan ke salah satu atau kedua

CLB juga dapat dihubungkan ke salah satu atau kedua flip-flop flip-flop.. Flip- Flip- flop

flop ini sendiri dapat dihubungkan juga ini sendiri dapat dihubungkan juga interconect network interconect network . Sebagai. Sebagai elemen

elemen memorymemory, konfigurasi, konfigurasi flip-flops flip-flops ini dapat dilihat dalam tabel ini dapat dilihat dalam tabel berikut.

berikut.

Tabel 2.

L

L atcatch (Unh (Un tuk tituk ti pe pe XC40XC400000XLXL ))

Ditunjukkan pada tabel diatas, bahwa

Ditunjukkan pada tabel diatas, bahwa latchlatch yang digunakan yang digunakan adalah

adalah common clock common clock (CLK) dan (CLK) dan clock enableclock enable (CE) input. (CE) input.

Cloc

Clock Ik I npu npu tt

Dapat

di-Dapat di-triggertrigger secarasecara rising rising atau atau falling falling edgeedge.. Clock Clock ini ini digunakan b

digunakan bersama denersama dengan elemen mgan elemen memori dan emori dan dapat dibalik untukdapat dibalik untuk masing-masing elemen memori.

masing-masing elemen memori.

Clock E

Clock E nablenable

Clock enable

Clock enable mempunyai nilai aktifmempunyai nilai aktif highhigh. CE digunakan. CE digunakan bersama den

bersama dengan elemen memgan elemen memori dan di CLB tidak dapat baliori dan di CLB tidak dapat balik.k.

Set/Reset Set/Reset

Masukan elemen sinkron memori (SR) dapat dioperasikan Masukan elemen sinkron memori (SR) dapat dioperasikan sebagai

sebagai set set ataupunataupun reset reset . Konfigurasi ini tergantung saat proses. Konfigurasi ini tergantung saat proses konfigurasi. Dan terpengaruh juga dari operasi

konfigurasi. Dan terpengaruh juga dari operasi Global Set/Reset Global Set/Reset selama proses operasi normal serta juga dipengaruhi dari pin SR selama proses operasi normal serta juga dipengaruhi dari pin SR CLB.

CLB.

Gl

Gl obal obal SeSet/t/ReResseet (t (GSR)GSR)

Line Global Set/reset

Line Global Set/reset yang terpisah dapat men-yang terpisah dapat men- set set atau atau clear clear elemen

elemen memorymemory selama selama power up power up, konfigurasi , konfigurasi ulang, ulang, atau jatau jalur resealur resett tertentu diaktifkan. Setiap

tertentu diaktifkan. Setiap flip-flop flip-flop dapat dikonfigurasi oleh GSR dapat dikonfigurasi oleh GSR atau l

atau local Set/reset. ocal Set/reset. GSR iGSR ini ni dapat di-dapat di-driver driver dari dari user programmableuser programmable pin sebagai

Gambar 19.

Gambar 19. SkemaSkematik untuk tik untuk global Set/Resetglobal Set/Reset

Masukan elemen memori adalah F’, G’ dan H’ atau dengan

Masukan elemen memori adalah F’, G’ dan H’ atau dengan Direct In Direct In (DIN)

(DIN) block input block input . Sedangkan. Sedangkan flip-flop flip-flop menggerakkan blok XQ dan menggerakkan blok XQ dan YQ.

YQ.

F

F asast Cat Carrrr y y LL ogogicic

Sesungguhnya, CLB F dan G telah dibuat untuk Sesungguhnya, CLB F dan G telah dibuat untuk menghasilkan

menghasilkan logika logika aritmatik aritmatik dengan sinydengan sinyalal carrycarry dandan borrowborrow yangyang cepat.

cepat. Fast Fast Carry Carry logiclogic ini bisa mencapai kecepatan aritmatik danini bisa mencapai kecepatan aritmatik dan perhitungan hi

perhitungan hingga 70 MHz.ngga 70 MHz.

1.5.1.2

1.5.1.2 II nput Outpnput Output Blut Bl ocock k (IOB) (IOB)

Setiap IOB berfungsi sebagai sarana u

Setiap IOB berfungsi sebagai sarana untuk menghubungkanntuk menghubungkan antara rangkaian eksternal melalui pin kemasan divais de

antara rangkaian eksternal melalui pin kemasan divais dengan fungsingan fungsi logika internal. Setiap IOB dapat diprogram untuk difungsikan logika internal. Setiap IOB dapat diprogram untuk difungsikan sebagai input, output

sebagai input, output ataupun sebagai bidirectional (dua arah). ataupun sebagai bidirectional (dua arah). BuffeBufferr input IOB dilengkapi dengan pendeteksi tegangan ambang yang input IOB dilengkapi dengan pendeteksi tegangan ambang yang dapat menterjemahkan sinyal eksternal pada pin kemasan menjadi dapat menterjemahkan sinyal eksternal pada pin kemasan menjadi level logika.

level logika.

Input pada XC4000XL kompatibel dengan TTL dan 3.3 Input pada XC4000XL kompatibel dengan TTL dan 3.3

input 5V meskipun dengan Vcc yang hanya 3.3V. Output input 5V meskipun dengan Vcc yang hanya 3.3V. Output XC4000XL telah di pull-up pada tegangan positif 3.3V dan XC4000XL telah di pull-up pada tegangan positif 3.3V dan mempunyai kemampuan arus hingga 12mA.

mempunyai kemampuan arus hingga 12mA.

Karakteristik dari kemampuan tegangan input-output dari Karakteristik dari kemampuan tegangan input-output dari XC4000XL dapat dilihat pada tabel berikut :

XC4000XL dapat dilihat pada tabel berikut :

Tabel 3.

Gambar 20.

Gambar 20. Diagram Blok IOB XC4000XLDiagram Blok IOB XC4000XL 1.5.1.3

1.5.1.3 PrPr ogrammable ogrammable II nterconnnterconneectct

Programmable

Programmable InterconnectInterconnect merupakan jalur routing yngmerupakan jalur routing yng menghubungkan input dan output dari IOB dan CLB untuk menghubungkan input dan output dari IOB dan CLB untuk membentuk jaringan fungsi yang diinginkan. Adanya fasilitas membentuk jaringan fungsi yang diinginkan. Adanya fasilitas

pengiriman

pengiriman sinyal sinyal dari dari 1 1 titik titik ke ke titik titik lain lain didalam didalam FPGA FPGA sesuaisesuai dengan yang dikehendaki. Fasilitas interkoneksi ini dibentuk dari dengan yang dikehendaki. Fasilitas interkoneksi ini dibentuk dari segmen logam (

segmen logam (metal segment metal segment ). Ada beberapa t). Ada beberapa tipe interkoneksi yaiipe interkoneksi yaitutu ::

1.

1. CLB routing CLB routing , yang menghubungkan baris dan kolom dalam, yang menghubungkan baris dan kolom dalam array

array CLB.CLB. 2.

2. IOB IOB routing routing , yang membentuk suatu “, yang membentuk suatu “ring ring ” (disebut” (disebut VersaRing

VersaRing ) ) disekitardisekitar arrayarray CLB.CLB. IOB IOB routingrouting menghubungkan IO dengan internal

menghubungkan IO dengan internal Logic Block Logic Block .. 3.

3. Global routing Global routing , yang berisi jaringan yang didesain terutama, yang berisi jaringan yang didesain terutama untuk distribusi

untuk distribusi clockclock dengandengan delaydelay dandan skew skew minimal.minimal.

Gambar diagram CLB routing dapat dilihat pada gambar berikut ini : Gambar diagram CLB routing dapat dilihat pada gambar berikut ini :

Gambar 21.

Ada 5

Ada 5 interconnect interconnect yang dibedakan berdasar panjang relatif dari yang dibedakan berdasar panjang relatif dari segmen, yaitu:

segmen, yaitu: 1.

1. Single-length linesSingle-length lines yang memberikan interkoneksi denganyang memberikan interkoneksi dengan fleksibilitas terbesar dan routing yang cepat antara CLB fleksibilitas terbesar dan routing yang cepat antara CLB yang berdekatan. Terdapat 8 vertikal single length line dan yang berdekatan. Terdapat 8 vertikal single length line dan 8 horisontal

8 horisontal single single length length lineline yang menghubungkan setiap yang menghubungkan setiap CLB dan dihubungkan dengan matriks

CLB dan dihubungkan dengan matriks switch switch yang dapat yang dapat diprogram.

diprogram.

Gambar 22.

Gambar 22. Programma Programmable switch matrixble switch matrix

2.

2. Double-length Double-length lineslines yang menawarkanyang menawarkan routingrouting sinyal yangsinyal yang lebih cepat untuk jarak menengah dengan

lebih cepat untuk jarak menengah dengan routingrouting yangyang fleksibel.

3.

3. Quad linesQuad lines yang memiliki kemampuan tercepat untuk yang memiliki kemampuan tercepat untuk routing jarak jauh karena terhubung dengan interkoneksi routing jarak jauh karena terhubung dengan interkoneksi switch matrik yang sangat cepat.

switch matrik yang sangat cepat. 4.

4. Octal linesOctal lines dandan Longlines Longlines yang merupakan segmen-segmen yang merupakan segmen-segmen metal yang melintas sejauh panjang dan lebar

metal yang melintas sejauh panjang dan lebar chipchip. Oleh. Oleh karena itu sangat cocok digunakan untuk

karena itu sangat cocok digunakan untuk routingrouting sinyalsinyal yang harus melewati jarak jauh, sinyal dengan

yang harus melewati jarak jauh, sinyal dengan time criticaltime critical atau sinyal dengan

atau sinyal dengan fan-out fan-out tinggi. tinggi.

Selain itu XC4000XL dilengkapi dengan

Selain itu XC4000XL dilengkapi dengan Direct Direct Interconnect

Interconnect yang sangat cepat dan efisien untuk CLB yang yang sangat cepat dan efisien untuk CLB yang berdekatan

berdekatan ataupun ataupun CLB CLB dan dan IOB IOB yang yang berdekatan. berdekatan. UntukUntuk GlobalGlobal Routi

Routing, terdapat 2 macam yang terdapat pada keluarga XC4000XL,ng, terdapat 2 macam yang terdapat pada keluarga XC4000XL, yai

yaitu :tu : a.

a. Global Low-Skew Buffer Global Low-Skew Buffer (BUFGLS). (BUFGLS). MerupakanMerupakan clock buffer standar yang digunakan untuk internal clocking clock buffer standar yang digunakan untuk internal clocking pada umumnya

pada umumnya.. b.

b. Global Early Buffer (BUFGE). Global Early Buffer (BUFGE). MenyeMenyediakan diakan akses akses clockclock dan interface input/output yang lebih cepat, tetapi akses CLB dan interface input/output yang lebih cepat, tetapi akses CLB dibatasi hingga ¼ kalinya.

dibatasi hingga ¼ kalinya. c.

c. Global Low-Skew BufferGlobal Low-Skew Buffer . Setiap sudut dari XC4000X. Setiap sudut dari XC4000X mempunyai 2

mempunyai 2 Global Low Skew buffer Global Low Skew buffer . . Masing Masing masingmasing dapat mencatu CLB manapun yang terdapat dalam divais. dapat mencatu CLB manapun yang terdapat dalam divais.

Gambar 23.

Gambar 23. BUFGLSBUFGLS d.

d. Global Early Buffer .. Tugas utama dariGlobal Early Buffer Tugas utama dari Global Early BufferGlobal Early Buffer ini ialah menyediakan clock access yang lebih awal daripada ini ialah menyediakan clock access yang lebih awal daripada Global Low- Skew Buffer

Global Low- Skew Buffer . Dengan sumber. Dengan sumber clock clock yang sama yang sama yang dicatukan ke kedua

yang dicatukan ke kedua buffer tersebut akan diperolehbuffer tersebut akan diperoleh clock clock dari

dari Global Early BufferGlobal Early Buffer sekian nano detik lebih awalsekian nano detik lebih awal daripada

daripada Global LowGlobal Low-Skew-Skew Buffer, Buffer, dengan beban yang lebih dengan beban yang lebih ringan.

ringan.

Gambar 24.

Gambar 25.

Gambar 25. BUFGE sisi kanan sisi kiriBUFGE sisi kanan sisi kiri

Global Early Buffer

Global Early Buffer bagian bagian atas atas dan dan bawahbawah devicedevice hanya hanya bisa

bisa mencatu mencatu 1 1 kuadran kuadran dari dari jumlah jumlah IOB.IOB. Global EarlyGlobal Early Buffer

Buffer sisi atas dan sisi bawah, berselisih 1 ns lebih lambatsisi atas dan sisi bawah, berselisih 1 ns lebih lambat dibandingkan

dibandingkan Global Early Buffer Global Early Buffer sisi kanan dan kiri. sisi kanan dan kiri. 1.5..1.4 Distribusi Daya

1.5..1.4 Distribusi Daya

Distribusi daya dan saluran ground pada FPGA tersusun Distribusi daya dan saluran ground pada FPGA tersusun dalam bentuk

dalam bentuk grid grid . Ini digunakan karena dapat mengurangi noise dan. Ini digunakan karena dapat mengurangi noise dan dapat berfungsi sebagai isolator antara sinyal-sinyal pada CLB dan dapat berfungsi sebagai isolator antara sinyal-sinyal pada CLB dan IOB. Bentuk ini juga memungkinkan penyaluran daya ke semua IOB. Bentuk ini juga memungkinkan penyaluran daya ke semua komponen yang ada dalam FPGA.

1.5.1.5 Mode Konfigurasi IC FPGA XC4000XL 1.5.1.5 Mode Konfigurasi IC FPGA XC4000XL

XC4000XL mempunyai 6 mode konfigurasi yang dipilih XC4000XL mempunyai 6 mode konfigurasi yang dipilih dengan memberikan nilai pada 3 bit input yaitu M2,M1 dan M0. dengan memberikan nilai pada 3 bit input yaitu M2,M1 dan M0. Mode yang tersedia adalah

Mode yang tersedia adalah Master Master dandan Slave Serial Slave Serial ,, Master Paralel Master Paralel Up

Up dandan Down Down,, Peripheral Peripheral SynchronousSynchronous, dan, dan Peripheral Peripheral Asynchronous

Asynchronous..

Kode untuk pemilihan mode dapat dilihat pada tabel berikut ini: Kode untuk pemilihan mode dapat dilihat pada tabel berikut ini:

Tabel 4.

Tabel 4. Mode konfigurasiMode konfigurasi

Berikut ini akan dijelaskan tentang mode

Berikut ini akan dijelaskan tentang mode Slave SerialSlave Serial dandan mode

mode Master Paralel dan Master Paralel dan modemode Slave Serial Slave Serial .. 1.5.1.5.1 Mode

1.5.1.5.1 Mode Slave SeSlave Serriial al

Pada mode ini, sebuah sinyal eksternal menggerakkan input Pada mode ini, sebuah sinyal eksternal menggerakkan input CCLK FPGA.

FPGA dalam waktu

FPGA dalam waktu setup setup yang singkat sebelum setiap kenaikan yang singkat sebelum setiap kenaikan tingkata

tingkatan n CCLK CCLK ((rising edgerising edge). Ini merupakan data awal yang). Ini merupakan data awal yang muncul pada pin DOUT-nya. Terdapat

muncul pada pin DOUT-nya. Terdapat delaydelay internal sebesar 0.5 internal sebesar 0.5 periode

periode CCLK CCLK yang yang berarti berarti DOUT DOUT berubah berubah pada pada sisi sisi turun turun CCLKCCLK (( falling falling CCLK CCLK edgeedge), mode), mode Slave SerialSlave Serial dipilih dengan data <111>dipilih dengan data <111> pada pin-pin

pada pin-pin mode-nymode-nya a (M2, M1, (M2, M1, M0).M0). Slave SerialSlave Serial ini adalah modeini adalah mode dasarnya

dasarnya apabila pinapabila pin-pin m-pin mode tidak diode tidak digunakan.gunakan.

Gambar 26.

Gambar 26. SistemSistem master/slavemaster/slave lengkap lengkap 1.5.1.5.2 Mode

1.5.1.5.2 Mode MM asasteter r ParalParal eel l

Pada dua mode Master Paralel (

Pada dua mode Master Paralel ( UpUp dan dan Down Down), FPGA), FPGA secara langsung mengalamati EPROM standar, dan dapat menerima secara langsung mengalamati EPROM standar, dan dapat menerima

data dengan lebar delapan bit tepat sebelum menaikkan atau data dengan lebar delapan bit tepat sebelum menaikkan atau menurunkan alamat PROM. Data paralel tersebut kemudian menurunkan alamat PROM. Data paralel tersebut kemudian diserialkan di dalam FPGA, dimana kemudian diteruskan ke pin diserialkan di dalam FPGA, dimana kemudian diteruskan ke pin DOUT-nya. Mode

DOUT-nya. Mode Master Master Parallel Parallel UpUp dipilih dengan memberikan dipilih dengan memberikan data <100> pada pin-pin mode (M2, M1, M0).

data <100> pada pin-pin mode (M2, M1, M0).

Gambar 27a.

Gambar 27a. SistemSistem Master Paralel Master Paralel dan ko dan koneksinya dengan paralelneksinya dengan paralel EEPROM

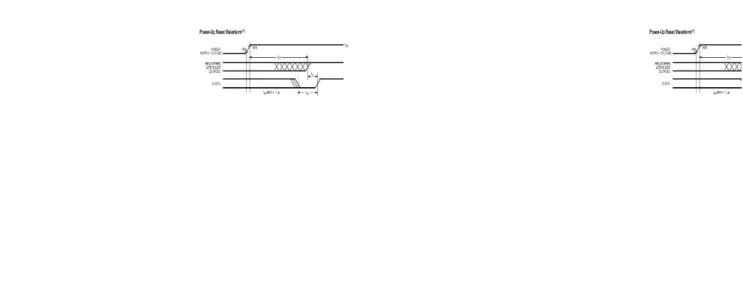

Gambar 27b.

Gambar 27b. KarakteristikKarakteristik switching switching pemrograman mode pemrograman mode mastermaster paralel

1.52 FPGA Spartan-II 1.52 FPGA Spartan-II

Keluarga FPGA Spartan-II dibuat oleh Xilinx Inc. untuk Keluarga FPGA Spartan-II dibuat oleh Xilinx Inc. untuk memperbaiki seri sebelumnya, yaitu keluarga FPGA Spartan-I. memperbaiki seri sebelumnya, yaitu keluarga FPGA Spartan-I. Secara umum, arsitektur keluarga ini adalah sebagai berikut :

Secara umum, arsitektur keluarga ini adalah sebagai berikut :

Gambar 28.

Gambar 28. ArsiArsitektur dasar tektur dasar FPGA FPGA Spartan-IISpartan-II

Berdasarkan gambar diatas maka arsitektur Spartan-II Berdasarkan gambar diatas maka arsitektur Spartan-II terdiri atas 5 komponen utama, yaitu :

terdiri atas 5 komponen utama, yaitu : 1.

1. CLBCLB (Configurable Logic Block)(Configurable Logic Block) 2.

2. IOBIOB (Input / Output Block)(Input / Output Block) 3.

3. DLLDLL (Delay-Locked Loop)(Delay-Locked Loop) 4.

4. BRBR (Block RAM)(Block RAM) 5.

1.5.2.1 CLB

1.5.2.1 CLB (Confi(Confi gurable gurable LL ogogic Block)ic Block)

Setiap CLB tersusun atas 2 buah

Setiap CLB tersusun atas 2 buah slice slice. Setiap. Setiap slice slice tersusun tersusun atas 2 buah LC

atas 2 buah LC (Logic Cell)(Logic Cell). Selain itu, di setiap CLB . Selain itu, di setiap CLB juga terdapat 1juga terdapat 1 multiplexer

multiplexer tambahan F6 dan 2 buah tambahan F6 dan 2 buah 3-state drivers3-state drivers. Struktur. Struktur slice slice pada Spartan-II adal

pada Spartan-II adalah sebagai beriah sebagai berikut :kut :

Gambar 29.

Penjelasan untuk setiap bagian-bagian CLB diatas adalah sebagai Penjelasan untuk setiap bagian-bagian CLB diatas adalah sebagai berikut :

berikut : 1.

1. LUTLUT (Look-Up Tables)(Look-Up Tables). Setiap LUT memiliki 4. Setiap LUT memiliki 4 input input dan dapat

dan dapat dikonfiguradikonfigurasi sebagaisi sebagai function generator function generator atau atau sebagai 16x1 bit SRAM. Kedua LUT dalam

sebagai 16x1 bit SRAM. Kedua LUT dalam slice slice dapat dapat digabung untuk membentuk 16x2 bit SRAM, 32x1 bit digabung untuk membentuk 16x2 bit SRAM, 32x1 bit SRAM, ataupun 16x1 bit

SRAM, ataupun 16x1 bit dual-portdual-port SRAM. LUT jugaSRAM. LUT juga dapat dikonfigurasi menjadi 16-bit

dapat dikonfigurasi menjadi 16-bit shift shift register register yang yang dapat

dapat dioperasidioperasikan dekan denganngan clock clock kecepatan tinggi. kecepatan tinggi. 2.

2. Multiplexer Multiplexer . Setiap. Setiap multiplexermultiplexer F5 digunakan untukF5 digunakan untuk memilih

memilih output output dari dari 22 function function generator generator pada setiap pada setiap slice

slice, sedangkan, sedangkan multiplexer multiplexer F6 F6 digunakan digunakan untukuntuk memilih output dari

memilih output dari multiplexermultiplexer F5.F5. 3.

3. Storage ElementsStorage Elements. Elemen ini dapat dikonfigurasikan. Elemen ini dapat dikonfigurasikan sebagai

sebagai edge-triggered D-Flip-Flopedge-triggered D-Flip-Flop atau sebagai atau sebagai level- level- sensitive

sensitive latchlatch. Setiap elemen dapan dikemudikan. Setiap elemen dapan dikemudikan melalui

melalui output output dari dari function function generator generator ataupun ataupun langsung dari

langsung dari input sliceinput slice dengan mem- dengan mem-bypassbypass function function generator

generator .. 4.

4. Arithmetic Logic Arithmetic Logic. . Tersusun Tersusun atasatas dedicated carry logicdedicated carry logic,, XOR

XOR gate gate dan dan ANDAND gate gate.. Dedicated Dedicated carry carry logiclogic memungkinkan

memungkinkan fast arithmetic carry fast arithmetic carry untuk perhitunganuntuk perhitungan aritmatika kecepatan tinggi. Kedua gerbang aritmatika kecepatan tinggi. Kedua gerbang memungkinkan untuk dibuatnya 1-bit

memungkinkan untuk dibuatnya 1-bit full full adder adder dalam dalam satu LC dan juga meningkatkan efisiensi dari proses satu LC dan juga meningkatkan efisiensi dari proses perkalian.

untuk mengkaskada

untuk mengkaskada function function generator generator untukuntuk mengimplementasikan fungsi logika yang besar.

mengimplementasikan fungsi logika yang besar. 5.

5. Three State Buffer Three State Buffer (BUFT). Setiap BUFT memiliki (BUFT). Setiap BUFT memiliki kontrol dan

kontrol dan input input tersendiri, digunakan untuk tersendiri, digunakan untuk mengemudikan

mengemudikan busbus internal. internal.

Jadi CLB dapat dikonfigurasikan sebagai : Jadi CLB dapat dikonfigurasikan sebagai :

1.

1. SRAM 16x1, 16x2 dan 32x1SRAM 16x1, 16x2 dan 32x1 2.

2. Dual port Dual port SRAM 16x1SRAM 16x1 3.

3. 16-bit16-bit Shift Register Shift Register 4.

4. Multiplexer Multiplexer 4:1 dan 8:1 4:1 dan 8:1 5.

5. Generator fungsi 5Generator fungsi 5 input input , 6, 6 input input , 9, 9 input input dan 19 dan 19 input input 6.

6. SuatuSuatu full full adder adder 1-bit dengan menggunakan 1-bit dengan menggunakan arithmeticarithmetic logic

logic

1.5.2.2 IOB

1.5.2.2 IOB (I(I nput / Outpnput / Output Blut Bl ocock)k)

Setiap IOB dapat dikonfigurasikan untuk mendukung Setiap IOB dapat dikonfigurasikan untuk mendukung berbagai

berbagai standar standar I/O, I/O, seperti seperti standar standar 3.3V, 3.3V, 2.5V 2.5V dan dan 1.5V. 1.5V. UntukUntuk level tegangan

level tegangan compatiblecompatible TTL, CMOS, PCI dan AGP digunakanTTL, CMOS, PCI dan AGP digunakan level tegangan 3.3V, untuk

level tegangan 3.3V, untuk low voltagelow voltage CMOS digunakan level CMOS digunakan level tegangan 2.5V. Setiap IOB dapat dikonfigurasikan sebagai

tegangan 2.5V. Setiap IOB dapat dikonfigurasikan sebagai input input ,, output

output atau atau bi-directional bi-directional . Struktur setiap IOB terlihat sebagai. Struktur setiap IOB terlihat sebagai berikut :

Gambar 30.

Gambar 30. SliceSlice pada CLB FPGA Spartan-II pada CLB FPGA Spartan-II

Register pada IOB dapat dikonfigurasikan sebagai

Register pada IOB dapat dikonfigurasikan sebagai edge- edge-triggered D-Flip-Flop

triggered D-Flip-Flop atau sebagai atau sebagai level sensitive latchlevel sensitive latch. Setiap IOB. Setiap IOB memiliki sinyal

memiliki sinyal clock clock (CLK) bersama dan sinyal (CLK) bersama dan sinyal clock enableclock enable (CE) (CE) independen untuk setiap register. Selain itu ketiga register tersebut independen untuk setiap register. Selain itu ketiga register tersebut juga

juga memiliki memiliki snyalsnyal set/preset set/preset (SR) bersama yang dapat (SR) bersama yang dapat dikonfigurasikan sebagai

dikonfigurasikan sebagai synchronous synchronous set, set, synchronous synchronous reset,reset, asynchrono

Setiap

Setiap pad pad pada IOB dapat dikonfigurasikan untuk pada IOB dapat dikonfigurasikan untuk memiliki suatu

memiliki suatu pull-up pull-up atauatau pull-dow pull-down n resistorsresistors, atau suatu, atau suatu weak- weak-keeper circuit

keeper circuit ..

1.5.2.3 DLL

1.5.2.3 DLL (D(D eellay-Lay-L ockeocked d LL oopoop))

Struktur dari suatu DLL secara sederhana terdiri atas Struktur dari suatu DLL secara sederhana terdiri atas variable line delay

variable line delay dandan control logiccontrol logic. Jaringan distribusi. Jaringan distribusi (clock(clock distribution network)

distribution network) mendistribusikan mendistribusikan clock clock keluaran ke seluruh keluaran ke seluruh register

register dan juga ke pin dan juga ke pin feedback feedback dari DLL. dari DLL. Control logicControl logic membaca membaca clock

clock masukan dan masukan dan clock feedbackclock feedback untuk melakukan pengaturanuntuk melakukan pengaturan terhadap

terhadap delay linedelay line agar menghasilkan sinyalagar menghasilkan sinyal clockclock yang tertundayang tertunda (delayed)

(delayed) dari dari clockclock masukan. Dengan mengatur besarnyamasukan. Dengan mengatur besarnya delaydelay yang dihasilkan maka

yang dihasilkan maka rising edgerising edge dari dari clock clock masukan dan masukan dan feedback feedback dapat dibuat agar menjadi berhimpit.

dapat dibuat agar menjadi berhimpit. ClockClock keluaran DLL menjadikeluaran DLL menjadi terkompensasi sehingga bebas dari

terkompensasi sehingga bebas dari delaydelay. Struktur sederhana dari. Struktur sederhana dari sebuah DLL dapat dilihat pada gambar dibawah ini :

sebuah DLL dapat dilihat pada gambar dibawah ini :

Gambar 31.

Setiap DLL pada Spartan-II dapat dihubungkan dengan satu Setiap DLL pada Spartan-II dapat dihubungkan dengan satu dari 4 pin

dari 4 pin clock clock melalui melalui global global clock clock bufferbuffer (BUFG), dan dapat(BUFG), dan dapat mengemudikan 2

mengemudikan 2 global global clock clock network network . . DLL DLL dapat dapat difungsidifungsikankan untuk :

untuk : 1.

1. MenghilangkanMenghilangkan skew skew pada pada clock input clock input 2.

2. Menghasilkan pergeseran faseMenghasilkan pergeseran fase clockclock 90, 180 dan 270 derajat90, 180 dan 270 derajat 3.

3. MenghasilkanMenghasilkan clock clock dengan frekuensi 2 kali dari dengan frekuensi 2 kali dari clock input clock input 4.

4. MenghasilkanMenghasilkan clock clock dengan dengan frekuensifrekuensi clock input clock input dibagi 1.5,dibagi 1.5, 2, 2.5, 3, 4, 5, 8, atau 16.

2, 2.5, 3, 4, 5, 8, atau 16.

1.5.2.4 BR

1.5.2.4 BR (Bloc(Block RAMk RAM ))

Spartan-II memiliki

Spartan-II memiliki block RAM block RAM kapasitas besar yang kapasitas besar yang memungkan untuk diperolehnya struktur memori yang lebih dalam memungkan untuk diperolehnya struktur memori yang lebih dalam dari yang disediakan oleh LUT pada CLB. Kapasitas total

dari yang disediakan oleh LUT pada CLB. Kapasitas total blockblock RAM

RAM pada berbagai pada berbagai devicedevice Spartan-II adalah sebagai berikut : Spartan-II adalah sebagai berikut :

Tabel 5.

Tabel 5. Kapasitas Kapasitas totatotall Block RAM Block RAM pada FPGA Spartan-II pada FPGA Spartan-II

Dev

Deviice ce # of # of BlBl ocks ocks TTotal otal BiBi tsts

XC2S15 XC2S15 4 4 16k16k XC2S30 XC2S30 6 6 24k24k XC2S50 XC2S50 8 8 32k32k XC2S100 XC2S100 10 10 40k40k XC2S150 XC2S150 12 12 48k48k XC2S200 XC2S200 14 14 56k56k

Block

Block RAM RAM dapat dikonfigurasikan menjadi RAM dengan kapasitas dapat dikonfigurasikan menjadi RAM dengan kapasitas sebagai berikut :

sebagai berikut :

Tabel 6.

Tabel 6. Konfigurasi Konfigurasi Block RAM Block RAM pada FPGA Spartan-II pada FPGA Spartan-II

Width

Width DeDepth pth ADDADD R R Bus Bus DATDAT A A BusBus

1 1 4096 4096 11:0 11:0 0:00:0 2 2 2048 2048 10:0 10:0 1:01:0 3 3 1024 1024 9:0 9:0 3:03:0 8 8 512 512 8:0 8:0 7:07:0 16 16 256 256 7:0 7:0 15:015:0 1.5.2.5 PRM

1.5.2.5 PRM (Pr(Pr ogogaammable mmable RoRoutiuti ng Mng M atriatri x)x)

Berguna untuk melakukan interkoneksi antara keempat Berguna untuk melakukan interkoneksi antara keempat komponen lainnya pada FPGA Spartan-II. Terdapat 5 jenis komponen lainnya pada FPGA Spartan-II. Terdapat 5 jenis interkoneksi

interkoneksi, , yaiyaitu :tu : 1.

1. Local Routing Local Routing . Memungkinkan interkoneksi antara :. Memungkinkan interkoneksi antara :

LUT, flip-flop dan General Routing MatrixLUT, flip-flop dan General Routing Matrix

(GRM) (GRM)

Feedback Feedback internal CLB untuk menghasilkan internal CLB untuk menghasilkan

koneksi kecepatan tinggi antar LUT dalam 1 koneksi kecepatan tinggi antar LUT dalam 1 CLB

CLB

Direct Direct pathpath yang memungkinkan koneksi yang memungkinkan koneksi

kecepatan tinggi antar CLB tetangga yang kecepatan tinggi antar CLB tetangga yang berada pada posi

Gambar 32.

Gambar 32. Local routing Local routing pada FPGA Spartan-II pada FPGA Spartan-II

General Purpose Routing General Purpose Routing . Memungkinkan interkoneksi. Memungkinkan interkoneksi

antar semua CLB pada

antar semua CLB pada devicedevice, terdiri dari :, terdiri dari : i.

i. General Routing MatrixGeneral Routing Matrix (GRM), menghubungkan (GRM), menghubungkan sembarang CLB tetangga baik pada posisi sembarang CLB tetangga baik pada posisi horisontal ataupun vertical

horisontal ataupun vertical ii.

ii. 24 single-length 24 single-length lines lines routeroute, menghubungkan, menghubungkan GRM tetangga baik pada posisi horizontal ataupun GRM tetangga baik pada posisi horizontal ataupun vertical

vertical iii.

iii. 96 buffered HEX lines route96 buffered HEX lines route, menghubungkan, menghubungkan GRM dengan jarak 6 blok dengan ketentuan GRM dengan jarak 6 blok dengan ketentuan koneksi hanya bisa dilakukan pada posisi awal, koneksi hanya bisa dilakukan pada posisi awal, akhir dan tengah

akhir dan tengah lineline.. iv.

iv. 12 buffered long lines12 buffered long lines, menghubungkan posisi, menghubungkan posisi mana saja pada

I/O I/O Routing Routing . Memungkinkan hubungan antara. Memungkinkan hubungan antara

CLB dengan IOB. Tersusun dalam suatu struktur CLB dengan IOB. Tersusun dalam suatu struktur yang mengelilingi CLB yang disebut dengan

yang mengelilingi CLB yang disebut dengan versaversa ring

ring . Memungkinkan hubungan dari CLB ke. Memungkinkan hubungan dari CLB ke sembarang IOB.

sembarang IOB.

Dedicated Dedicated Routing Routing . . Digunakan Digunakan untukuntuk

menghubungkan secara langsung beberapa sinyal menghubungkan secara langsung beberapa sinyal agar dapat diperoleh peformansi maksimal, terdiri agar dapat diperoleh peformansi maksimal, terdiri atas :

atas : i.

i. Horizontal routing resourc Horizontal routing resourceses, dihubungkan dengan, dihubungkan dengan 3-state buffers

3-state buffers memingkinkan memingkinkan terbentuknyaterbentuknya multiple buses

multiple buses pada setia pada setiap baris (posisi horisontal).p baris (posisi horisontal). ii.

ii. Dedicated Dedicated carry carry net net , memungkinkan pengiriman, memungkinkan pengiriman sinyal

sinyal carrycarry secara secara langsung ke CLB tetangga padalangsung ke CLB tetangga pada posisi vertikal

posisi vertikal..

Global Routing . Memungkinkan distribusiGlobal Routing . Memungkinkan distribusi clock clock

dan sinyal dengan

dan sinyal dengan fan-out fan-out sangat tinggi padasangat tinggi pada keseluruhan

keseluruhan devicedevice, terdiri atas :, terdiri atas : i.

i. Primary Primary Global Global Routing Routing , , berguna berguna untukuntuk menghubungkan 4 sinyal

menghubungkan 4 sinyal clock clock dengan semua dengan semua CLB, IOB dan

CLB, IOB dan block RAM block RAM .. ii.

ii. Secondari Global Routing Secondari Global Routing , tersusun atas 12 jalur, tersusun atas 12 jalur pada

pada sisi sisi atas atas dan dan 12 12 jalujalur r pada pada sisi sisi bawah bawah yangyang berguna untuk m

Gambar 33.

Gambar 33. Global clock routing Global clock routing pada FPGA Spartan II pada FPGA Spartan II

1.6. Rangkaian dengan

1.6. Rangkaian dengan PALCE22VPALCE22V1010

Pada gambar 34 dibalik ditunjukan rangkaian yang Pada gambar 34 dibalik ditunjukan rangkaian yang memanfaatkan PALCE22V10 untuk membuat sebuah

memanfaatkan PALCE22V10 untuk membuat sebuah trainer board trainer board PAL. Pada rangkaian tersebut diperlihatkan bahwa masukan ataupun PAL. Pada rangkaian tersebut diperlihatkan bahwa masukan ataupun keluaran ke atau dari PAL

di-keluaran ke atau dari PAL di- buffer buffer dengan IC 74HCT373. Hal ini dengan IC 74HCT373. Hal ini dimaksudkan untuk melakukan proteksi terhadap PAL karena PAL dimaksudkan untuk melakukan proteksi terhadap PAL karena PAL sangat rentan terhadap arus atau dan tegangan berlebih.

VII. Daftar Pustaka VII. Daftar Pustaka

---, Januari 2000, XAPP174 : Using the Spartan2 Delay-Locked ---, Januari 2000, XAPP174 : Using the Spartan2 Delay-Locked Loop.pdf,

Loop.pdf, http://direchttp://direct.xilinx.com/bvdocs/appnt.xilinx.com/bvdocs/appnotes/xapp174.pdf.otes/xapp174.pdf.

---, Maret 5, 2001, Spartan-II 2.5V FPGA Family : Introduction and ---, Maret 5, 2001, Spartan-II 2.5V FPGA Family : Introduction and Orderin

Ordering g Information, Information, http://www.xilihttp://www.xilinx.com/partinfo/ds001_nx.com/partinfo/ds001_1.pdf.1.pdf.

---, Maret 5, 2001, Spartan-II 2.5V FPGA Family : Functional ---, Maret 5, 2001, Spartan-II 2.5V FPGA Family : Functional Description

Description, , http://www.xilihttp://www.xilinx.com/partinfo/ds001_2.pdfnx.com/partinfo/ds001_2.pdf..

Skahill, Kevin & March, 1996, VHDL for Programmble Logic, Skahill, Kevin & March, 1996, VHDL for Programmble Logic, Cypress

Cypress Semiconductor, Semiconductor, SunnyvSunnyvale, ale, California California Addison-WesleyAddison-Wesley Publishing, Inc.