Diajukan Untuk Memenuhi Salah Satu Syarat Memperoleh Gelar Sarjana Teknik pada

Program Studi Teknik Elektro Fakultas Sains dan Teknologi

Oleh:

Nama : Inggit Novita Panannangan NIM : 035114010

PROGRAM STUDI TEKNIK ELEKTRO

JURUSAN TEKNIK ELEKTRO

FAKULTAS SAINS DAN TEKNOLOGI

UNIVERSITAS SANATA DHARMA

YOGYAKARTA

Presented as Partial Fulfillment of the Requirements To Obtain the Sarjana Teknik Degree

In Science and Technology Faculty

By:

Name : Inggit Novita Panannangan Student Number : 035114010

ELECTRICAL ENGINEERING STUDY PROGRAM

SCIENCE AND TECHNOLOGY FACULTY

SANATA DHARMA UNIVERSITY

YOGYAKARTA

MODULATOR QPSK

Oleh :

INGGIT NOVITA PANANNANGAN

NIM : 035114010

Telah disetujui oleh :

Pembimbing I

_____________________

Damar Widjaja, S.T., M.T. Tanggal _________________

Pembimbing II

_____________________

MODULATOR QPSK

(QPSK MODULATOR)

Oleh :

INGGIT NOVITA PANANNANGAN

NIM : 035114010

Telah dipertahankan di depan Panitia Penguji Pada tanggal : 8 Maret 2008

dan dinyatakan memenuhi syarat

Susunan Panitia Penguji

Nama Lengkap Tanda Tangan

Ketua : Martanto, S.T., M.T. ……… Sekretaris : Damar Widjaja, S.T., M.T. ... Anggota : A. Bayu Primawan, S.T., M.Eng. ... Anggota : Pius Yosy Merucahyo,S.T.,M.T. ...

Yogyakarta, 12 Maret 2008

Fakultas Sains dan Teknologi

Universitas Sanata Dharma

Dekan

karya atau bagian karya orang lain, kecuali yang telah disebutkan dalam kutipan

dan daftar pustaka, sebagaimana layaknya karya ilmiah.

Yogyakarta, 23Februari 2008

Inggit Novita Panannangan

“Semangat yang tinggi bukanlah jaminan kita akan berhasil,

namun tanpanya kita akan sulit melangkah dengan mantap”

Tugas akhir ini dipersembahkan untuk :

Bapaku yang di Sorga Yesus Kristus buat pertolonganNya dan

tuntunanNya selama hidupku

Orang tua dan saudaraku yang tercinta…

Teman-temanku yang kusayangi…..

Almamaterku……

informasi (pemodulasi) yang berfrekuensi rendah. QPSK merupakan salah satu modulasi digital yang merepresentasikan tiap dua bit dengan empat fasa yang berbeda. Keuntungan dari modulasi QPSK adalah memiliki bandwidth (BW) yang lebih efisien karena setiap dua bit data ditransmisikan dalam simbol modulasi tunggal. Penerapan pada modulator QPSK belum banyak dilakukan di fakultas ini. Tujuan penelitian ini yaitu membuat modulator QPSK sehingga mempermudah dosen dalam menjelaskan tentang modulasi QPSK dan mempermudah mahasiswa dalam memahaminya.

Modulator QPSK memiliki dua blok utama yaitu blok masukan data dan blok pemrosesan data. Blok masukan data berupa data digital terdiri dari multivibrator, pencacah, pembangkit kode Grey, register PISO, dan register SIPO. Sedangkan blok pemrosesan data terdiri dari komparator, osilator, integrator, balance modulator, summing amplifier, dan BPF.

Alat yang telah dibuat dapat bekerja dengan baik. Pergeseran fasa dari modulator QPSK sebanding dengan urutan data digital yang keluar dari demodulator QPSK. Modulator QPSK memiliki kecepatan data sebesar 20kbps dengan frekuensi carrier sebesar 100kHz.

Kata kunci : modulasi, modulasi QPSK, modulator QPSK.

QPSK is one of the digital modulation that is representing every two bits of data in different phases. The benefit of QPSK modulation is an efficient bandwidth due to transmission of two bits of data in a single modulation symbol. The application to QPSK modulator has not been done commonly in this faculty The aim of this research is making a QPSK modulator so that it can make lecturer easier in explaining about QPSK modulation and the students easier in understanding it.

QPSK modulator that has been made has two main blocks. There are data input block and data dprocessing block. Digital data input block consist of multivibrator, counter, Grey code generator, PISO register, and SIPO register. While data processing block consist of comparator, oscilator, integrator, balance modulator, summing amplifier, and BPF.

The device which has been made can work well. Phase shift from QPSK modulator equivalent with digital data sequence from QPSK demodulator. QPSK modulator has data rate of 20kbps and carrier frequency of 100kHz.

Keywords : modulation, QPSK modulation, QPSK modulator.

sehingga penulis dapat menyelesaikan penulisan Tugas Akhir ini yang berjudul

Modulator QPSK.

Skripsi ini ditulis bertujuan untuk memenuhi salah satu syarat dalam

memperoleh gelar sarjana teknik pada program studi Sains dan Teknologi

Universitas Sanata Dharma. Penulisan skripsi ini didasarkan pada hasil-hasil yang

penulis peroleh berdasarkan pada perancangan alat, pembuatan alat, dan sampai

pada pengujian alat.

Penulisan skripsi ini dapat diselesaikan berkat bantuan, dorongan, dan

bimbingan dari berbagai pihak. Pada kesempatan ini penulis ingin mengucapkan

terima kasih yang sebesar-besarnya kepada :

1. Yesus Kristus sebagai penolong hidupku

2. Bapak Damar Wijaya, S.T, M.T. sebagai dosen pembimbing I dan Bapak

Martanto, S.T., M.T. sebagai pembimbing II yang telah bersedia

memberikan ide, saran, bimbingan, dan waktu untuk penulis dalam

menyelesaikan tugas akhir.

3. Papa, Mama, saudaraku Ledy, Jen, dan Evi yang selalu mendukung dalam

doa, memberikan semangat dan kasih sayang selama ini.

5. Teman-teman angkatan 2003 yang memberikan ide masukan dan

dorongan semangat pada penulis untuk cepat lulus Denis, Widi, Suryo,

Mery, Jacob, Jefri, Yosef, Opunk, Gi2h, Alex, Adit, Angga dan

teman-teman yang lainnya yang tidak disebutkan satu-persatu.

6. Teman-teman sepermainanku di Amakusa: Nike, Agnes, Jeni, Ayu, Tyas,

Desi, Henot, In-chan, Cendut, Cipi, Tata, D_K, Ita, Inri, Mira, Dian, Dewi,

Uut, Yemi, Lia, Reta, Titin, Flori, Putri, yang selalu memberi semangat

dan dorongan unutuk cepat- cepat ujian.

7. Teman-teman persekutuanku di Apostolos M’wilma, Yusak’TM, Sigit,

Berlin, Rikad, Ratna, Theo, Yeyik, dan teman-teman yang lain yang selalu

menghibur dan membuat aku lebih dekat dengan Tuhan. Trimakasih untuk

sharing dan persaudaraanya selama ini.

8. Laboran TE Mas Soer, Mas Mardie, Mas Broto untuk kesabaran dalam

mengajar menggunakan alat-alat di Lab. Tak ketinggalan Mas Ucup yang

selalu membuat kaget di Lab.

9. Semua pihak yang tidak dapat disebutkan satu persatu di sini, atas

kebaikan dan bantuannya kepada penulis.

Yogyakarta, 23Februari 2008

Inggit Novita Panannangan

HAL

HALAMAN JUDUL ... i

LEMBAR PENGESAHAN PEMBIMBING ... iii

LEMBAR PENGESAHAN PENGUJI ……… iv

PERNYATAAN KEASLIAN KARYA ... v

HALAMAN PERSEMBAHAN DAN MOTTO HIDUP... vi

INTISARI ... vii

ABSTRACT ... viii

KATA PENGANTAR ... ix

DAFTAR ISI ... xii

DAFTAR GAMBAR ... xvi

DAFTAR TABEL ... xxi

DAFTAR LAMPIRAN ... xxii

BAB I PENDAHULUAN ... 1

1.1 Latar Belakang ...1

1.2 Batasan Masalah ...2

1.3 Tujuan Penulisan ……….….... 3

1.4 Manfaat Penulisan ………..…... 3

1.5 Metodologi Penulisan ……… 3

1.6 Sistematika Penulisan ………. ... 4

2.3 PSK ... 7

2.4 QPSK ... 8

2.5 Modulator QPSK... 10

2.6 Komponen Pendukung Rangkaian Modulator QPSK ... 14

2.6.1 Multivibrator ... 14

2.6.2 Pencacah Asinkron Modulo-4 ... 16

2.6.3 Kode Grey ... 19

2.6.4 Register PISO ... 21

2.6.5 Register SIPO ... 24

2.6.6 Komparator ... 25

2.6.7 Osilator ... 26

2.6.8 Balance Modulator... 28

2.6.9 Integrator ... 29

2.6.10 Summing amplifier ... 32

2.6.11 Band Pass Filter... 33

BAB III PERANCANGAN ... 38

3.1 Multivibrator ... 39

3.2 Pencacah Asinkron Modulo-4 ... 42

3.6 Komparator... 48

3.7 Osilator ... 52

3.8 Balance Modulator ... 53

3.9 Integrator ... 56

3.10 Summing amplifier... 58

3.11 Band Pass Filter... 60

BAB III HASIL DAN PEMBAHASAN ... 64

4.1 Perangkat Hasil Penelitian ... 64

4.2 Pengujian Perangkat Secara Keseluruhan ... 65

4.2.1 Pengujian Modulator QPSK ... 65

4.2.2 Pengujian Tiap Blok ... 82

4.2.2.1 Multivibrator ... 82

4.2.2.1 Pencacah asinkron modulo-4 ... 84

4.2.2.1 Kode Grey... 85

4.2.2.1 Register PISO ... 86

4.2.2.1 Register SIPO ... 88

4.2.2.1 Komparator ... 89

4.2.2.1 Osilator ... 91

4.2.2.1 Balance Modulator ...92

BAB V PENUTUP ... 104

5.1 Kesimpulan ... 104

5.2 Saran ...104

DAFTAR PUSTAKA ... 105

Gambar 2.1 Proses modulasi...…..………... 5

Gambar 2.2 Proses modulasi digital...………..……... 6

Gambar 2.3 Sinyal keluaran PSK………... 7

Gambar 2.4 Diagram fasor QPSK...…...………..……...….…....9

Gambar 2.5 Bentuk gelombang tiap bit... 9

Gambar 2.6 Bentuk gelombang keluaran modulator QPSK...10

Gambar 2.7 Diagram blok modulator QPSK ……….………10

Gambar 2.8 Pulsa multivibrator astabil …….…………...…...14

Gambar 2.9 Pin IC Pewaktu 555 ...………....…...15

Gambar 2.10 IC LM555 sebagai multivibrator astabil ...………....…...15

Gambar 2.11 Flip-flop JK ...………...…...17

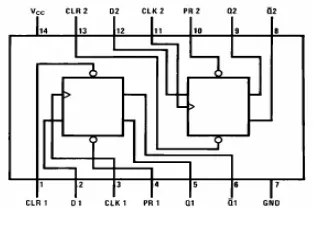

Gambar 2.12 Pin IC 74LS76 ……….. 18

Gambar 2.13 Gerbang logika XOR ………..…...19

Gambar 2.14 Rangkaian pengubah biner menjadi kode Grey ...20

Gambar 2.15 Pin IC 74LS86 ...…...…...20

Gambar 2.16 Rangkaian register PISO menggunakan flip-flop D ………..21

Gambar 2.17 Flip-flop D ……….………...…..22

Gambar 2.18 Pin IC 74LS74 …...………...…..24

Gambar 2.19 Rangkaian register SIPO menggunakan flip-flop D ...24

Gambar 2.20 Rangkaian komparator non inverting ...25

Gambar 2.24 IC XR2206 dengan rangkaian eksternal ... 28

Gambar 2.25 Pin IC MC 1496 ...…... 29

Gambar 2.26 Rangkaian dasar integrator ...……….. 30

Gambar 2.27 Rangkaian integrator AC …... 31

Gambar 2.28 Penguat penjumlah ... 32

Gambar 2.29 Karakteristik ideal BPF ………... 34

Gambar 2.30 Rangkaian dasar BPF ………..………... 34

Gambar 2.31 Kurva tanggapan BPF ………... 36

Gambar 3.1 Rangkaian multivibrator astabil ……… 41

Gambar 3.2 Sinyal keluaran hasil simulasi rangkaian multivibrator astabil ….... 41

Gambar 3.3 Rangkaian pencacah asinkron modulo-4………... 42

Gambar 3.4 Rangkaian register PISO ………... 44

Gambar 3.5 Timing diagram rangkaian register SIPO ……....…... 45

Gambar 3.6 Periode pada register PISO ……….……....…... 46

Gambar 3.7 Rangkaian SIPO dengan menggunakan IC 7474... 46

Gambar 3.8 Timing diagram hasil keluaran rangkaian register SIPO...48

Gambar 3.9 Periode pada register SIPO ……….……....…... 48

Gambar 3.10 Hasil simulasi pembagi tegangan... 49

Gambar 3.11 Rangkaian pembagi tegangan dengan op-amp sebagai buffer... 50

Gambar 3.12 Hasil simulasi rangkaian pembagi tegangan... 51

Gambar 3.16 Rangkaian pengali antara sinyal pemodulasi dengan sinyal carrier.. 54

Gambar 3.17 Sinyal keluaran hasil simulasi rangkaian pengali ... 55

Gambar 3.18 Hasil perancangan rangkaian integrator ... 57

Gambar 3.19 Sinyal keluaran hasil simulasi rangkaian integrator .…………...…. 57

Gambar 3.20 Rangkaian penjumlah... 59

Gambar 3.21 Sinyal keluaran hasil simulasi rangkaian penguat penjumlah... 59

Gambar 3.22 Blok rangkaian penguat penjumlah ………... 60

Gambar 3.23 Rangkaian BPF ……….………...…… 62

Gambar 3.24 Sinyal keluaran hasil simulasi BPF……….….. 63

Gambar 4.1 Tamapk atas perangkat ... 64

Gambar 4.2 Pengujian antara sinyal carrier dengan keluaran modulator QPSK 65 Gambar 4.3 Pengujian antara keluaran modulator dan keluaran demodulator QPSK ... 65

Gambar 4.4 Sinyal carrier dalam 1 periode ... 66

Gambar 4.5 Perbandingan sinyal carrier dan termodulasi dengan beda fasa 45° 67 Gambar 4.6 Perbandingan sinyal carrier dan termodulasi dengan beda fasa 135° ... 69

Gambar 4.7 Perbandingan sinyal carrier dan termodulasi dengan beda fasa -135° ………. 70

QPSK dengan demodulator QPSK ………..… 74

Gambar 4.10 Perbandingan antara keluaran register PISO dengan keluaran modulator QPSK setelah ditapis ...75

Gambar 4.11 Perbandingan keluaran antara modulator QPSK dengan demodulator QPSK pada kanal I ………...76

Gambar 4.12 Perbandingan keluaran antara modulator QPSK dengan demodulator QPSK pada kanal Q………...77

Gambar 4.13 Sinyal carrier dari osilator dengan frekuensi 100kHz ... 78

Gambar 4.14 Spektrum frekuensi sinyal carrier dari osilator ……… 78

Gambar 4.15 Sinyal carrier dari integrator dengan frekuensi 100kHz ... 79

Gambar 4.16 Spektrum frekuensi sinyal carrier dari integrator ….…….…...…... 80

Gambar 4.17 Data digital pada rangkaian register PISO untuk data 8 bit …..….... 81

Gambar 4.18 Perbandingan antara keluaran register PISO dengan keluaran sinyal termodulasi setelah ditapis ... 81

Gambar 4.19 Keluaran multivibrator saat kondisi Ton ... 83

Gambar 4.20 Keluaran multivibrator saat kondisi Toff ... 83

Gambar 4.21 Keluaran sinyal pencacah asinkron modulo-4 ... 84

Gambar 4.22 Sinyal keluaran dari kode Grey ... 86

Gambar 4.26 Keluaran komparator pada kanal Q ……... 90

Gambar 4.27 Amplitudo sinyal keluaran osilator ... 91

Gambar 4.28 Spektrum frekuensi balance modulator ... 92

Gambar 4.29 Keluaran balance modulator pada kanal I ... 93

Gambar 4.30 Keluaran balance modulator pada kanal Q ... 94

Gambar 4.31 Perbandingan antara sinyal pemodulasi, dan sinyal carrier dari osilator terhadap sinyal termodulasi kanal I………..…………..………... 95

Gambar 4.32 Perbandingan antara sinyal pemodulasi, dan sinyal carrier dari osilator terhadap sinyal termodulasi kanal Q………..…….….. 96

Gambar 4.33 Perbandingan antara keluaran register SIPO dengan register SIPO setelah melewati kapasitor ……….... 97

Gambar 4.34 Sinyal keluaran integrator ... 97

Gambar 4.35 Perbedaan fasa antara osilator dan integrator saat amplitudo sinyal 2V... 99

Gambar 4.36 Keluaran summing amplifier ... 100

Gambar 4.37 Grafik tanggapan BPF ………. 102

Tabel 2.1 Tabel kebenaran QPSK ………..………... 8

Tabel 2.2 Tabel kebenaran flip-flop JK ………..……….…. 18

Tabel 2.3 Perbedaan bilangan biner dengan kode Grey ………... 19

Tabel 2.4 Tabel kebenaran XOR ………... 20

Tabel 2.5 Tabel kebenaran flip-flop data ……… ……. 22

Tabel 2.6 Tabel kebenaran IC 74LS74 ………..…...…………. 23

Tabel 3.1 Tabel kebenaran IC 74LS76 ………..……….... 42

Tabel 3.2 Tabel Kebenaran IC 74LS86 ……….………...…. 43

Tabel 3.3 Keluaran rangkaian kode Grey... 44

Tabel 4.1 Data pengukuran sinyal dengan geser fasa 45 ° ... 68

Tabel 4.2 Data pengukuran sinyal dengan geser fasa 135 ° ... 69

Tabel 4.3 Data pengukuran sinyal dengan geser fasa 135 ° atau 225° ...71 Tabel 4.4 Data pengukuran sinyal dengan geser fasa -45 ° atau 315° ... 72

Tabel 4.5 Rangkuman data dari fasa hasil teori dan percobaan ………...73

Tabel 4.6 Data pengukuran BPF ……….….………... 98

Rangkaian modulator QPSK ……… L1

Rangkaian balance modulator ……….……… L2

Rangkaian osilator ………... L3

Tunda antara rangkaian modulator QPSK dengan demodulator QPSK ….. L4

Tunda antara rangkaian modulator QPSK dengan demodulator QPSK yang

diukur pada tiap blok rangkaian………... L5

Datasheet LM 555 ……….... L6

Datasheet 74LS76………... L7

Datasheet 74LS74 ………... L8

Datasheet 74LS86 ……… L9

Datasheet MC 1496 ………... L10

Datasheet XR 2206 ………. L1

BAB I

PENDAHULUAN

1.1.

Latar Belakang

Komunikasi memiliki tujuan yaitu mengirimkan informasi dari suatu

sumber ke suatu tujuan, dengan harapan bahwa informasi yang sampai sesuai

dengan yang dikirim. Sistem komunikasi dirancang untuk mentransmisikan

informasi atau sinyal dengan terlebih dahulu memodulasikan informasi atau sinyal

tersebut. Di dalam sistem komunikasi dikenal istilah modulasi. Modulasi

mengandung pengertian yaitu pengaturan parameter suatu gelombang pembawa

(carrier) yang berfrekuensi tinggi dengan sinyal informasi (pemodulasi) yang berfrekuensi rendah [1][2].

Teknik modulasi dibagi atas 2 bagian yaitu modulasi analog dan modulasi

digital. Modulasi analog terdiri atas Amplitude Modulation (AM), Frequency Modulation (FM), Phase Modulation (PM). Sedangkan modulasi digital terdiri

atas Amplitude Shift Keying (ASK), Frequency Shift Keying (FSK), Phase Shift Keying (PSK) [1].

Penelitian ini difokuskan pada modulator QPSK (Quadrature Phase Shift Keying). PSK adalah suatu sinyal carrier yang hanya memiliki keadaan dengan fasa tertentu. Jenis PSK yang terkenal adalah BPSK (Bi-Phase Shift Keying) dan

QPSK. Dalam PSK, biasanya keadaan fasa yang digunakan adalah 2n, misalnya n = 1 terdiri atas 2 fasa (binary, BPSK), n = 2 terdiri dari 4 fasa (quadrature,

QPSK) [3]. Dengan kata lain dapat dikatakan bahwa pada BPSK, tiap bit

direpresentasikan oleh fasa yang berbeda. Pada QPSK tiap 2 bit direpresentasikan

oleh fasa yang berbeda. Keuntungan dari modulasi QPSK adalah memiliki

bandwidth (BW) yang lebih efisien karena 2 bit ditransmisikan dalam simbol modulasi tunggal [1][4].

Penerapan pada modulator QPSK ini sudah banyak dilakukan oleh para

peneliti. Salah satunya diantaranya yaitu digunakan pada satelit GSO

(Geostationary Orbit) untuk layanan komunikasi bergerak [5]. Tetapi penerapan pada modulator QPSK belum banyak dilakukan dikampus ini. Oleh karena itu,

penulis mencoba merancang dan membuat suatu perangkat modulator QPSK agar

dapat mempermudah dosen dalam menjelaskan tentang modulasi QPSK dan

mempermudah mahasiswa dalam memahaminya.

1.2.

Pembatasan Masalah

Pada penyusunan Laporan Tugas Akhir ini, penulis membatasi

permasalahan yang ada. Batasan masalah tersebut antara lain adalah sebagai

berikut:

1. Keluaran modulator QPSK memiliki pergeseran fasa sebesar +45°, +135°,

-45°, -135° yang mewakili data 2 bit

2. Modulator QPSK memiliki kecepatan data sebesar 20kbps dan frekuensi

carrier 100kHz.

3. Urutan masukan data berupa data digital hanya mengalami perubahan

1.3.

Tujuan Penelitian

Tujuan yang ingin dicapai dalam penelitan ini adalah merancang dan

membuat suatu perangkat modulator QPSK.

1.4.

Manfaat Penelitian

Manfaat yang diharapkan yaitu:

1. Alat ini dapat mempermudah dosen dalam menjelaskan teknik

QPSK dan mempermudah mahasiswa dalam memahaminya.

2.

Dapat menjadi acuan dalam membuat modulator PSK denganpergeseran fasa yang lain.

1.5.

Metode Penelitian

Penelitian ini disusun berdasarkan studi literatur, serta mempelajari cara

kerja dan sekaligus cara-cara merencanakan dan membuat peralatan tersebut.

Perencanaan peralatan menggunakan teori yang ada untuk mendapatkan

karakteristik yang sesuai dengan spesifikasi yang ditentukan. Pembuatan peralatan

untuk setiap bagian sesuai dengan fungsi masing-masing dan kemudian diujikan.

Pengujian perangkat modulator QPSK ini dilakukan dengan cara melihat sinyal

1.6.

Sistematika Penulisan

1. BAB 1 PENDAHULUAN

Pendahuluan berisi latar belakang masalah, batasan masalah, tujuan

penelitian, manfaat penelitian, metode penulisan dan sistematika penulisan.

2. BAB II DASAR TEORI

Bab ini berisi penjelasan tentang modulator QPSK sebagai bagian dari

salah satu teknik modulasi digital yang memiliki keluaran dengan 4 fasa

yang berbeda.

3. BAB III ALUR PERANCANGAN

Bab ini berisi penjelasan alur perancangan pada modulator QPSK,

persamaan-persamaan matematis yang digunakan dalam menentukan

komponen pada rangkaian, serta parameter-parameter yang digunakan

dalam rangkaian.

4. BAB IV HASIL PERANCANGAN DAN PEMBAHASAN

Bab ini berisi hasil perancangan dengan keluaran pada rangkaian seperti

yang telah tertulis pada batasan masalah, analisa hasil perancangan yang

diperoleh.

5. BAB V KESIMPULAN DAN SARAN

Bab ini berisi ringkasan hasil penelitian yang telah dilakukan dan usulan

yang berupa ide-ide untuk perbaikan atau pengembangan terhadap

BAB II

DASAR TEORI

2.1

Modulasi

Pengertian modulasi yaitu proses pengaturan parameter dari suatu

gelombang pembawa (carrier) yang berfrekuensi tinggi dengan sinyal pemodulasi yang berfrekuensi rendah [2]. Tujuan dari modulasi yaitu [6]:

a. memudahkan pemancaran

b. mengurangi noise dan interferensi c. mengatasi keterbatasan hardware

modulasi

Sinyal pemodulasi Sinyal termodulasi

Sinyal carrier

Gambar 2.1 Proses modulasi [6]

Gambar 2.1 menunjukkan proses modulasi. Sinyal pemodulasi dimodulasi

dengan sinyal carrier sehingga menghasilkan sinyal termodulasi. Sinyal termodulasi merupakan keluaran dari proses modulasi.

Teknik modulasi dibagi menjadi 2 jenis yaitu modulasi analog dan

modulasi digital. Modulasi analog memiliki sinyal masukan berupa sinyal analog.

Proses dalam modulasi analog merupakan respon atas informasi dari sinyal

analog. Sedangkan modulasi digital memiliki sinyal masukan berupa sinyal

digital. Dalam modulasi digital, suatu sinyal analog dimodulasi berdasarkan aliran

data digital [7][8].

2.2

Modulasi Digital

Modulasi digital diperoleh dengan mengubah parameter sinyal carrier

(amplitudo, frekuensi, fasa) sesuai dengan sinyal pemodulasi yang berupa sinyal

digital [7]. Gambar 2.2 merupakan proses modulasi digital dengan sinyal masukan

berupa sinyal digital, sedangkan sinyal carrier berupa sinyal analog.

Pemodulasi (digital)

Carrier (

Gambar 2.2 Proses modulasi digital [7]

Teknik modulasi digital terdiri atas 3 yaitu ASK, FSK, dan PSK. Pada

ASK, deretan bit informasi direpresentasikan oleh level amplitudo carrier yang

berbeda. Pada FSK, frekuensi sinyal carrier diubah pada frekuensi tertentu tergantung pada bit informasi yang dikirim. Pada PSK, fasa sinyal carrier digeser

pada fasa tertentu tergantung pada bit informasi yang dikirim [7]. analog)

2.3

PSK

PSK merupakan proses representasi bit “1” dan bit “0” dengan fasa yang

berbeda. Setiap bit direpresentasikan dalam fasa tertentu [1]. Sinyal keluaran pada

PSK ditunjukkan pada Gambar 2.3.

Gambar 2.3 Sinyal Keluaran PSK [1]

Masing-masing fasa memiliki data digital yang unik [9]. Keadaan fasa

yang digunakan pada PSK yaitu 2n. Untuk n = 1 terdiri atas 2 fasa (binary, BPSK), n = 2 terdiri dari 4 fasa (quadrature, QPSK), dan n = 3 terdiri atas 8 fasa (M-ary

PSK) dan seterusnya [3].

Pada BPSK, tiap bit direpresentasikan oleh fasa yang berbeda. Perbedaan

fasa pada BPSK yaitu 180°. Pada QPSK, tiap 2 bit direpresentasikan oleh fasa

yang berbeda. Perbedaan fasa pada QPSK sebesar 90°. Pada M-ary PSK, tiap 3 bit direpresentasikan oleh fasa yang berbeda. Perbedaan fasa pada M-ary PSK sebesar 45° [1][10].

Sinyal keluaran dari PSK dinyatakan dengan [10]

dan

s(t) = Acos [2πfc + Φ(t)] (2.2)

Sinyal s(t) adalah sinyal termodulasi, fc adalah frekuensi carrier, sedangkan Φ(t) adalah fasa sinyal termodulasi.

2.4

QPSK

QPSK memiliki keluaran dengan 4 fasa yang berbeda. Masukan digital

pada QPSK terdiri atas 2 bit dengan 4 kondisi yaitu 00, 01, 10, dan 11. Karena ada

4 kondisi masukan yang berbeda, maka keluaran QPSK terdiri atas sinyal dengan

empat fasa yang berbeda yaitu π/ 4 (45º), 3π/4 (135º), 5π/4 (-135º), dan 7π/4 (-45º).

Setiap data 2 bit yang masuk akan mengakibatkan adanya satu perubahan fasa di

sisi keluaran. Sehingga kecepatan perubahan keluaran adalah setengah dari

kecepatan bit di sisi masukan [10]. QPSK memiliki bandwidth dua kali lebih

efisien dari BPSK, karena 2 bit ditransmisikan dalam simbol modulasi tunggal

[10][4]. Tabel 2.1 menunjukkan tabel kebenaran QPSK [10].

Tabel 2.1 Tabel kebenaran QPSK [10]

Masukan bit

I Q

Keluaran fasa QPSK

0 1 45°

0 0 135°

1 0 -135°

Gambar 2.4 Diagram fasor QPSK [10]

Gambar 2.4 menunjukkan diagram fasor QPSK. Jarak anguler antara kedua fasor yang berdekatan pada QPSK yaitu sebesar 90°. Karena itu suatu

sinyal QPSK bisa mengalami pergeseran fasa dari +45° ke +135° selama transmisi.

Keempat fasa keluaran pada QPSK memiliki amplitudo yang sama. Karena itu

informasi biner harus disandikan dalam bentuk perbedaan fasa sinyal keluaran.

Hal ini merupakan karakteristik yang paling penting pada QPSK yang

membedakannya dengan QAM ( Quadrature Amplitude Modulation ). Perbedaan bit pada QPSK yang berdekatan adalah hanya 1bit, contohnya 11 dan 01, 00 dan

10. Hal ini dilakukan untuk meminimalisasi terjadinya error dalam penyandian

karena hanya 1 bit yang berubah [10]. Gambar 2.5 merupakan titik awal

gelombang tiap bit yang relatif terhadap gelombang sinus murni.

Gambar 2.6 merupakan bentuk gelombang dari sinyal keluaran QPSK.

Gambar 2.6. Bentuk gelombang keluaran modulator QPSK [10]

2.5

Modulator QPSK

Penyandian pada QPSK terdiri atas 2 proses yaitu modulasi dan

demodulasi. Modulasi QPSK merupakan proses penyandian sinyal pemodulasi

berupa data digital menjadi sinyal analog dengan 4 perubahan fasa. Sedangkan

demodulasi QPSK merupakan proses penyandian kembali sinyal pemodulasi

berupa sinyal analog menjadi data digital dengan 4 keadaan. Diagram blok

modulator QPSK ditunjukkan pada Gambar 2.7.

Pada modulator QPSK, sinyal pemodulasi berupa data digital dengan dua

bit keluar secara serial kemudian diumpankan serentak secara paralel dengan

menggunakan register SIPO (serial input paralel output) ke kanal I(inphase) dan kanal Q (quadrature). Kanal I memodulasi suatu carrier yang fasanya sama

dengan osilator referensi. Keluaran dari kanal I berupa sinyal sinus. Sedangkan kanal Q memodulasi suatu carrier yang berbeda fasa 90° dengan osilator referensi.

Keluaran dari kanal Q berupa sinyal kosinus. Sinyal pemodulasi akan diubah dari NRZ (Nonreturn to Zero) unipolar menjadi bipolar, sehingga diperoleh logic 1 = +1V dan logic 0 = -1V. NRZ merupakan suatu penyandian yang menggunakan

dua tingkat tegangan yang berlainan untuk 2 digit biner. Sinyal carrier

dibangkitkan oleh osilator. Kemudian sinyal pemodulasi dari masing-masing

kanal akan dikalikan dengan sinyal carrier dengan menggunakan balance modulator (BM).

Keluaran modulator dari kanal I yang diperoleh dari hasil perkalian antara sinyal pemodulasi dan sinyal carrier adalah +sin ωct dan –sin ωct. Sedangkan

keluaran modulator dari kanal Q adalah +cos ωct dan –cos ωct. Keluaran dari

modulator tersebut dijumlahkan sehingga ada 4 fasa yang berbeda yaitu + cos ωct

+ sin ωct, + cos ωct – sin ωct, - cos ωct + sin ωct, dan - cos ωct – sin ωct [10].

Proses modulasi QPSK dinyatakan dengan [10] :

1. Sinyal pemodulasi 00 (I,Q), maka kanal I = -1 dan Q = -1

Balance modulator I = (-1)( sinωct) = -1sin ωct (2.3)

Hasil penjumlahan dari kedua kanal (I,Q) dinyatakan dengan

(0,0): -1sin ωct -1cos ωct = 2 cos (ωct +135°) (2.5)

2. Sinyal pemodulasi 01 (I,Q), maka kanal I = -1 dan Q = + 1

Balance modulator I = (-1)( sin ωct) = -1sin ωct (2.6)

Balance modulator Q = (+1)( cos ωct) = +1cosωct (2.7)

Hasil penjumlahan dari kedua kanal (I,Q) dinyatakan dengan

(0,1) : -1sin ωct + 1cos ωct = 2 cos (ωct + 45°) (2.8)

3. Sinyal pemodulasi 11 (I,Q), maka kanal I = +1 dan Q = +1

Balance modulator I = (+1)( sin ωct) = +1sin ωct (2.9)

Balance modulator Q = (+1)( cos ωct) = +1cos ωct (2.10)

Hasil penjumlahan dari kedua kanal (I,Q) dinyatakan dengan

(1,1) : +1sin ωct +1cos ωct = 2 cos (ωct - 45°) (2.11)

4. Sinyal pemodulasi 10 (I,Q), maka kanal I = +1 dan Q = -1

Balance modulatorI = (+1)( sin ωct) = +1sin ωct (2.12)

Balance modulatorQ = (-1)( cos ωct) = -1cos ωct (2.13)

Hasil penjumlahan dari kedua kanal (I,Q) dinyatakan dengan

(1,0) : +1sin ωct -1cos ωct = 2 cos (ωct -135°) (2.14)

Berdasarkan Gambar 2.7, rangkaian modulator QPSK menggunakan

beberapa test point yang terdiri atas test point MV, B0, B1, G0, G1, PISO, SIPO 1, SIPO 2, Komp I, Komp Q, Osc, Int, BM I, BM Q, Summing, Out QPSK yang

digunakan untuk mengamati ataupun mengukur setiap rangkaian pendukung pada

Fungsi dari masing-masing test point adalah :

1. Test point MV digunakan untuk mengamati clock yang akan membangkitkan sinyal pada masukan data digital.

2. Test point B0, dan B1 digunakan untuk mengamati sinyal masukan data

pada modulator QPSK.

3. Test point G0, dan G1 digunakan untuk mengamati sinyal masukan data

dengan perubahan 1 bit.

4. Test point PISO digunakan untuk mengamati sinyal masukan data secara serial.

5. Test point SIPO 1 dan SIPO 2 digunakan untuk mengamati urutan data yang masuk, yang kemudian akan diumpankan kekanal I dan Q.

6. Test point Komp I dan Komp Q digunakan untuk mengamati dan mengukur keluaran dari komparator sebagai penghasil sinyal pemodulasi

baik pada kanal I maupun pada kanal Q.

7. Test point Osc digunakan untuk mengamati dan mengukur sinyal sinus sebagai pembangkit sinyal carrier pada kanal I.

8. Test point Int digunakan untuk mengamati adanya pergeseran fasa sebesar

-90° dari kanal I.

9. Test point BM I, dan BM Q digunakan untuk mengamati dan mengukur

hasil sinyal termodulasi dari kanal I dan kanal Q.

10. Test point Summing digunakan untuk mengamati serta mengukur fasa setelah sinyal termodulasi dari kanal I dijumlahkan dengan sinyal

11. Test point out QPSK digunakan untuk mengamati keluaran dari modulator

QPSK setelah ditapis dengan menggunakan BPF.

2.6

Komponen Pendukung Rangkaian Modulator QPSK

Modulator QPSK terdiri atas multivibrator, pencacah asinkron modulo-4, Grey code (kode Grey), PISO, SIPO, komparator, balance modulator, osilator,

integrator, penguat penjumlah (summing amplifier), BPF (Band Pass Filter).

2.6.1. Multivibrator

Multivibrator (MV) berfungsi untuk membangkitkan pulsa yang menghasilkan keluaran berupa gelombang segiempat [11]. Cara kerja

multivibrator ada 3 jenis yaitu sebagai multivibrator astabil (bergerak bebas),

multivibrator monostabil (satu pulsa), dan multivibrator bistabil (flip-flop). Pulsa

multivibrator astabil ditunjukkan pada Gambar 2.8. Tegangan keluarannya beralih

dari tingkat yang tinggi ke tingkat yang rendah dan kembali lagi ke tingkat yang

tinggi[12].

Vo Keluaran Tinggi Keluaran Rendah

Multivibrator astabil

Vo

…..

Vcc

t

Multivibrator bisa dirancang dengan menggunakan IC pewaktu 555

(LM555). Cara kerja LM555 ditentukan oleh resistor yang terdiri atas RA dan RB

serta kapasitor (C) yang terhubung secara eksternal pada IC pewaktu tersebut [12].

Bentuk fisik IC LM555 ditunjukkan pada Gambar 2.9.

Gambar 2.9 Pin IC LM555 [13]

Gambar 2.10 IC LM555 sebagai multivibrator astabil[13]

Gambar 2.10 menunjukkan IC LM 555 yang berfungsi sebagai

multivibrator astabil. Pulsa keluaran tetap tinggi terjadi selama selang waktu saat

Waktu pengisian (t tinggi) dinyatakan dengan [12]

t tinggi= ln2 (RA+RB)C = 0,693(RA+RB)C (2.15)

Pulsa keluaran rendah terjadi selama selang waktu saat C dikosongkan dari

2/3Vcc sampai 1/3 Vcc. Waktu pengosongan (t rendah ) dinyatakan dengan

t rendah = ln2 RBC = 0,693RBC (2.16)

Periode osilasi total (T) yang dihasilkan

T = t tinggi + t rendah = 0,693 (RA+2RB)C (2.17)

Frekuensi osilasi ( f ) dari multivibrator astabil dinyatakan dengan

(

R R)

CT f

B A 2

443 , 1 1

+ =

= (2.18)

Sedangkan duty cycle (D) sebesar 50% pada multivibrator astabil dinyatakan dengan

100%

2 ×

+ + =

B A

B A

R R

R R

D (2.19)

2.6.2.

Pencacah Asinkron Modulus-4 ( Mod-4)

Pencacah merupakan suatu rangkaian logika yang berfungsi untuk

mencacah jumlah clock pada bagian masukan dan keluaran berupa digit biner [14].

Karena perancangan pada modulator QPSK menggunakan 2 bit dengan 4 keadaan,

maka digunakan pencacah modulus-4. Pencacah modulus-4 berfungsi untuk

mencacah hitungan dari bit 0 (00) sampai 3 (11) kemudian kembali ke 0 lagi.

Pencacah modulus-4 dapat disingkat dengan mod-4 [11]. Pencacah ini

asinkron. JK adalah singkatan dari Jack Kilby yang merupakan nama dari penemu

JK flip-flop [15]. Flip-flop JK memiliki berbagai manfaat yaitu sebagai pencacah

frekuensi, pembagi frekuensi, dan sebagainya [16].

Pencacah asinkron merupakan suatu pencacah yang tiap-tiap keluaran dari

flip-flop berfungsi sebagai sinyal clock untuk flip-flop selanjutnya secara berurutan. Gambar 2.11 merupakan flip-flop JK dengan tiga masukan sinkron

yaitu J, K dan clock.

Gambar 2.11 Flip-flop JK [11]

Masukan J dan K adalah masukan data, sedangkan masukan clock (CLK)

berfungsi untuk memindahkan data dari masukan ke keluaran. Q merupakan keluaran dan Q adalah komplementer dari keluaran pada suatu flip-flop. Selain masukan sinkron, flip-flop JK juga mempunyai masukan asinkron. Flip-flop JK

dengan masukan asinkron mempunyai suatu masukan yang membuat keluaran

flip-flop menjadi 1 yang disebut dengan preset (PR) dan masukan yang membuat keluaran flip-flop menjadi 0 yang disebut dengan clear (CLR) [11].

Bila kedua masukan J dan K bernilai 0, maka keluaran flip flop tidak

berubah keadaan. Flip-flop tersebut ada dalam mode tetap. Kondisi untuk

yang membuat keluaran menjadi 1 (set) dari flip-flop. Bila J = 1 dan K = 0 serta

pulsa clock datang pada masukan CLK, maka keluaran flip-flop bernilai 1. Baris 4 menunjukkan keadaan jika kedua masukan J dan K bernilai 1, maka keluaran

flip-flop akan berlawanan dengan keadaan pada waktu pulsa tiba pada masukan CLK

(togel). Dengan pulsa clock yang berulang, keluaran Q akan menjadi rendah, tinggi, rendah, tinggi, dan seterusnya [11].

Tabel 2.2 Tabel kebenaran flip-flop JK [11]

Perancangan pada pencacah sinkron modulus-4 menggunakan IC 74LS76

yang terdiri atas 2 flipflop JK yang terhubung secara terpisah. Gambar 2.12

menunjukkan bentuk fisik dari IC 74LS76.

2.6.3.

Kode Grey

Kode Grey berfungsi untuk mengubah bilangan biner 2 digit hanya satu bit.

Kode Grey sangat berguna dalam teknik digital. Sebuah kode Grey sebesar 2 bit dapat menyatakan perbedaan sebesar 22 = 4 keadaan [16]. Perbedaan antara kode Grey dan kode bilangan biner dapat ditunjukkan pada Tabel 2.3.

Tabel 2.3 Perbedaan bilangan biner dengan kode Grey [17]

Desimal Biner Grey

0 00 00

1 01 01

2 10 11

3 11 10

Kode Grey berubah hanya satu bit dari satu hitungan ke hitungan yang lainnya dan dari hitungan terakhir menjadi nol kembali. Pada desimal 1 ke 2,

bilangan biner akan berubah dari 01 ke 10. Pada pergantian dari 01 ke 10, terdapat

2 bit yang berubah ( 0 menjadi 1 atau 1 menjadi 0 ).

Peluang terjadinya error saat penyandian pada sistem biner sangat besar

karena terjadi perubahan sebesar 2 bit. Dengan menggunakan kode Grey, bilangan

desimal dari 1 ke 2 akan berubah dari 01 ke 11 sehingga hanya 1 bit yang berubah

[16].

Rangkaian pengubah kode bilangan biner menjadi kode Grey pada

dasarnya menggunakan gerbang logika XOR. Gerbang logika XOR ditunjukkan

pada Gambar 2.13.

U2

A

B Y

Tabel 2.4 Tabel Kebenaran XOR [16]

A B Y= A⊕B

0 0 0

0 1 1

1 0 1

1 1 0

Tabel kebenaran untuk gerbang logika XOR ditunjukkan pada Tabel 2.4.

Keluaran pada gerbang XOR akan bernilai 1 jika kedua masukannya berbeda.

Tetapi jika kedua masukannya sama, maka akan menghasilkan keluaran bernilai 0.

Gambar 2.14 Rangkaian pengubah bilangan biner menjadi kode Grey [16]

Gambar 2.14 menunjukkan rangkaian pengubah dari kode bilangan biner

menjadi kode Grey. Perancangan pada kode Grey menggunakan IC 74LS86. IC

74LS86 merupakan suatu IC XOR sebanyak 4 buah dengan 2 masukan. Gambar

2.15 menunjukkan bentuk fisik IC 74LS86.

2.6.4.

Register PISO

Register PISO merupakan suatu rangkaian yang masukannya dihubungkan

secara paralel dan keluarannya serial. Dalam perancangan, register PISO

digunakan untuk menghubungkan antara keluaran dari kode Grey dan register

SIPO. Register PISO termasuk salah satu jenis dari register geser. Register geser

adalah suatu rangkaian yang menggunakan flip-flopyang saling disambung secara

seri sehingga setiap bit yang disimpan di keluaran Q digeser ke flip-flop

berikutnya [14]. Pergeseran bit terjadi pada setiap pulsa clock. Dasar dari register geser yaitu menggeser data yang disimpannya. Proses bergesernya data yang

masuk ke dalam register sesuai dengan sinyal clock [16]. Flip-flop jenis apapun yang operasinya sesuai (terpicu tepian) dapat dipakai seperti flip-flop D, SR, atau

JK.

Pada perancangan digunakan sebuah flip-flop D yang terpicu tepi positif.

Gambar 2.16 menunjukkan rangkaian register PISO dengan menggunakan

flip-flop D VCC CLK D0 D1 OUT W/S CLR U1 JKFF J CLK K CL RN P R N Q U4 NAND2 U5 NAND2 U6 NAND2 U7 NAND2 U3 DFF D CLK CL R N P RN Q U2 DFF D CLK CL R N P RN Q

Dalam register ini, sinyal clock akan diumpankan secara bersama-sama

atau serentak kesemua flip-flop. Sinyal clock akan menggerakkan pergeseran data flipflop. Karena mode operasi yang digunakan sinyal clock berubah dari negatif ke positif atau tepi naik dari sinyal clock, maka flip-flop akan menganggapi untuk

sinyal kendali D pada setiap tepi pulsa positif. Setiap kali flip-flop menanggapi,

maka akan terjadi pergeseran. Gambar 2.17 merupakan flip-flop D dengan dua

masukan sinkron yaitu D dan clock.

Gambar 2.17 Flip-flop data [16]

Masukan D adalah masukan data, sedangkan masukan clock (CLK)

berfungsi untuk memindahkan data dari masukan ke keluaran. Q merupakan keluaran dan Q adalah komplementer dari keluaran pada suatu flip-flop. Tabel 2.5 merupakan tabel kebenaran flip-flop D.

Tabel 2.5 Tabel kebenaran flip-flop data [16]

Selain masukan sinkron, flip-flop data juga mempunyai masukan asinkron.

Flip-flop data dengan masukan asinkron mempunyai suatu masukan yang

suatu masukan yang membuat keluaran flip-flop menjadi 0 yang disebut dengan

clear [11]. Perancangan pada flip-flop D menggunakan IC 74LS74. IC 74LS74 berisi dua flip-flop data yang terpisah. Tabel 2.6 menunjukkan tabel kebenaran IC

74LS74.

Tabel 2.6 Tabel kebenaran IC 74LS74 [11]

Tiga baris pertama merupakan operasi asinkron. Baris 1 menunjukkan

masukan preset yang diaktifkan oleh suatu level rendah yang mengakibatkan

keluaran Q menjadi 1. Tanda ‘X’ pada masukan sinkron berarti bahwa masukan

tidak relevan karena masukan asinkron menolaknya. Baris 2 menunjukkan

masukan clear yang diaktifkan dengan suatu level randah, yang mengakibatkan keluaran Q menjadi 0. Baris 3 menunjukkan masukan asinkron yang terlarang

(baik preset maupun clear berada pada logika 0). Masukan sinkron akan

beroperasi bila semua masukan asinkron terbuka (preset = 1, clear = 1). Baris 4 menunjukkan logika 1 pada masukan D dan pulsa clock yang naik. Logika 1 pada

menunjukkan bahwa masukan D dengan logika 0 dipindahkan ke keluaran Q

pada pulsa clock tersebut. Gambar 2.17 menunjukkan bentuk fisik dari IC 74LS74.

Gambar 2.18 Pin IC 74LS74 [19]

2.6.5.

Register SIPO

Register SIPO merupakan suatu rangkaian yang masukannya dihubungkan

secara serial, dan keluarannya paralel. Dalam perancangan, register SIPO

digunakan untuk memisahkan data digital menjadi 2 kanal yaitu kanal I dan kanal

Q. Seperti halnya dengan register PISO, register SIPO termasuk salah satu jenis

dari register geser. Pada perancangan register SIPO, digunakan dua buah flip-flop

D yang berfungsi untuk memasukkan dan mengeluarkan data. Gambar 2.19

menunjukkan rangkaian register SIPO dengan menggunakan flip-flop data.

Setiap pulsa clock tepi positif terpicu, maka akan menggeser bit-bit data

satu posisi ke kanan. Data akan masuk secara berurutan kemudian akan

ditampilkan secara serentak.

2.6.6.

Komparator

Komparator berfungsi untuk membandingkan suatu tegangan isyarat pada

satu masukan dengan suatu tegangan acuan pada masukan lainnya. Komparator

terdiri atas 2 jenis, yaitu komparator inverting dan komparator non inverting. Pada komparator non inverting, tegangan referensi (Vref) dengan level prasikap

tegangan positif dipasang pada masukan inverting, sedangkan untuk sinyal masukan dipasang pada masukan non inverting [20]. Gambar 2.20 menunjukkan rangkaian pada komparator non inverting dengan level prasikap tegangan positif

Gambar 2.20 Rangkaian komparator non inverting [20]

Jika sinyal masukan lebih rendah dari pada tegangan referensi, maka

perbedaan tegangan yang dihasilkan bernilai negatif dan keluaran dari komparator

bernilai saturasi negatif (-Vsat). Sebaliknya, jika sinyal masukan lebih tinggi dari

pada tegangan referensi, maka perbedaan tegangan yang dihasilkan bernilai positif

dan keluaran dari komparator bernilai saturasi positif (+Vsat).

Vo = -Vsat untuk Vi<Vref (2.20)

Vo = +Vsat untuk Vi>Vref (2.21)

Kurva karakteristik masukan dan keluaran pada komparator non inverting

ditunjukkan pada Gambar 2.21.

Gambar 2.21 Kurva karakteristik masukan dan keluaran komparator [20]

2.6.7.

Osilator

Osilator berfungsi untuk membangkitkan sinyal sinusoidal. Pada

perancangan, osilator digunakan untuk membangkitkan gelombang carrier.

Karakteristik yang terpenting pada suatu osilator adalah bentuk gelombang,

amplitudo serta frekuensi dari sinyal yang dibangkitkan. Osilasi dapat diperoleh

dengan pemberian umpan balik positif pada sebuah rangkaian penguat (amplifier) [21]. Gambar 2.22 menunjukkan skematik dari blok osilator.

Masukan (Vi) dikalikan dengan suatu penguat (A) untuk memberikan

keluaran (Vo). Sebagian kecil dari Vo diumpan balikkan (β) kemudian diberikan pada Vi. Sehingga diperoleh

AβVi = Vi (2.22)

Aβ= 1 (2.23)

Aβ = 1 merupakan suatu kondisi yang diperlukan untuk memperoleh

osilasi dengan amplitudo yang stabil dengan bentuk gelombang yang tidak

terdistorsi. Ini dikenal dengan kriteria Barkhausen [2]. Jika loop gain lebih besar dari satu, maka akan terjadi pertambahan amplitudo yang terjadi secara

terus-menerus yang pada akhirnya menghasilkan distorsi bentuk gelombang.

Perancangan pada osilator menggunakan IC XR2206 yang bekerja pada rentang

frekuensi dari 0.01Hz sampai 1MHz.

Gambar 2.23 Pin IC XR2206 [22]

Gambar 2.23 menunjukkan bentuk fisik dari IC XR2206. Frekuensi

keluaran dari osilator dinyatakan dengan [22]

RC

Perubahan nilai frekuensi dilakukan dengan mengubah nilai resistor dan

kapasitor sebagai rangkaian eksternal dari IC XR 2206. Gambar 2.24

menunjukkan IC XR2206 dengan rangkaian eksternal.

Gambar 2.24 IC XR2206 dengan rangkaian eksternal [22]

2.6.8.

Balance Modulator

(BM)

Balance modulator berfungsi untuk mengalikan dua tegangan masukan yaitu sinyal pemodulasi dan sinyal carrier. Apabila digunakan sebagai modulator, masukan osilator menjadi masukan carrier dan masukan sinyal menjadi masukan

sinyal pemodulasi. Balance modulator beroperasi sebagai rangkaian multiplier

yang keluarannya merupakan sinyal termodulasi tetapi hanya berupa pasangan

Gambar 2.25 Pin IC MC 1496 [23]

Gambar 2.25 menunjukkan bentuk fisik dari IC MC 1596. Arus bias

internal pada IC MC 1596 diatur pada pin 5. Asumsi arus dinyatakan dengan [23]

I5 = I6 = I12 (2.22)

Besarnya nilai R5 pada pin 5 dinyatakan dengan [23]

R5 = −

( )

− −500Ω5 I

V φ

(2.23)

Berdasarkan datasheet MC 1496, nilai φ = 0.75 pada suhu TA = 25°C dan V =

12V.

2.6.9.

Integrator

Integrator adalah rangkaian yang membentuk suatu operasi matematis

yang disebut integrasi karena dapat menghasilkan tegangan keluaran yang

sebanding dengan integral masukan [24]. Dalam perancangan, integrator

digunakan untuk menggeser fasa dari masukan. Rangkaian dasar integrator adalah

Gambar 2.26 Rangkaian dasar integrator [24]

Gambar 2.26 merupakan rangkaian dasar dari integrator. Keluaran (Vo) integrator dinyatakan dengan

∫

−

= t in

o V dt

RC V

0

1

(2.24)

Impedansi masukan (Zi) dan impedansi umpan balik (Zf) integrator dinyatakan

dengan

R Zi = dan

C j Z f

ω 1

= (2.25)

Fungsi transfer H

( )

jω dinyatakan denganRC j R

C j j

H

ω ω

ω) 1 1

( = − = − (2.26)

sehingga menghasilkan respon amplitudo M

( )

ω yang dinyatakan dengan( )

RC M

ω

ω = 1 (2.27)

Semua masukan menuju kapasitor. Karena kapasitor dalam keadaan

terbuka untuk sinyal-sinyal DC, maka tidak ada umpan balik negatif pada

frekuensi nol. Tanpa umpan balik negatif pada frekuensi nol, rangkaian akan

Offset masukan akhirnya akan mengisi kapasitor dan menggerakkan

keluaran menjadi saturasi positif dan saturasi negatif. Cara untuk menurunkan

efek tegangan offset masukan adalah dengan menurunkan gain tegangan pada frekuensi rendah dengan menyertakan suatu resistor secara paralel terhadap

kapasitor. Hal ini disebut dengan integrator AC [20]. Gambar 2.27 adalah

rangkaian integrator AC.

Gambar 2.27 Rangkaian integrator AC [20]

Impedansi umpan balik dinyatakan dengan [20]

(

)

j R CR C j R C j R C j R Z f f f f f

f ω ω

ω ω + = + × = = 1 1 1 1

// (2.28)

Impedansi masukan dinyatakan dengan

Zi = Ri (2.29)

Fungsi transfer dinyatakan dengan

( )

C R j R R j H f i f ω ω + − =1 = f

i f j R R ωτ + −

1 (2.30)

Respon amplitudo dinyatakan dengan

( )

(

)

2( )

21

1 f

i f f

i

f R R

C R

R R M

ωτ ω

ω

+ = +

= (2.31)

2.6.9.

Summing Amplifier

Summing amplifier adalah suatu rangkaian op-amp yang merupakan kombinasi dari beberapa masukan dan menghasilkan keluaran berupa

penjumlahan dari masukan tersebut [25]. Summing amplifier berfungsi untuk menjumlahkan hasil kali dari kanal I (cos) dan hasil kali dari kanal Q (sin).

Gambar 2.28 menunjukkan rangkaian penguat penjumlah.

Gambar 2.28 Penguat penjumlah [25]

Persamaan KCL pada titik a adalah [25]

i=i1 +i2 +i3 (2.29)

dengan

1 1

R v v

i a

i

−

= (2.30)

2 2 2

R v v i = − a

3 3 3 R v v

i = − a (2.32)

f o a R v v

i= − (2.33)

Tegangan keluaran pada penguat inverting dinyatakan dengan [20]

i f

o V

R R

V =− ×

1

(2.34)

Tegangan = 0, sehingga tegangan keluaran pada penguat penjumlah dapat

dinyatakan dengan [25]

a v ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ + + − = 3 3 2 2 1 1 v R R v R R v R R

vo f f f (2.35)

2.6.10. BPF

Filter adalah rangkaian yang menghasilkan karakteristik tanggapan

frekuensi yang telah ditentukan dengan tujuan melewatkan sinyal dengan rentang

frekuensi tertentu dan menekan atau menolak sinyal dengan rentang frekuensi

yang lain [20]. Klasifikasi filter berdasarkan band terdiri atas LPF (Low Pass Filter), HPF (High Pass Filter). BPF akan melewatkan semua frekuensi dengan

bandwidth tertentu dari frekuensi rendah sampai frekuensi tinggi. Filter terdiri atas 2 jenis yaitu filter aktif dan filter pasif. Filter pasif terdiri atas kombinasi resistor, kapasitor, dan induktor (L). Filter aktif terdiri atas kombinasi RC dan

f fo

1

0

Gambar 2.29 Karakteristik ideal BPF [20]

Gambar 2.29 merupakan karakteristik ideal BPF. Ada dua area pada filter

pada karakteristik ideal yaitu:

1. Pass Band, rentang frekuensi yang dilewatkan (ditunjukkan dengan nilai

satu)

2. Stop Band, rentang frekuensi yang ditolak (ditunjukkan dengan nilai nol).

Gambar 2.30 merupakan rangkaian BPF aktif 2 pole dengan komponen ternormalisasi satu.

Gambar 2.30 Rangkaian dasar BPF [20]

Untuk merancang BPF digunakan prosedur penskalaan frekuensi

(Frequency scaling) dan penskalaan impedansi (Impedance Scaling) yang dinyatakan dengan [20]:

r

ω = frekuensi referensi pada rancangan ternormalisasi

r r r

r f

f K

ω π ω

ω 2

= =

(2.36)

a. bisa fc untuk tapis pelewat rendah dan tapis pelewat

tinggi, atau fo untuk BPF dan BRF (Band Reject Filter). b. biasanya bernilai 1 rad/dt.

r

ω = frekuensi referensi pada rancangan aktual

Setelah Kf diketahui, maka hal-hal yang perlu dilakukan yaitu:

1. nilai R/C diubah dengan faktor Kf (kali / bagi).

2. Jika frekuensi pada rancangan aktual lebih tinggi, maka R/C

dibagi Kf.

Nilai Cbasicdinyatakan dengan

f sasi ternormali basic

K C

C = (2.37)

2. Konstanta Penskalaan Impedansi (Kr)

Kr = Level Impedansi pada Rangkaian Aktual

Level Impedansi pada Rangkaian Ternormalisasi (2.38)

sasi ternormali

aktual r

R R K =

Nilai Caktual dinyatakan dengan

r basic aktual

K C

Tanggapan amplitudo M(ω) pada rangkaian BPF dinyatakan dengan 2 0 0 2 0 1 ) ( ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − + = ω f f f f Q M M (2.40)

dengan M0 adalah penguatan maksimum dalam bidang frekuensi dan f0 sering

disebut dengan frekuensi pusat geometris (geometric center frequency). Parameter Q adalah ukuran selektifitas atau ketajaman suatu filter. Disarankan nilai Q tidak lebih dari 20.

Tanggapan relatif (dalam decibel),MdB(ω) dinyatakan dengan

⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎣ ⎡ ⎟⎟ ⎠ ⎞ ⎜⎜ ⎝ ⎛ − + − = ω 2 0 0 2 1 log 10 ) ( f f f f Q

MdB (2.41)

Gambar 2.31 Kurva tanggapan BPF [20]

Gambar 2.31 menunjukkan kurva tanggapan BPF. Dari gambar

menunjukkan bahwa BPF memiliki frekuensi pusat (fo).Sedangkan BW pada BPF

merupakan selisih antara frekuensi tinggi (f2) dan rendah (f1). Jika f1 dan f2

menyatakan frekuensi tinggi dan rendah yang mempunyai tanggapan 1 2 kali

BW = f2 – f1 (2.42)

Parameter Q berhubungan dengan frekuensi pusat dan BW dinyatakan dengan

BW f

Q= 0

(2.43)

Jika Q meningkat, maka tapis semakin selektif. Artinya BW yang dibatasi

BAB III

PERANCANGAN

Perancangan pada modulator QPSK ini akan dibagi dalam beberapa

bagian, yaitu menentukan diagram blok yang digunakan, menjelaskan tentang

cara kerja dari diagram blok, dan menentukan komponen rangkaian yang akan

digunakan. Diagram blok modulator QPSK mengacu pada Gambar (2.7).

Multivibrator yang menggunakan IC LM555 berfungsi untuk membangkitkan pulsa digital. Kemudian data digital masuk melalui pencacah

digital modulo-4. Keluaran dari pencacah digital dihubungkan ke rangkaian kode

Grey agar data digital yang masuk hanya berbeda 1 bit untuk setiap perubahan

data. Keluaran pada kode Grey dimasukkan ke PISO, lalu keluaran PISO

dimasukkan ke SIPO. Data digital kemudian diumpankan serempak secara paralel.

Setiap bit akan diumpankan ke kanal yang berbeda. Bit yang satu menuju ke kanal

I dan bit yang lainnya menuju ke kanal Q. Bit-bit digital akan diubah dari bentuk

NRZ unipolar ke bipolar yaitu logic 0 = –1V dan logic 1 = +1V dengan menggunakan komparator. Data – data digital ini merupakan sinyal pemodulasi.

Kanal I memiliki perbedaan fasa sebesar 90° dari kanal Q. Integrator digunakan

untuk membedakan fasa. Setiap sinyal pemodulasi yang ada di kanal I maupun Q

masing-masing akan dikalikan dengan frekuensi carrier dengan menggunakan

balance modulator. Frekuensi carrier dibangkitkan oleh osilator. Keluaran dari

balance modulator dari kanal I maupun dari kanal Q secara serempak akan

dijumlahkan. Kemudian hasil penjumlahan akan di tapis dengan menggunakan

BPF.

3.1

Multivibrator

Dari Gambar (2.10) terlihat bahwa multivibrator memiliki 2 resistor yaitu RA dan RB serta kapasitor yang dipasang secara eksternal dari IC LM 555.

Resistor RA dan RB mempengaruhi waktu pengisian (waktu keluaran tinggi) dan

hanya R

B

B yang mempengaruhi waktu pengosongan (waktu keluaran rendah).

Perancangan multivibrator menggunakan duty cycle sebesar 50%, agar nilai ttinggi sama dengan trendah. Untuk menghasilkan duty cycle sebesar 50%

digunakan sebuah dioda yang paralel dengan RB. Pada kondisi dioda ideal, RA =

RB. Tetapi pada prakteknya, RB lebih besar dari RA.

Perancangan pada modulator QPSK memiliki kecepatan data sebesar

20Kbps atau frekuensi sebesar 10kHz untuk 2 bit data. Tetapi sebelum masuk ke

rangkaian SIPO, frekuensi pada multivibrator harus dua kali lebih besar dari

frekuensi 10kHz. Sehingga frekuensi pada multivibrator dirancang sebesar 20kHz. Periode multivibrator dinyatakan dengan

f

T = 1 (3.1)

3

10 20

1 × =

T

= 50us

T = t tinggi + t rendah (3.2)

Pada perancangan duty cycle ditentukan sebesar 50%, sehingga diperoleh

Ttinggi = 25uS dan Trendah = 25uS. Untuk memperoleh duty cycle sebesar 50% maka

dipasang sebuah diode yang paralel dengan RB. C1 diisi melalui RA dan melalui

diode, tapi dikosongkan melalui RB. Perhitungan resistor (RA) saat duty cycle 50%

dengan Ttinggi = 25uS dan asumsi C1 = 3,3x10-9F (karena lebih mudah diperoleh di

pasaran) dinyatakan dengan

t tinggi = ln2xRAxC (3.3)

25uS = 0,693xRAx3,3x10-9

2,29x10-9 RA = 25uS

RA = 10,90 kΩ

Pada prakteknya dipilih RA = 6,8kΩ diseri dengan 680Ω, karena secara

praktek RA ≠ RB. Sedangkan nilai RB saat duty cycle sebesar 50% mengacu pada

persamaan (2.16), dinyatakan dengan

t rendah = ln2xRBxC

25us = 0,693xRBx3,3x10-9

2,29x10-9RB = 25us

RB = 10,90 kΩ

Gambar 3.1 menunjukkan rangkaian multivibrator astabil dengan duty

cycle 50% .

Gambar 3.1 Rangkaian multivibrator astabil

Gambar 3.2 menunjukkan sinyal keluaran hasil simulasi rangkaian

multivibrator astabil.

3.2 Pencacah

Asinkron

Modulo-4

Rangkaian pencacah menggunakan IC TTL 74LS76. Flip-flop JK 74LS76

merupakan flip-flop yang menggunakan picuan pulsa negatif. Data pada keluaran

akan berubah pada transisi tinggi ke rendah dari pulsa clock. Rangkaian akan

mencacah dari 00, 01, 10, 11 dan kemudian kembali lagi ke 00. Gambar 3.3

menunjukkan rangkaian pencacah modulo-4 dengan menggunakan IC TTL

74LS76, dan Tabel 3.1. menunjukkan tabel kebenaran untuk IC 74LS76.

QA

QB

CLK CLR VCC

U2 7476

J1 CLK1 PRN1 CLRN1 K1

Q1

QN1 J2

CLK2 PRN2 CLRN2 K2

Q2

QN2

Gambar 3.3 Rangkaian pencacah asinkron modulo-4

Baris satu sampai tiga menjelaskan masukan set asinkron yaitu preset dan

clear. Masukan sinkron diabaikan pada tiga baris pertama. Tanda ‘X’ berarti larangan yang terjadi bila kedua masukan asinkron diaktifkan pada masukan yang

sama. Baris 4 sampai 7 menjelaskan kondisi masukan sinkron untuk mode tetap,

reset, set, dan togel dari flip-flop JK.

3.3

Kode Grey

Pada perancangan ini, rangkaian untuk kode Grey menggunakan IC TTL

74LS86 sebanyak 1 buah.

Tabel 3.2 Tabel Kebenaran IC 74LS86 [11]

Tabel 3.2. menunjukkan tabel kebenaran untuk IC 74LS86. Keluaran IC

akan bernilai 1 apabila masukan A dan B berbeda. Tetapi apabila masukan

bernilai sama, maka keluaran dari IC akan bernilai 0.

Rangkaian pengubah kode biner ke kode Grey mengacu pada Gambar

(2.14). Untuk mengubah data sebanyak 2 bit, diperlukan rangkaian XOR

Tabel 3.3 Keluaran rangkaian kode Grey

Tabel 3.3 menunjukkan keluaran dari rangkaian pengubah bilangan biner

menjadi kode Grey. Dari hasil pengubahan bilangan biner menjadi kode Grey

diperoleh suatu keluaran biner yang hanya memiliki perubahan sebesar 1 bit.

3.4. Register

PISO

Perancangan register PISO menggunakan flip-flop data. Gambar 3.4

menunjukkan rangkaian register PISO .

W/S D1 D0 CLR CLK Out VCC U3 NAND2 U1 NAND2 U10 7474 D1 CLK1 PRN1 CLRN1 Q1 QN1 D2 CLK2 PRN2 CLRN2 Q2 QN2 U4 NAND2 U6 7476 J1 CLK1 PRN1 CLRN1 K1 Q1 QN1 J2 CLK2 PRN2 CLRN2 K2 Q2 QN2 U2 NAND2 U7 INV

Data masukan yaitu D0 dan D1 masuk serentak secara paralel. D0 masuk

ke flip-flop data yang pertama dan D1 masuk ke flip-flop data yang kedua. Pada

perancangan terdapat flip-flop JK yang terpasang secara toogle, yaitu masukan J dan K diberi masukan 1. Flip-flop JK berfungsi sebagai W/S (write/shift) yaitu

kondisi yang menunjukkan flip-flop data menulis atau menggeser. Jika kondisi

logika masukan rendah, maka flip-flop data berada pada kondisi write (menulis).

Tetapi jika kondisi logika masukan tinggi, maka flip-flop data berada pada kondisi

shift (menggeser).

0ns 500ns 1000ns 1500ns 2000ns 2500ns 3000ns 3500ns 4000ns 4500ns 5000ns

SCHEMATIC1 Context CLK Signal '0' Value SCHEMATIC1 Context CLR Signal '1' Value SCHEMATIC1 Context VCC Signal '1' Value SCHEMATIC1 Context D0 Signal '1' Value SCHEMATIC1 Context D1 Signal '1' Value SCHEMATIC1 Context OUT Signal '0' Value

Gambar 3.5 Timing diagram rangkaian register PISO

Gambar 3.5 menunjukkan timing diagram dari rangkaian register PISO. D0 merupakan LSB (least significant bit), dan D1 merupakan MSB (most

significant bit). Ketika W/S berada pada kondisi logika tinggi maka flip-flop data akan menggeser, sehingga D1 akan keluar. Pada clock berikutnya maka D0 akan keluar.

Rangkaian modulator QPSK memiliki masukan sebesar 20kbps dengan

Gambar 3.6 Perioda pada register PISO

Perioda pada register PISO ditunjukkan pada Gambar 3.6. Karena clock

pada multivibrator sebesar 50uS (Ton = 25us dan Toff = 25uS), maka perioda register SIPO sebesar 400uS atau 2,5kHz yang untuk 8 bit data. Sedangkan

perioda untuk setiap 2 data yaitu 00,01,11,10 sebesar 100uS.

3.5

Register SIPO

Perancangan register SIPO menggunakan flip-flop data yang dirangkai

secara terpisah. Gambar 3.7 menunjukkan rangkaian register SIPO dengan

menggunakan IC 74LS74.

Ketika pulsa clock (CLK) datang pada periode pertama, maka keluaran O1

akan mengikuti masukan data (IN) yang pertama. Kemudian saat clock datang pada periode yang kedua, keluaran dari O1 akan bergeser ke flip-flop data yang

kedua (U2) sehingga mneghasilkan keluaran O2. Lalu masukan data yang kedua

akan masuk ke flipflop data yang pertama (U1) dan menghasilkan keluaran O1.

Keluaran O1 akan diteruskan ke flipflop data yang ketiga (U3) dan menghasilkan

keluaran q1. Sedangkan keluaran O2 akan diteruskan masuk menuju ke flip-flop

data yang keempat (U4), sehingga menghasilkan keluaran q2. Pada saat bersamaan

keluaran dari q1 dan q2 akan dikeluarkan paralel secara serentak.

Pada perancangan SIPO dengan menggunakan flip-flop data, terdapat

sebuah flip-flop JK. Flip-flop JK berfungsi sebagai pembagi frekuensi. Frekuensi

pemodulasi yang diinginkan sebesar 10kHz, sehingga frekuensi yang masuk pada

rangkaian SIPO harus bernilai 2 kali lebih besar dari frekuensi pemodulasi yaitu

20kHz. Oleh karena itu, frekuensi pada multivibrator dirancang sebesar 20kHz.

Flip-flop JK kemudian akan membagi frekuensi dari multivibrator yaitu 20kHz, sehingga menghasilkan frekuensi pemodulasi yang diinginkan. IC 74LS74 yang

pertama (terletak di samping flip-flop JK), digunakan untuk memasukkan data.

Kemudian IC 74LS74 yang kedua digunakan untuk mengeluarkan data secara

Gambar 3.8 Timing diagram hasil keluaran rangkaian register SIPO

Timing diagram hasil keluaran dari rangkaian register SIPO ditunjukkan pada Gambar 3.8 sedangkan perioda untuk setiap 2 bit data saat 00, 01, 11, 10

yang ditunjukkan pada Gambar 3.9 yaitu sebesar 100uS. Periode untuk 1 bit yaitu

50uS dengan kecepatan transfer data 20kbps.

Gambar 3.9 Perioda pada register SIPO

3.6 Komparator

Komparator non inverting digunakan untuk mengubah logic 1 = +1V dan

logic 1 dan logic 0 pada pencacah digital. Perancangan komparator non inverting

mengacu pada Gambar (2.18). Tegangan referensi bernilai 1,5V yang bernilai

setengah dari tegangan masukan, diperoleh dari hasil pembagi tegangan. Gambar

3.10 menunjukkan hasil simulasi pembagi tegangan.

Gambar 3.10 Hasil simulasi pembagi tegangan

in

ref V

R R

R

V ×

+ =

2 1

2

(3.3)

3

10 10 10 10

10 10

![Tabel 2.1 Tabel kebenaran QPSK [10]](https://thumb-ap.123doks.com/thumbv2/123dok/1634247.2067018/31.595.240.357.572.702/tabel-tabel-kebenaran-qpsk.webp)

![Gambar 2.5 Bentuk gelombang tiap bit [10]](https://thumb-ap.123doks.com/thumbv2/123dok/1634247.2067018/32.595.249.375.642.706/gambar-bentuk-gelombang-bit.webp)

![Gambar 2.7 Diagram blok modulator QPSK [10]](https://thumb-ap.123doks.com/thumbv2/123dok/1634247.2067018/33.595.95.535.484.702/gambar-diagram-blok-modulator-qpsk.webp)

![Gambar 2.10 IC LM555 sebagai multivibrator astabil [13]](https://thumb-ap.123doks.com/thumbv2/123dok/1634247.2067018/38.595.219.403.438.603/gambar-ic-lm-sebagai-multivibrator-astabil.webp)

![Gambar 2.11 Flip-flop JK [11]](https://thumb-ap.123doks.com/thumbv2/123dok/1634247.2067018/40.595.238.387.306.353/gambar-flip-flop-jk.webp)

![Tabel 2.2 Tabel kebenaran flip-flop JK [11]](https://thumb-ap.123doks.com/thumbv2/123dok/1634247.2067018/41.595.221.406.562.684/tabel-tabel-kebenaran-flip-flop-jk.webp)

![Tabel 2.3 Perbedaan bilangan biner dengan kode Grey [17]](https://thumb-ap.123doks.com/thumbv2/123dok/1634247.2067018/42.595.226.400.285.358/tabel-perbedaan-bilangan-biner-dengan-kode-grey.webp)

![Gambar 2.20 Rangkaian komparator non inverting [20]](https://thumb-ap.123doks.com/thumbv2/123dok/1634247.2067018/48.595.256.360.451.518/gambar-rangkaian-komparator-non-inverting.webp)

![Gambar 2.21 Kurva karakteristik masukan dan keluaran komparator [20]](https://thumb-ap.123doks.com/thumbv2/123dok/1634247.2067018/49.595.241.382.224.336/gambar-kurva-karakteristik-masukan-keluaran-komparator.webp)