CHƯƠNG TRÌNH DÀNH CHO NGOẠI LỆ – HOẶC CÀI ĐẶT CHƯƠNG TRÌNH ĐỂ NHẬN ĐƯỢC SỰ PHÙ HỢP VÀ YÊU CẦU. Tổng lượng điện năng cần thiết để lập trình SPLD, CPLD hoặc FPGA.

GIÔÙI THIEÄU PLD

- HOAÏT ÑOÄNG CUÛA SPLD CÔ BAÛN LAØ PAL

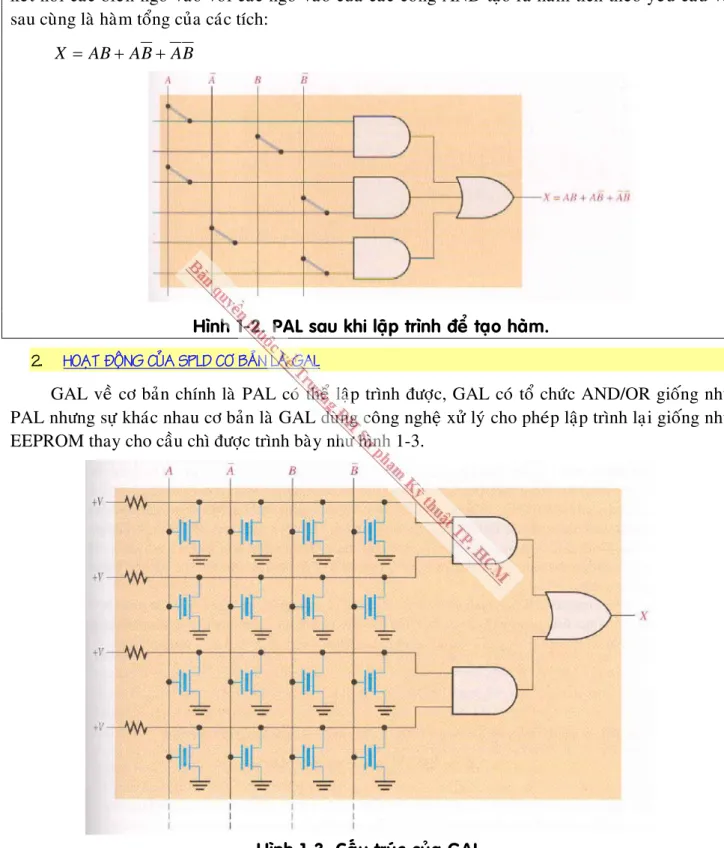

- HOAÏT ÑOÄNG CUÛA SPLD CÔ BAÛN LAØ GAL

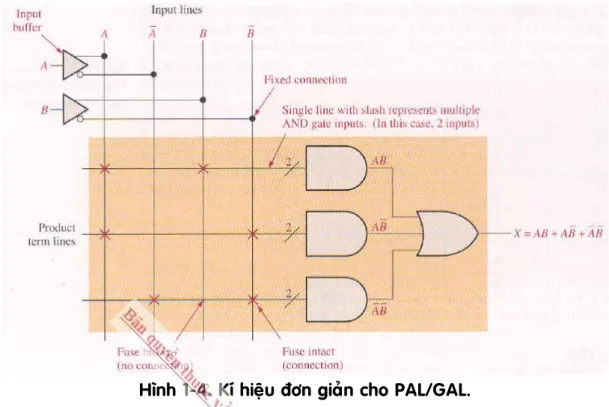

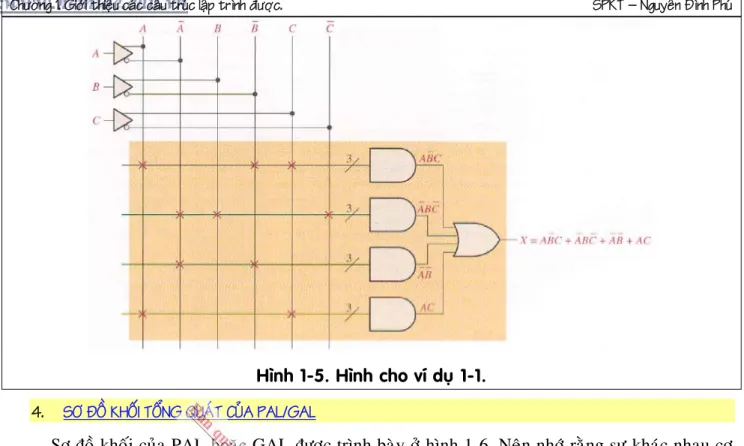

- KÍ HIEÄU ÑÔN GIAÛN CHO SÔ ÑOÀ CUÛA PAL/GAL

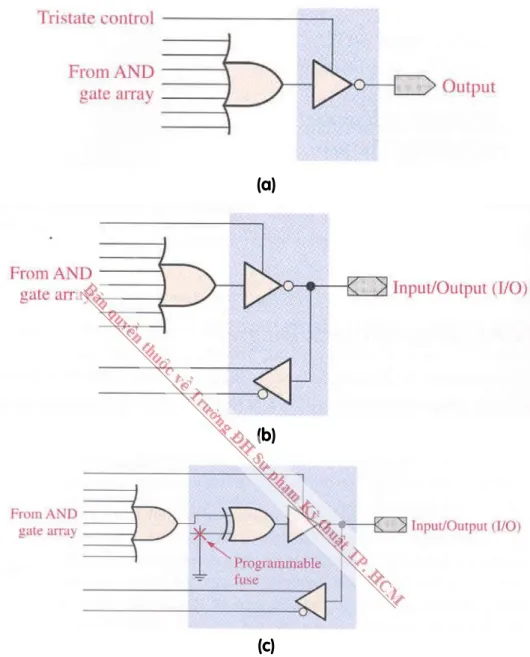

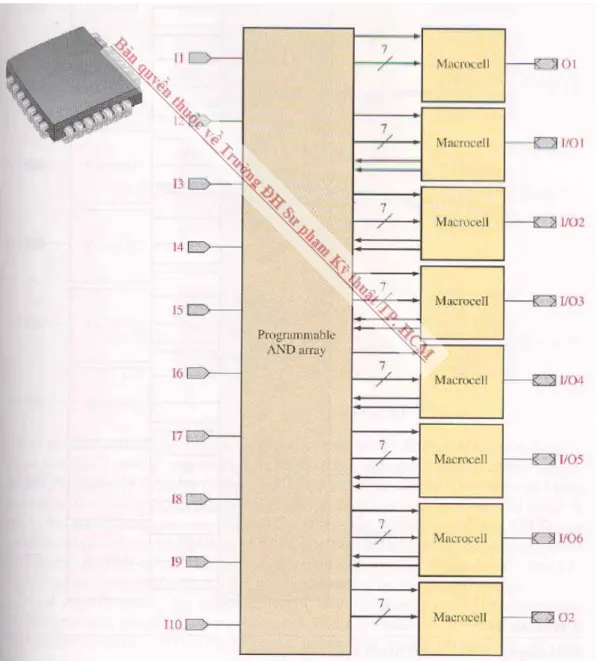

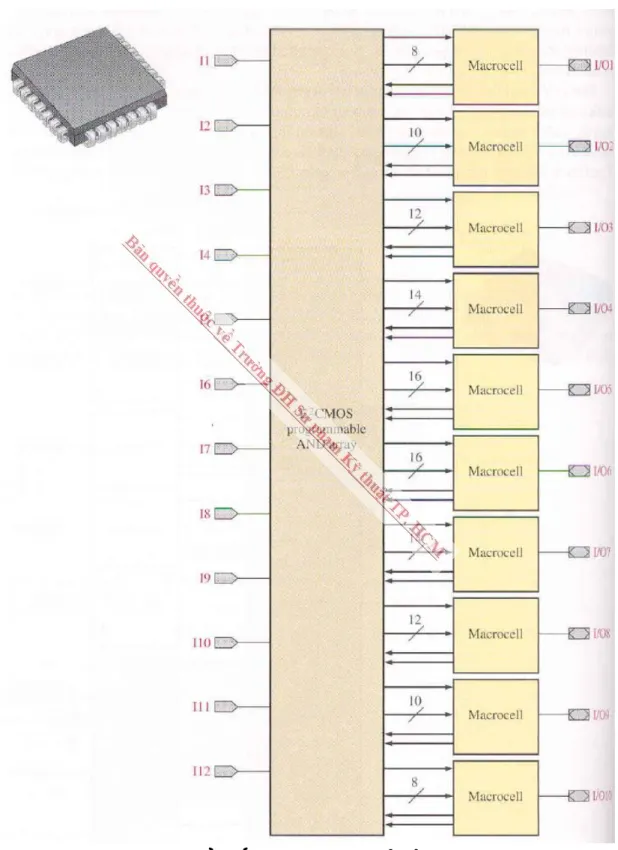

- SÔ ÑOÀ KHOÁI TOÅNG QUAÙT CUÛA PAL/GAL

- MACROCELL

- CAÙC SPLD THÖÏC TEÁ

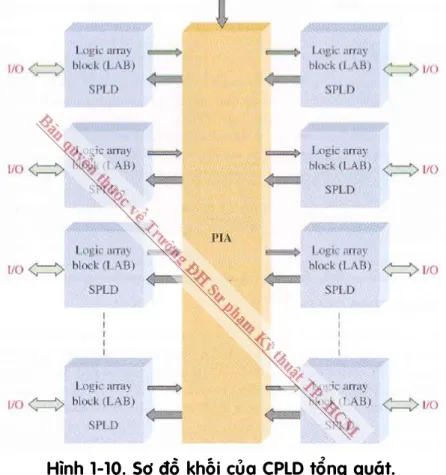

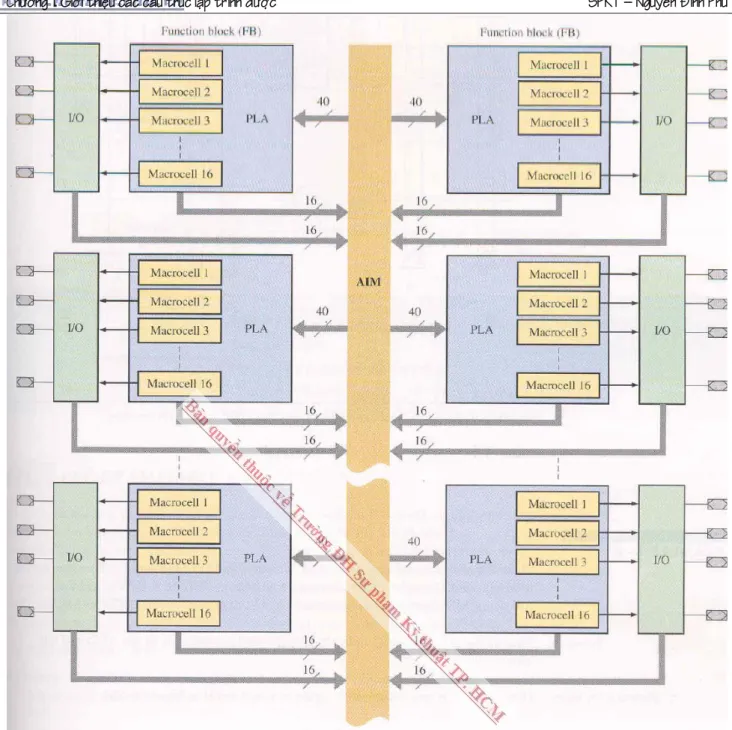

- CAÙC CPLD

Một đầu vào XOR (ex-or) có thể được lập trình ở mức CAO hoặc THẤP. Mỗi macrocell có 8 đầu vào mang đường cong AND nên có 8 dải phân tích cho mỗi đầu ra.

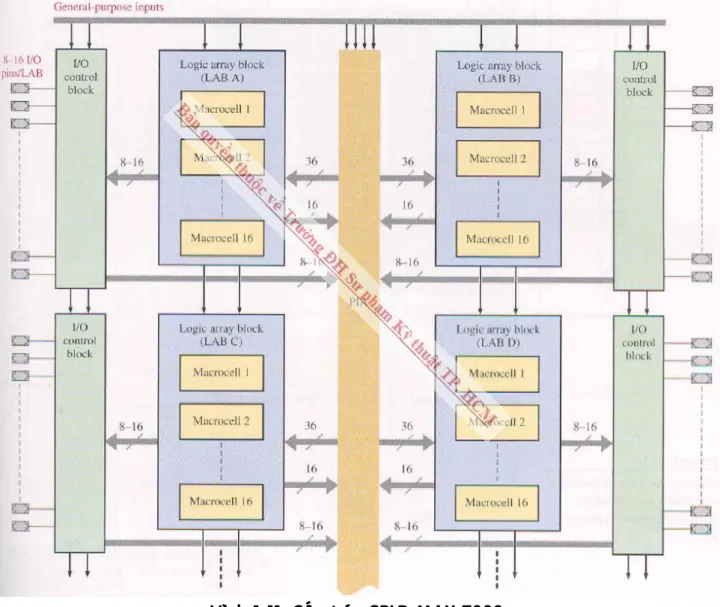

CPLD CUÛA HAÕNG ALTERA

- CPLD MAX 7000

- MACROCELL

- KHOÁI MÔÛ ROÄNG CHIA SEÛ

- KHOÁI MÔÛ ROÄNG SONG SONG

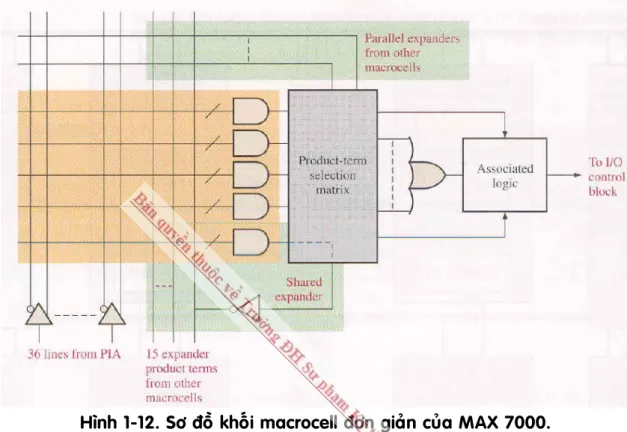

- CPLD MAX II

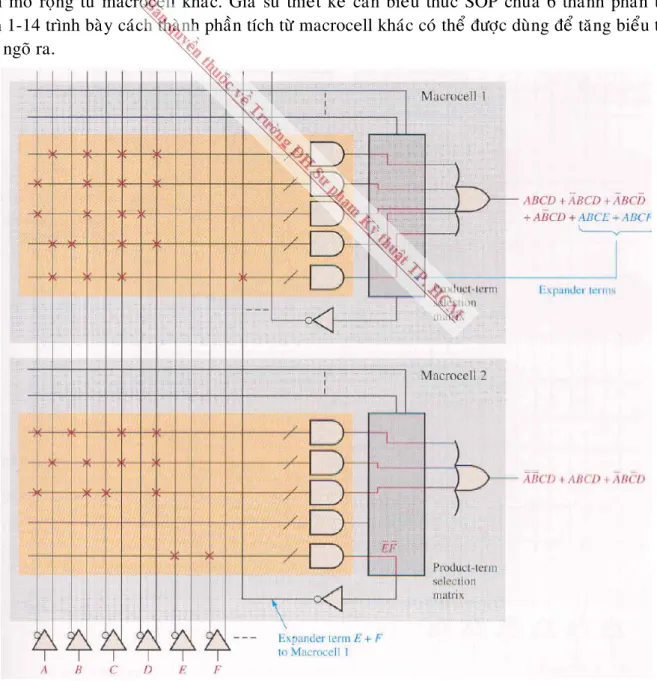

Trong Hình 1-12, có 5 đường cong AND tạo ra các thanh tích phân từ PIA trong ma trận bộ chọn chất phân tích. Các đầu vào mô hình song song cho phép các thanh phân tích không được sử dụng bởi các macrocell khác để mô phỏng mẫu SOP. Mỗi macrocell của MAX 7000 có thể tạo ra 5 thanh phân tích với đường cong EN.

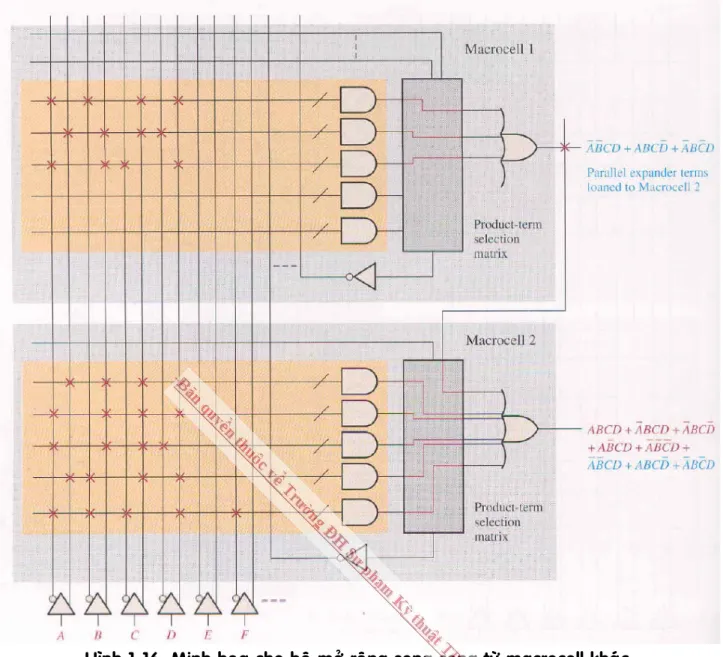

15 Enemy Macrocell 2 tạo ra một nguyên tố chung phổ biến (E+F) được dự đoán bởi IN số 5 trong Enemy Macrocell 1 để tạo ra một mẫu chất phân tích SOP 6. Macrocell cho phép nhiều chất phân tích nhất có thể, điều mà macrocell thay thế không thể sử dụng (có thể thu được tối đa 5 macrocell khác nhau từ MAX 7000). Macrocell loại thứ hai sử dụng ba dòng phân tích từ macrocell loại thứ nhất để tạo mẫu SOP tám thanh.

CPLD CUÛA HAÕNG XILINX

PLA (PROGRAMMABLE LOGIC ARRAY)

Ví dụ: CPLD MAX II có phương pháp sao chép đầu ra của các kết nối bên trong thay vì loại kết nối bên trong được tìm thấy trong CPLD. Tất cả các CPLD đều sử dụng giải pháp điểm chương trình liên tục. Tuy nhiên, MAX II sử dụng bộ xử lý như SRAM, vì vậy nó có thể bay xa - tất cả logic được lập trình sẽ nguội đi khi nó nóng.

Bo mạch được lắp vào chip để lưu trữ dữ liệu chương trình cố định và để tạo hình dạng mới cho CPLD khi được cấp nguồn. Như được hiển thị, PAL có thể mang một đường cong thủ tục AND theo sau bởi một đường cong OR được chỉ định để tạo ra các mẫu SOP như trong Hình 1-20a. PLA có sóng mang AND có lập trình và được theo sau bởi sóng mang OR có lập trình như trong Hình 1-20b.

COOLRUNNER II

Kết quả CPLD của Xilinx và CPLD của Altera gần như giống hệt nhau, nhưng bên trong chúng khác nhau. Vì có 16 macrocell cho mỗi chức năng nên số lượng thỏa mãn chức năng thay đổi từ 2 đến 32. Giữ một đường AND có 56 đường AND và giữ một đường OR sẽ cho 16 đường OR.

Với mô hình PLA, bất kỳ phân tích nào cũng có thể được thực hiện với đường cong OR để tạo định dạng SOP cho đầu ra. Với mỗi chức năng, mỗi chức năng có thể tạo ra 16 đầu ra và mỗi đầu ra có định dạng SOP gồm 56 kết quả phân tích. Ví dụ 1-2: Hãy lập trình hàm FB của Hình 1-22 để tạo hàm SOP cho macrocell đầu tiên: ABCD+ABCD+ABCD và cho macrocell thứ hai::.

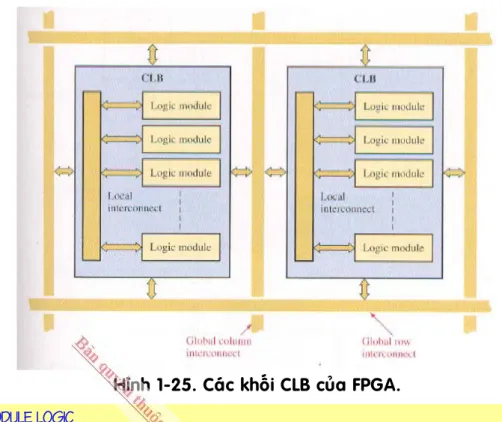

LOGIC LAÄP TRÌNH FPGA

- CAÙC KHOÁI LOGIC COÙ THEÅ ÑÒNH CAÁU HÌNH CLB

- CAÙC MODULE LOGIC

- FPGA DUØNG COÂNG NGHEÄ SRAM

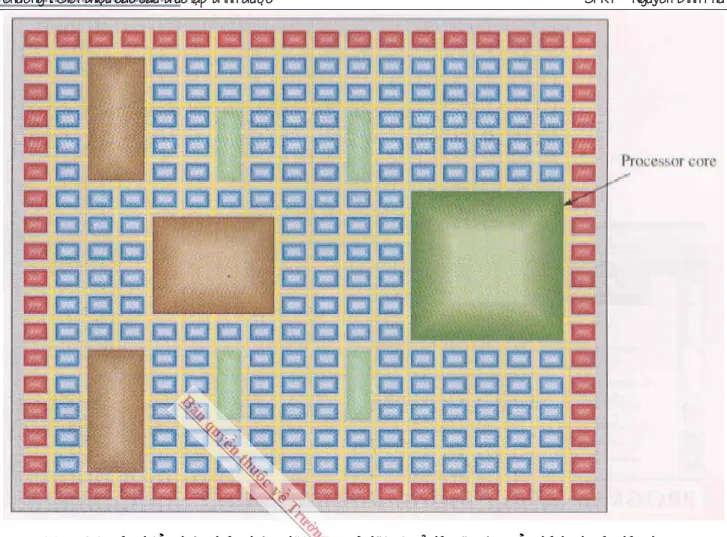

- CAÙC LOÕI CUÛA FPGA

Trình phân loại các nút bên trong quy trình tạo ra các nút trong câu lạc bộ và xác định đầu vào và đầu ra. FPGA là một FPGA có thể lập trình lại và sử dụng SRAM hoặc xử lý nóng chảy để lập trình các nút. Có thể nhập mẫu 1 và 0 vào LUT như minh họa trong Hình 1-27 để tạo chức năng SOP được chỉ định.

FPGA và các FPGA khởi động tương tự như các bo mạch có thể lập trình cho người dùng đối với các thiết kế logic. Ví dụ, nếu một khách hàng có một vấn đề nhỏ như một phần của dự án ngoài trời, nó có thể được đưa vào FPGA để khách hàng có thể tham gia. Nếu các chức năng được tích hợp vào các chức năng của chương trình, thì chúng được coi là các chức năng "lõi mềm".

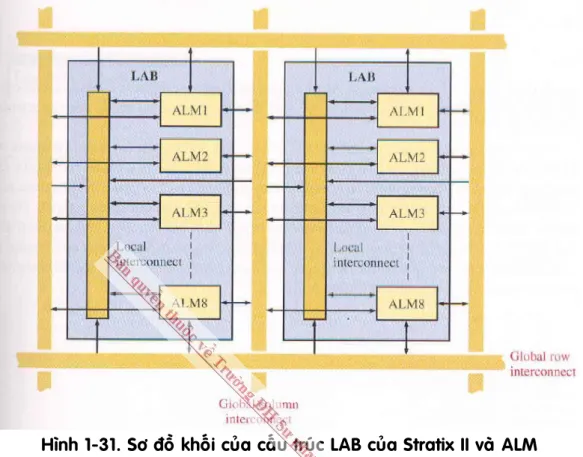

FPGA CUÛA ALTERA

KHOÁI MAÛNG LOGIC (LAB – LOGIC ARRAY BLOCK)

27 Ưu điểm lớn của phương pháp là nó giống hệt với những gì được xác định trong quá trình tạo và khách hàng phải được sử dụng bởi phương pháp. Các phần tử cùng pha thường được sử dụng cho các chức năng phổ biến được sử dụng trong quá độ như bộ xử lý, giao diện đầu vào/đầu ra và xử lý tín hiệu. Các loại giai đoạn tương tự thường được xây dựng bằng cách sử dụng nhà sản xuất FPGA và mã riêng của nhà sản xuất.

Nhiều người trí thức là sự kết hợp của cùng một nhóm và nhóm. Các FPGA được tích hợp bộ vi xử lý của một trong hai hay nhiều loại giống và khác nhau về chức năng và chức năng được công nhận là nền tảng FPGA mới vì chúng có thể trích xuất lưu vong, không cần thêm bất kỳ hình thức hỗ trợ nào. Một ALM có thể thực hiện một hoặc hai chức năng đầu ra kết hợp với hai LUT của nó.

CAÙC CHÖÙC NAÊNG TÍCH HÔÏP

Toán tử AND - OR với đầu vào là một ví dụ điển hình của hoạt động kênh. Ví dụ 1-4: Một ALM trong Stratix II FPGA được gọi là LUT mô hình đang được điều khiển trong Hình 1-35. Giai đoạn: Đối với định dạng đầu ra của ô trên cùng, đầu vào AND là A0 và đối với định dạng đầu ra dưới cùng, AND là A0.

FPGA chứa các thành phần chính và chức năng xử lý tín hiệu DSP. Các chức năng DSP như mã hóa thường được sử dụng trong không gian mở. Khi xem niềm vui, niềm vui tích hợp được sao chép vào ma trận bên trong của FPGA và các đầu vào/đầu ra được đặt xung quanh chu vi của FPGA.

FPGA CUÛA XILINX

CAÙC KHOÁI LOGIC COÙ THEÅ ÑÒNH CAÁU HÌNH CLB (CONFIGURABLE LOGIC BLOCK)

Công suất tích hợp nằm trong khoảng từ 2000 đến 74000 tế bào logic LC trong một đơn vị Virtex. Minh họa các cáp logic xác định đường bao logic của câu lạc bộ.

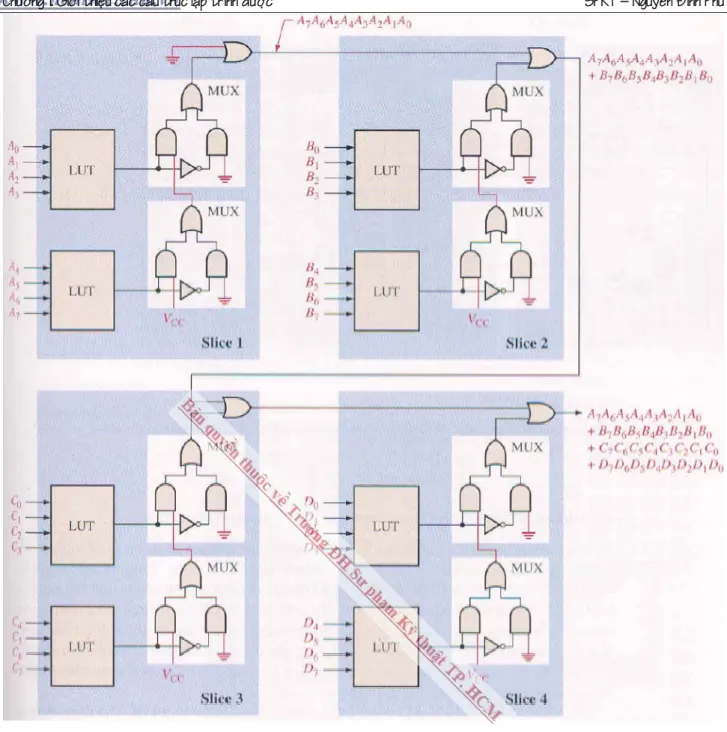

CHUOÃI LIEÂN TIEÁP SOP

33 Hình 1-38a cho thấy một ví dụ về cách một đoạn trong CLB có thể được cấu hình như một đường cong AND để tạo ra một phép tính đếm 8. Hai phân đoạn có thể được cấu hình để tạo ra chức năng SOP với hai phép tính 8 số đếm được minh họa trong Hình 1-38b. Bảng câu lạc bộ của 4 phân đoạn có thể được định nghĩa như một chuỗi nối để tạo ra hàm SOP với 4 tích phân có 8 số được trình bày như Hình 1-38c.

Hình thức SOP dài hạn có thể được thực hiện bởi các câu lạc bộ địa phương. Ví dụ 1-5: Hãy hiển thị một phương thức AND với 16 đầu vào có thể tạo ra một mẫu câu lạc bộ. Pha: Hai lát cắt xác định được biểu diễn trong Hình 1-39 dưới dạng giao điểm của một đường cong AND với 16 đầu vào.

CAÁU TRUÙC FPGA TRUYEÀN THOÁNG VAØ CAÁU TRUÙC ASMBL a. Caáu truùc truyeàn thoáng

LINH HOẠT NỀN TẢNG FPGA VÀ ASMBL a.c) FPGA có nhiều loại card, nhân DSP và nhân xử lý sẽ có kích thước lô nhỏ hơn. Mỗi bảng là một chuỗi logic có thể được thay thế bằng một chuỗi logic khác mà không thay đổi cách bố trí chip. Việc phân biệt từng loại logic có thể được thực hiện trong tương lai để phù hợp với yêu cầu sử dụng cụ thể.

Nhiều hay ít cuộc hôn nhân của hai người đàn ông có thể được sử dụng tùy theo yêu cầu. 37 Nếu có nhiều hơn một số thì có thể thay đổi một hoặc nhiều chiều dài gậy như hình 1-41b. Nếu khu vực đang sử dụng là bộ xử lý tín hiệu số, các lớp IP DSP có thể được thêm vào bảng như trong Hình 1-41c.

PHAÀN MEÀM LAÄP TRÌNH

- CAÙCH THIEÁT KEÁ

- MOÂ PHOÛNG CHÖÙC NAÊNG

- TOÅNG HÔÏP

- LIEÄT KEÂ LÖÔÙI (NETLIST)

- PHAÀN MEÀM THI HAØNH

- MOÂ PHOÛNG THÔØI GIAN

- LAÄP TRÌNH CHO THIEÁT BÒ – HAY NAÏP CHÖÔNG TRÌNH CHO THIEÁT BÒ

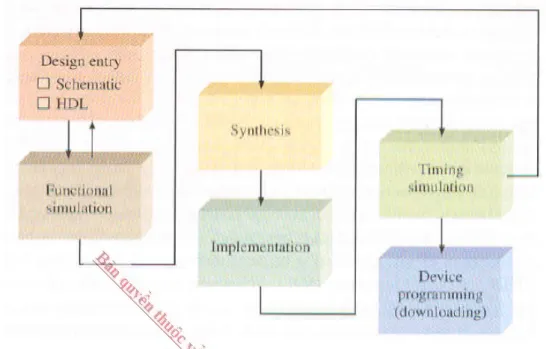

Quá trình lập kế hoạch được gọi là quy trình lập kế hoạch. Môi trường thực hiện được sử dụng để thực hiện logic cho chương trình bay, như trong Hình 1-42. Sử dụng đầu ra Z của ví dụ này để có được kết quả tương tự. Đừng ngại.

Logic AND-OR đã được cấu hình ở trên hiển thị trong Hình 1-50a có thể được chuyển đổi thành Hiển thị 1-50b. Giai đoạn thiết kế sử dụng thông tin quy trình như thời gian trễ của các đường cong để chạy mô hình theo thời gian của dự án. 47 Nếu không có gì được nhập thông qua chế độ trong Hình 1-52a, nó có thể được thêm vào chương trình.

Khi bạn đã kiểm tra chế độ chức năng và chế độ thời gian và thiết bị hoạt động bình thường, bạn có thể tiến hành tải xuống. Sau khi thực hiện xong, thiết kế có thể được kiểm tra bằng phương pháp thử nghiệm.