PERANCANGAN RANGKAIAN ANALOG CMOS MULTIPLIER

1Brahmantyo Heruseto2Hamzah Affandi 3Eri Prasetyo 4Nur Sultan Salahuddin

1,2,3,4Information Technology Study Program, Gunadarma Universiy

Jl. Margonda Raya No. 100 Depok 16424 JAWA BARAT – INDONESIA

(brahm,hamzah,eri,[email protected]) .

ABSTRAK

Pada tulisan ini membahas perancangan rangkaian analog CMOS Multiplier sebagai rangkaian synapse yang merupakan bagian penelitian pembuatan rangkaian analog Jaringan Syaraf Tiruan menggunakan CMOS. Rangkaian Multiplier yang dibuat menggunakan dasar dari rangkaian four quadrant multiplier yang telah dirancang oleh Gilbert[Gilbert,1974]

Kata Kunci: Multiplier,Four Quadrant, Analog CMOS

1. PENDAHULUAN

Perkembangan teknologi komputer saat ini sudah sangat berkembang dengan pesat dalam membantu pekerjaan manusia sehari-hari. Walaupun demikian, dalam banyak hal otak manusia masih lebih unggul dibandingkan komputer. Contoh yang paling baik adalah dalam pemrosesan visual. Jika dapat dibuat bagian terkecil saja dari arsitektur otak manusia maka akan dapat dibuat komputer yang mempunyai kekuatan proses yang sangat hebat. Kemajuan Model Jaringan Syaraf Buatan mendapat perhatian yang semakin baik akhir-akhir ini. Model-model ini merupakan gambaran dari sistem syaraf otak manusia. Sebagai contoh penggunaan “neuron” dan “synapse” yang dapat

ditemukan dalam sistem otak dan jaringan syaraf manusia.

Fungsi dari Jaringan Syaraf Tiruan diharapkan dapat mengaplikasikan kemampuan pengenalan citra, suara dan fungsi-fungsi yang sejenis sesuai dengan kemampuan yang dimiliki manusia. Banyak dari perkembangan model tersebut diimplementasi-kan menggunakan komputer digital. Perkembangan terakhir dalam ketertarikan penggunaan model ini juga melihat perkembangan teknologi komputer yang sangat cepat. Beberapa hal yang menjadi keter-tarikan menggunakan jaringan syaraf dapat dilihat dari berbagai aspek, diantaranya : [Sigvartsen,1994]

• Adaptif : dapat menyesuaikan diri dengan “belajar” dari data terbaru.

• General : dapat menggolongkan data mana yang telah “belajar”.

• Mampu menangani data yang tidak sempurna atau tidak lengkap, dengan meyediakan tingkatan toleransi kesalahan.

• Non-linear : dapat menangkap keter-hubungan kompleksitas yang besar.

Penelitian Jaringan Syaraf Tiruan dapat dikembangkan dengan sistem analog maupun digital, bahkan dapat digabungkan diantara kedua-nya. Dalam penelitian ini akan membahas peng-gunaan Jaringan Syaraf Tiruan menggunakan sistem analog. Beberapa pendapat yang menyatakan sistem analog lebih mempunyai keunggulan. Hal ini dapat dijelaskan sebagai berikut : [Sigvartsen,1994]

• Dalam sistem analog (dan Jaringan Syaraf Tiruan), tingkatan yang tinggi dari toleransi ke-salahan digunakan jika tidak menyebabkan kesalahan yang kritis bila beberapa transistor tidak berfungsi. Hal ini tidak dapat dilakukan pada sistem digital.

• Dimungkinkan untuk membuat

rangkaian yang mengaplikasikan kemampuan proses komputasi yang luar biasa dibandingkan dengan ukuran serta kompleksitasnya. Satu contoh adalah proses komputasi dari fungsi aktifasi (dalam neuron). Rangkain sistem analog yang mem-proses kedua fungsi tersebut hanya mem-butuhkan tujuh transistor dan bila dibandingkan dengan sistem digital maka akan sangat sulit dicapai.

• Penggunaan CMOS analog hanya

membutuh-kan konsumsi daya yang kecil, apalagi jika menggunakan CMOS transistor pada daerah subthreshold.

• Proses kerja sistem otak juga “analog” : Pemrosesan informasi pemahaman dalam sistem biologi menggunakan sinyal analog, sehingga pemrosean sinyal yang efisien pada Jaringan Syaraf Tiruan dapat diperoleh. Sebagai contoh dalam menjumlahkan beberapa synapse untuk input neuron. Ketika menggunaan arus sebagai jenis semua sinyal output , maka hanya memerlukan perkabelan dari berbagai output synapse yang diperlukan

untuk melakukan penjumlan.

Akan tetapi sistem analog tidak tahan terhadap noise, tetapi hal ini tidak berpengaruh untuk Jaringan Syaraf Tiruan. Disamping itu, noise pada Jaringan Syaraf Tiruan dapat digunakan untuk membantu dalam proses learning atau pelatihan [Hertz,1991] [Lehman,1988]

2. TINJAUAN PUSTAKA

Ketika mengimplementasi Jaringan Syaraf Tiruan menggunakan rangkaian analog, terutama perancangan rangkaian synaptic merupakan pekerjaan yang agak rumit karena membutuhkan rangkaian synaptic array yang besar. Biasanya sistem parallel akan terpadu pada silicon die yang sama, sehingga daya rangkaian synaptic sangat berpengaruh menentukan konsumsi keseluruhan chip. Jika N merupakan jumlah dari input atau output neuron jaringan, maka jumlah synapse akan sebanding dengan N2 . Pertimbangan yang sama dapat terjadi pada ukuran (misalnya ukuran area silicon). Pada jaringan feedforward, rangkaian dasar synaptic adalah four-quadrant analog multiplier. Perancangan rangkaian multiplier ini menggunakan CMOS yang mempunyai kelebihan dalam hal mengurangi area silicon yang digunakan. [Selcuk,1999].

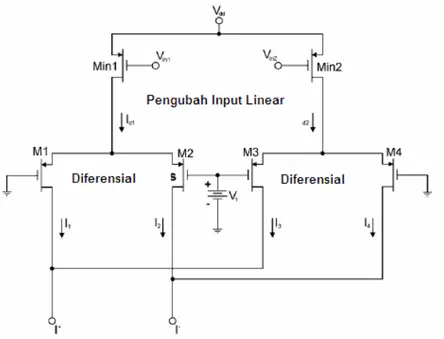

Gambar 1 adalah rangkain dasar four-quadrant transconductance multiplier. Pada

tersebut. Kedua input merupakan input yang mengubah tegangan ke arus dan empat bagian di bawahnya merupakan

perbedaan bobot yang digunakan sebagai pengali arus.

Gambar 1. Gilbert Multiplier Sumber : Gilbert (1974)

3. METODE PENELITIAN

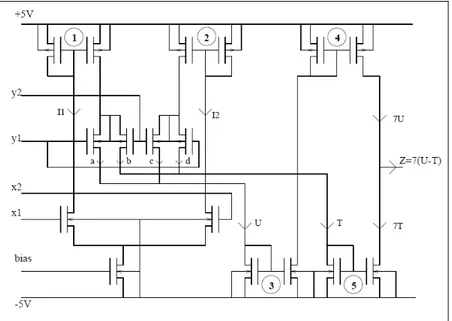

Rangkaian synapse yang merupakan salah satu rangkaian pada Jaringan Syaraf Tiruan dapat dibuat menggunakan rangkaian analog multiplier jika beberapa input dan bobot yang diberikan merupakan tegangan . Rancangan rangkaian synapse pada tulisan ini menggunakan versi modifikasi Gilbert Multiplier yang dapat dilihat pada gambar 2. Input-input berupa perbedaan tegangan dan dilambangkan sebagai (x2 –

x1) dan (y2 – y1). Output yang dihasilkan

oleh rangkaian Gilbert sebelum dimodifikasi adalah perbedaan arus (U-T) dan perbedaan dalam perancangan ini di ubah menjadi arus tunggal (Z) melalui

current mirror. Hal ini akan meningkatkan linearitas dari multiplier dan juga memudahkan menghubungkan dengan rangkaian lain. Dengan menggunakan tegangan sebagai input dan synapse mempunyai output arus akan sangat cocok untuk implementasi menggunakan VLSI karena sinyal yang umumnya berasal dari luar banyak dalam bentuk tegangan dan operasi penjumlahan pada output synapse dapat dilakukan dengan menghubungkan seluruh output synapse secara bersamaan.

Output arus dari synapse dapat diperoleh dengan asumsi bahwa transistor bekerja pada daerah saturasi untuk arus drain ID dari transistor MOS adalah

2 (

2

D GS T)

Dimana β adalah faktor arus, VGS adalah

tegangan gate-to-source dan VT adalah

tegangan threshold. Perbedaan pasangan untuk input Δx = (x2 – x1) menyebabkan

arus I1 dan I2 mengalir melalui pasangan

perbedaan bobot, Δy = (y2-y1), setelah

dicerminkan oleh current mirror 1 dan 2,

Gambar 2. Diagram Rangkaian Synapse 2 2 1 2 2 2 2 x x SS x x I I β β ⎛ ⎞ − Δ + Δ + ⎜ ⎟ ⎜ ⎟ = ⎜ ⎟ ⎜ ⎟ ⎝ ⎠ (2) 2 2 2 2 2 2 2 x x SS x x I I β β ⎛ ⎞ Δ + Δ + ⎜ ⎟ ⎜ ⎟ = ⎜ ⎟ ⎜ ⎟ ⎝ ⎠ (3) Dimana βx adalah faktor arus dari

pasangan perbedaan input dan Iss adalah

arus bias. Perbedaan arus I1 - I2 dapat

disederhanakan menjadi 1 2 x SS I − = −I β I Δx (4) Jika 2 2 x x β

Δ dapat diabaikan berkenaan dengan 2Iss. Perbedaan arus ini akan

menjadi arus bias untuk pasangan

perbedaan bobot. Oleh karena itu, perbedaan arus a-b dan c-d terbentuk dari pasangan perbedaan bobot dan dapat mendekati

1 y a b− = β I Δy (5) 2 y c− = −d β I Δy (6)

(

1 2)

(a c+ − +) (b d)= βyΔy I − I (7)Dari perhitungan U – T = (a+c)-(b+d) dapat ditulis kembali menggunakan (2) dan (3) menjadi

2 x y

U − = −T β β Δ Δx y (8)

Arus U dan T dikalikan dengan tujuh dengan masing-masing arus miror 3,4 dan 5. Akhirnya output arus Z menjadi

7 2 x y Z = − β β Δ Δx y (9) 4. HASIL DAN PEMBAHASAN

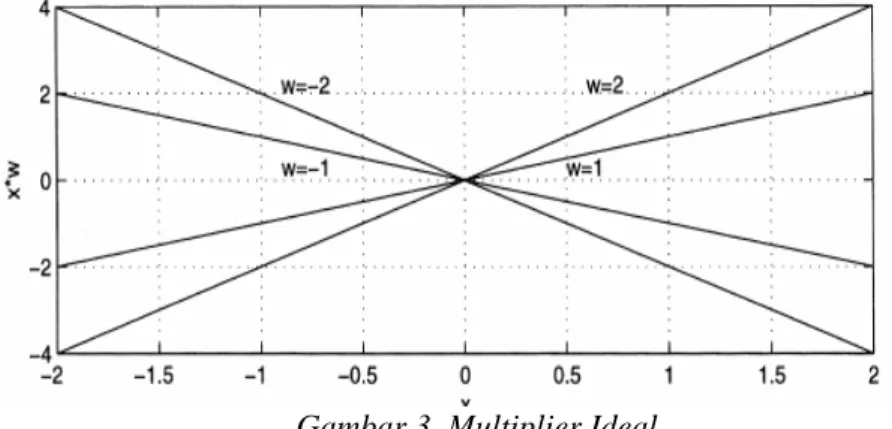

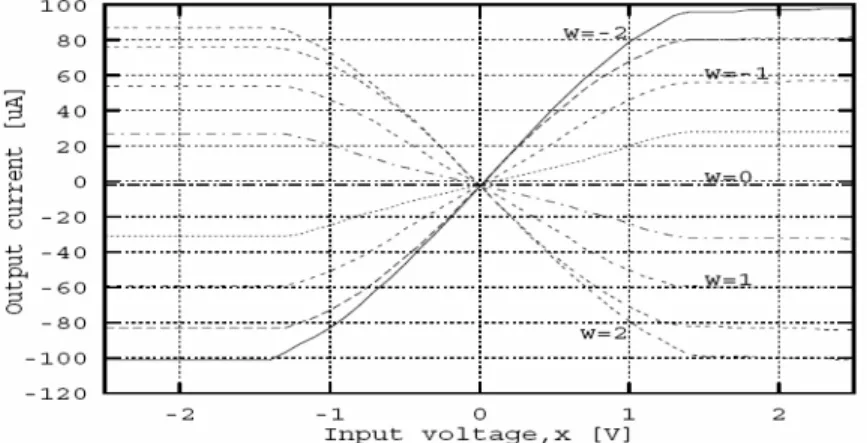

Hasil karakteristik dari arus dari rangkaian synapse untuk perbedaan nilai W = { -2,-1,0,1,2} dapat dilihat pada gambar 4. Hasil simulasi SPICE tersebut

menghasilkan bentuk yang non ideal pada karakteristik synapse dimana bentuk kurva arus sedikit berbeda dari bentuk ideal yang linear dari nilai input dan bobot yang diberikan seperti pada gambar 3

Gambar 4. Hasil Simulasi

5. KESIMPULAN DAN

SARAN

Rancangan rangkaian analog CMOS Multiplier menghasilkan output yang dapat digunakan sebagai rangkaian synapse pada rangkaian analog Jaringan Syaraf Tiruan. Dalam perkembangan berikutnya rangkaian ini nantinya akan dirancang dan disimulasikan menggunakan CMOS teknologi 0,35 μm.

6. DAFTAR PUSTAKA

A. von Lehman, E.G. Paek, P.F. Liao, A. Marrakchi, J.S. Patel, "Factors Influencing Learning by Back-Propagation. IEEE International

Confe-rence on Neural Networks", Vol. I,pp. 335-341, San Diego 1988.

B. Gilbert, “A High-Performance Monolithic Multiplier Using Active Feedback,” IEEE JSSC , Vol. SC-9, No. 6, pp. 364–373, December 1974.

John Hertz, Anders Krogh, Richard G. Palmer, "Introduction to the Theory of Neural Compu-tation",Addison-Wesley, 1991.

Ogrenci, Arif Selcuk, "Multilayer Perceptron Neural Network In Analog VLSI - A System Level Study", Bogazici University, 1999.

Sigvartsen, Roy Ludwig, “An Analog Neural Network With On-Chip Learning”, PhD Thesis, Universitas Osloensis, 1994.