PENYEMPURNAAN DESAIN FILTER HARMONISA

MENGGUNAKAN KAPASITOR EKSISTING PADA

PABRIK SODA KAUSTIK DI SERANG - BANTEN

Margo Pujiantara

Jurusan Teknik Elektro-FTI, Institut Teknologi Sepuluh November Kampus ITS, Keputih Sukolilo, Surabaya-60111

Abstrak : Pada sistem tenaga listrik AC tiga fasa yang ideal, daya listrik disalurkan dengan frekwensi tunggal 50 Hz dan masing-masing line berbeda fasa 120o. Dengan adanya pembebanan yang non linear pada sistem tenaga listrik maka dapat terjadi distorsi harmonisa dan ketidakseimbangan sistem. Hal ini mengakibatkan turunnya kwalitas sistem tenaga listrik. Salah satu metode untuk memperbaikinya adalah dengan menggunakan filter pasif.

Filter pasif yang digunakan dalam paper ini adalah orde dua. Pada paper ini penalaan dilakukan pada frekwensi 550 Hz dan 650 Hz menggunakan kapasitor eksisting (tanpa menambah kapasitor). Filter ini diharapkan dapat menurunkan harmonisa pada frekwensi ke-11 dan ke-13 yang timbul akibat beban konverter 12 pulsa.

Kata Kunci : harmonisa, resonansi, damped filter

1. PENDAHULUAN

Harmonisa adalah cacat gelombang yang disebabkan oleh interaksi antara gelombang sinusoidal sistem dengan komponen gelombang lain yang mempunyai frekwensi kelipatan integer dari komponen fundamentalnya. Penyebab harmonisa ini ialah adanya beban nonlinear seperti konverter, tanur busur listrik, UPS dll.tidak sinusoidal. Kerugian akibat pengaruh harmonisa seperti : pemanasan pada peralatan, penurunan faktor daya, masalah resonansi dll.

Untuk meningkatkan kwalitas sistem tenaga listrik maka distorsi harmonisa harus ditekan seminimalnya. Salah satu caranya adalah dengan menggunakan filter harmonisa. Filter harmonisa selain dapat mereduksi distorsi harmonisa juga dapat berfungsi sebagai kompensator reaktif pada frekwensi fundamental.

Beban utama sistem kelistrikan pada perusahaan penghasil soda kaustik yang diamati ialah konverter 12 pulsa yang dipergunakan untuk suplai proses elektrolisis. Akibat dari beban konverter 12 pulsa tersebut harmonisa orde ke-11

dan ke-13 cukup tinggi sehingga perlu untuk dikurangi. Tujuan dari paper ini ialah mereduksi harmonisa orde ke-11 dan ke-13 tanpa manambah kapasitor.

Dalam paper ini dibahas metode untuk mandesain filter harmonisa dengan damper sehingga dapat menurunkan individual harmonic sampai kurang dari 3 % dan mengoptimalkan kondisi eksisting.

2. HARMONISA DAN FILTER

2.1. Pengertian HarmonisaPada sistem tenaga listrik ac ideal, energi listrik disalurkan dalam frekuensi tunggal yang konstan dan pada level tegangan yang konstan pula. Tetapi dengan perkembangan beban listrik yang semakin besar dan komplek, terutama penggunaan beban-beban tak linier, akan menimbulkan perubahan pada bentuk gelombangnya.

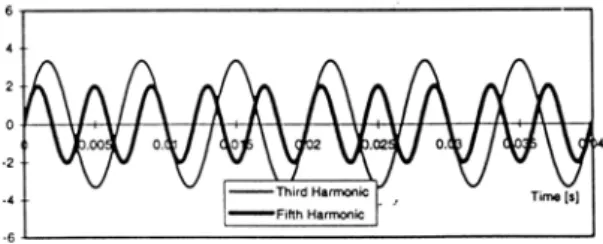

Cacat gelombang yang disebabkan oleh interaksi antara bentuk gelombang sinusoidal sistem dengan komponen gelombang lain lebih dikenal dengan harmonisa, yaitu komponen gelombang lain yang mempunyai frekuensi kelipatan integer dari komponen fundamentalnya seperti ditunjukkan pada gambar 1.

Gambar 1. Bentuk gelombang harmonisa 2.2. Sumber – Sumber Harmonisa

Dalam sistem tenaga listrik AC sumber-sumber harmonisa dapat berasal dari pemakaian beban-beban tak linier seperti :

9 Konverter 9 Tanur busur listrik 9 Lampu Florence

19 C1 L R C2 Impedansi Frekuensi, f R

Selain itu pada beban linier seperti transformator dan motor-motor induksi juga dapat membangkitkan harmonisa pada jaringan. Tetapi harmonisa yang dibangkitkan cukup kecil jika dibandingkan dengan menggunakan beban-beban tak linier.

2.3. Distorsi Harmonisa

Dalam harmonisa khususnya pada sistem tenaga listrik dipakai istilah Total Harmonic Distortion (THD) yang didefinisikan sebagai persentase total komponen harmonisa terhadap komponen fundamentalnya. Total Harmonic Distortion (THD) dituliskan sebagai : % 100 1 2 1 2 x U U THD k n⎥ ⎦ ⎤ ⎢ ⎣ ⎡ =

∑

(1) Dimana : Un = komponen harmonisa U1 = komponen fundamentalk = komponen harmonisa maksimum yang diamati

Perhitungan tersebut tidak sama untuk setiap negara tergantung standar yang dipakai. Dalam paper ini diberikan standar dari IEEE Std. 519-1992 seperti pada tabel 1.

Tabel 1. Limit distorsi tegangan

Bus Voltage at PCC Individual Voltage Distortion (%) THD (%) 69 kV and below 3,0 5,0 69,001 kV through 161 kV 1,5 2,5 161,001 kV and above 1,0 1,5 2.4. Filter Harmonisa

Tujuan utama dari filter harmonisa adalah untuk mengurangi amplitudo satu atau lebih frekuensi tertentu dari sebuah tegangan atau arus. Dengan penambahan filter harmonisa pada suatu sistem tenaga listrik yang mengandung sumber-sumber harmonisa, maka penyebaran arus harmonisa ke seluruh jaringan dapat ditekan sekecil mungkin. Selain itu filter harmonisa pada frekuensi fundamental dapat mengkompensasi daya reaktif dan dipergunakan untuk memperbaiki faktor daya sistem. 2.5. Perencanaan High Pass Filter Damped Orde Dua

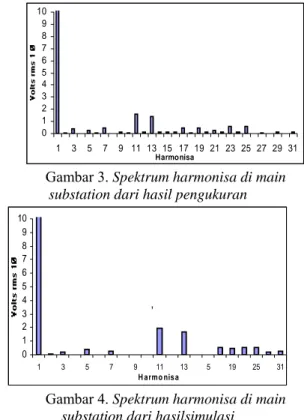

High Pass Filter orde dua diperlihatkan pada gambar 2 yang terdiri atas resistansi yang diparalel dengan induktor/ reaktor dan diseri dengan kapasitor. Impedansi rangkaian : L j R L j R C j Z ω ω ω + + = 1 . L j R L j R x L j R L j R C j ω ω ω ω ω − − + + = 1 . 2 2 2 2 2 2 2 2 2 1 L R RL L R L jR C j ω ω ω ω ω + + + + = ⎟ ⎟ ⎠ ⎞ ⎜ ⎜ ⎝ ⎛ − + + + = C L R L R j L R RL ω ω ω ω ω 1 2 2 2 2 2 2 2 2 2

Pada saat resonansi bagian imajiner = 0 sehingga : 0 1 0 2 2 0 2 0 2 = − + L C R L R ω ω ω 2 2 0 2 2 0 2 LC R L R ω = +ω Sehingga : 0 2 2 0 2 2 2 0 L −R ω CL+R = ω a=ω02 ; b=-R2ω02C ; c=R2 a ac b b L 2 4 2 12=− ± − 2 0 2 2 0 2 2 0 2 2 0 2 12 2 4 ) ( ω ω ω ω C R C R R L = ± − 2 0 2 2 0 2 4 0 4 2 0 2 12 2 4 ω ω ω ω C R C R R L = ± −

Agar terdapat nilai L maka dibawah akar harus ≥ 0, sehingga : 0 4 02 2 2 4 0 4 C − R ≥ R ω ω C R 0 2 ω ≥

Gambar 2. High Pass Filter orde dua [2]. (a) Gambar rangkaian (b) Kurva impedansi fungsi

frekwensi

3. SISTEM KELISTRIKAN

EKSISTING

Sistem kelistrikan eksisting disuplai dari PLN dengan tegangan 150 KV dan kapasitas daya terpasang dari PLN adalah 71,464 MVA. Tegangan 150 kV tersebut diturunkan menjadi 20 kV oleh trafo utama yang berkapasitas 80 MVA.

Beban utama pabrik adalah rectifier yang dipakai untuk elektrolisa. Adapun rectifier tersebut adalah rectifier 6 pulsa dan 12 pulsa, sehingga distorsi harmonisa yang dominan adalah harmonisa ke 5, 7, 11 dan 13.

4. HARMONISA DAN

PENYEMPURNAAN DESAIN FILTER

4.1. Simulasi Pada Kondisi Eksisting Beban 64%Asumsi yang dipakai dalam simulasi ini adalah sumber kelistrikan PLN yang merupakan swing bus yang tidak terpengaruh perubahan diluar sistem kelistrikannya.

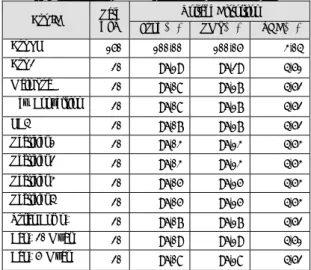

Tabel 2. Hasil Simulasi Aliran Daya pada kondisi eksisting

SUMMARY OF TOTAL GENERATION , LOADING & DEMAND

Study : MW MVar MVA % PF

Swing Bus (es) : 43.802 7.652 44.465 98.5 Lagging Generator : 0.000 0.000 0.000 100.0 Lagging Total Demand : 43.802 7.652 44.465 Lagging 98.5 Total Motor Load 43.023 29.607 52.226 82.4 Lagging Total Static Load : 0.481 -26.013 Apparent Loss : 0.297 4.057

Catatan : Tabel diatas adalah output Load Flow Report dari Software ETAP

Dari simulasi harmonisa dengan Software ETAP maka diperoleh tingkat distorsi harmonisa pada kondisi eksisting yang terlihat pada tabel 3.

Tabel 3.Tingkat distorsi harmonisa eksisting pada bus utama Bus ID Rated kV Voltage Distortion Fund (%) RMS(%) THD(%) 100 100.02 2.00 Bus 2 20 99,07 99,11 2,87 Main Sub 20 99,01 99,05 2,88 New Conversion 20 99,01 99,05 2,88 LC4 20 99,01 99,05 2,88 Rsectifier 1 20 98,97 99,02 2,88 Rectifier 2 20 98,98 99,02 2,88 Rectifier 3 20 98,99 99,03 2,88 Rectifier 4 20 99,00 99,04 2,88 Turbo Comp. 20 99,01 99,05 2,88 Cap. 20 Mvar 20 99,03 99,07 2,87 Cap. 5 Mvar 20 99,01 99,05 2,88

Pada kondisi eksisting, distorsi tegangan bus-bus utama sistem masih dibawah standar IEEE

519-1992 (Vthd < 5%) kecuali pada bus sumber harmonisa.

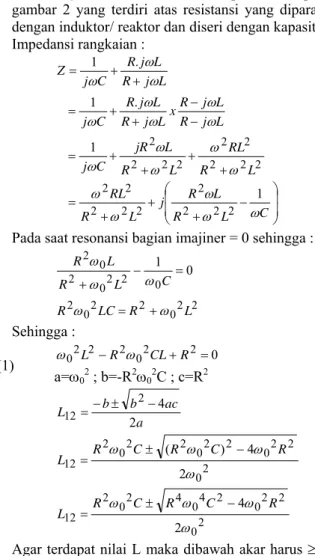

Dalam plot dibawah ini ditampilkan plot spektrum pada saatpengukuran dan simulasi pada bus mainsubstation. 0 1 2 3 4 5 6 7 8 9 10 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 Harmonisa

Gambar 3. Spektrum harmonisa di main substation dari hasil pengukuran

0 1 2 3 4 5 6 7 8 9 10 1 3 5 7 9 11 13 5 19 25 31 H armo nis a ,

Gambar 4. Spektrum harmonisa di main substation dari hasilsimulasi

Dari gambar di atas terlihat bahwa hasil simulasi sama dengan hasil pengukuran saat eksisting (beban 64%).

4.2. Simulasi Kondisi Eksisting Beban 100 % Berdasarkan sistim saat pengukuran yang bebannya hanya 64 %, maka sistem dapat dikembangkan ke pembebanan 100 %. Pada kondisi tersebut daya yang diambil dari PLN sebesar 68,78 MW. Hasil simulasinya dapat dilihat pada tabel berikut.

Tabel 4. Hasil simulasi aliran daya eksisting beban penuh

SUMMARY OF TOTAL GENERATION , LOADING & DEMAND

Study : MW Mvar MVA % PF

Swing Bus (es) : 67,61 8 33,023 75,251 89,9 Lagging Generator : 0,000 0,000 0,000 100,0 Lagging Total Demand : 67,61 8 33,023 75,251 89,9 Lagging Total Motor Load 66,28 0 46,056 80,710 82,1 Lagging Total Static Load 0,453 -24,483 Apparent Loss : 0,885 11,450

Catatan : Tabel diatas adalah output Load Flow Report dari Software ETAP

21

Tingkat distorsi harmonisa diperoleh dengan melakukan simulasi Software ETAP (Harmonic Analysis) dan hasilnya dapat dilihat pada tabel 5 sebagai berikut :

Tabel 5. Tingkat distorsi harmonisa dengan pembebanan 100% pada bus-bus utama

Bus ID d kV Rate Voltage Distortion Fund (%) RMS(%) THD(%) Bus PLN 150 100,00 100,05 3,04 Bus 2 20 96,19 96,29 4,51 Main Sub 20 96,08 96,17 4,52 New Conversion 20 96,08 96,17 4,52 LC4 20 96,07 96,17 4,52 Rectifier 1 20 96,03 96,13 4,53 Rectifier 2 20 96,03 96,13 4,53 Rectifier 3 20 96,05 96,15 4,53 Rectifier 4 20 96,05 96,15 4,53 Turbo Comp. 20 96,07 96,17 4,52 Cap. 20 Mvar 20 96,09 96,19 4,51 Cap. 5 Mvar 20 96,08 96,18 4,52

Dari tabel 5 di atas terlihat bahwa total harmmonic distortion masih di bawah ambang batas [1].

Gambar 5. Plot impedansi bus 20 KV pada pembebanan 100 % 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 17 19 23 25 29 31

Harm onic orde

Vo lt a g e sp ec tr u m ( % )

Gambar 6. Spektrum tegangan bus PLN eksisting pada pembebanan 100 % Dari gambar di atas menunjukkan bahwa harmonisa ke 11 dan 13 melampaui ambang batas (3%) [1,3], sehingga perlu dirancang filter untuk mereduksi harmonisa tersebut.

4.3. Perencanaan Filter Harmonisa

Untuk mendapatkan kualitas tegangan yang lebih baik maka filter penalaan tunggal pada bus mainsub akan dimodifikasi menjadi filter harmonisa karena terjadi resonansi pada bus-bus tersebut dan distorsi tegangan yang melebihi standar. Jenis filter yang digunakan adalah high pass filter. Sebuah high pass filter adalah rangkaian resistor dan induktansi yang diparalel dan diseri dengan kapasitor. Pada frekuensi penalaan yang telah ditetapkan, rangkaian ini menghasilkan impedansi minimal sehingga menjadi jalan bagi arus-arus harmonisa pada frekuensi penalaan dan arus-arus harmonisa pada frekuensi diatas frekuensi penalaan yang ada di jaringan. Sehingga akan memperbaiki plot impedansi jaringan dan menurunkan tingkat distorsi harmonisa dibawah standar IEEE 519-1992 (VTHD < 5%). Perbandingan nilai filter

MVar MVar MVar x . , F = 5 =2808,708839 ≈2809 2 46 9 25 11 MVar MVar MVar x , , F = 5 =2191,291161 ≈2191 2 46 2 20 13 Perhitungan Filter

a) Filter F11 / 550 Hz / 2809 kVar di Main Sub 2 Perencanaan filter F11 menggunakan jenis high pass filter orde dua. Nilai komponen kapassitor, resistor dan induktor dapat dihitung sebagai berikut :

Kapasitor

Nilai kapasitor dihitung berdasarkan daya reaktif yang dibutuhkan. Dari perhitungan sebelumnya dibutuhkan daya reaktif sebesar 2809 kVar pada tegangan 20 kV.

-9 210 V C f 2 kVar= π dengan :

C = kapasitansi dalam micro farad (uF) f = frekuensi sistem (Hz)

V = tegangan jala-jala (Volt)

Nilai komponen kapasitor, resistor dan induktor dapat dihitung sebagai berikut :

F ) .( . C = μ π = 2 −9 22.36233152 10 20000 50 2 2809 Induktor

Frekuensi resonansi f0 = 550 Hz sehingga nilai induktor dapat dihitung sebagai berikut :

( ) 3.75 mH 2.10 22.3623315 -6= = ω = 2 2 0 2 314 550 1 1 x . x C L Resistor

Sedangkan untuk mencari resistor dapat digunakan persamaan :

(

)

= Ω = ω = 25.89348946 2 22.3623315 2x3.14x550 2 2 0 2 C RSpesifikasi yang lebih lengkap adalah sebagai berikut :

Spesifikasi Kapasitor

¾ Kapasitas kapasitor = 22,36 μF

¾ Arus kapasitor pada tegangan sistem dan frekuensi fundamental : φ sin I V 3 Q= LL C dimana sinφ=1 A A 20000 3 2.809.000=8109 ≈81 = , IC

¾ Tegangan kapasitor pada tegangan base system :

(

)

-1 C C X 81 22,36 I = 2π50 10−6 = . . . . VC φ =11530,9 V1 C V =19972.11 V3φSpesifikasi Induktor / Reactor ¾ Induktansi nominal = 3,75 mH ¾ Arus nominal filter = 57,77 A

Arus nominal diperoleh dari simulasi Circuit Maker.

Spesifikasi Resistor

¾ Resistansi nominal = 25,89 Ohm ¾ Rating daya resistor = 321,1 W

Rating daya diperoleh dari simulasi Circuit Maker

b) Filter F13 / 650 Hz / 2191 kVar di Main Sub 2. Perencanaan filter F13 menggunakan jenis high pass filter orde dua. Nilai komponen kapasitor, resistor dan induktor dapat dihitung sebagai berikut :

Kapasitor

Nilai kapasitor dihitung berdasarkan daya reaktif yang dibutuhkan. Dari perhitungan sebelumnya dibutuhkan daya reaktif sebesar 2037 Kvar pada tegangan 20 kV.

-9 210 V C f 2 kVar= π

Nilai komponen kapasitor, resistor dan induktor dapat dihitung sebagai berikut :

F x ) ( x x x C = μ π = 2 −9 17.44658568 10 20000 50 2 2191 Induktor

Frekuensi resonansi f0 = 650 Hz sehingga nilai induktor dapat dihitung sebagai berikut :

( )17.44658568.10-6=3,44 mH = ω = 2 2 0 2 314 650 1 1 x . x C L Resistor

Sedangkan untuk mencari resistor dapat digunakan persamaan : ( ) = Ω = ω = 28.08319708 8.10 17.4465856 2x3.14x650 2 6 -2 0 2 C R

Spesifikasi yang lebih lengkap adalah sebagai berikut :

Spesifikasi Kapasitor

¾ Kapasitas kapasitor = 17,45 uF

¾ Arus kapasitor pada tegangan sistem dan frekuensi fundamental : φ sin I V 3 Q= LL C dimana sinφ=1 A A 9 63,2487219 20000 3 2.191.000 63 ≈ = = C I

¾ Tegangan kapasitor pada tegangan base system :

(

)

-1 C CX 63 17.44658568 I = 2π50 10−6 = . . . . VC φ =11497.82 V1 C V =19914.81V3φSpesifikasi Induktor / Reactor ¾ Induktansi nominal = 3,44 mH ¾ Arus nominal filter = 44,8 A

Arus nominal diperoleh dari simulasi Circuit Maker.

Spesifikasi Resistor

¾ Resistansi nominal = 28,08 Ohm ¾ Rating daya resistor = 160,2 W

Rating daya diperoleh dari simulasi Circuit Maker

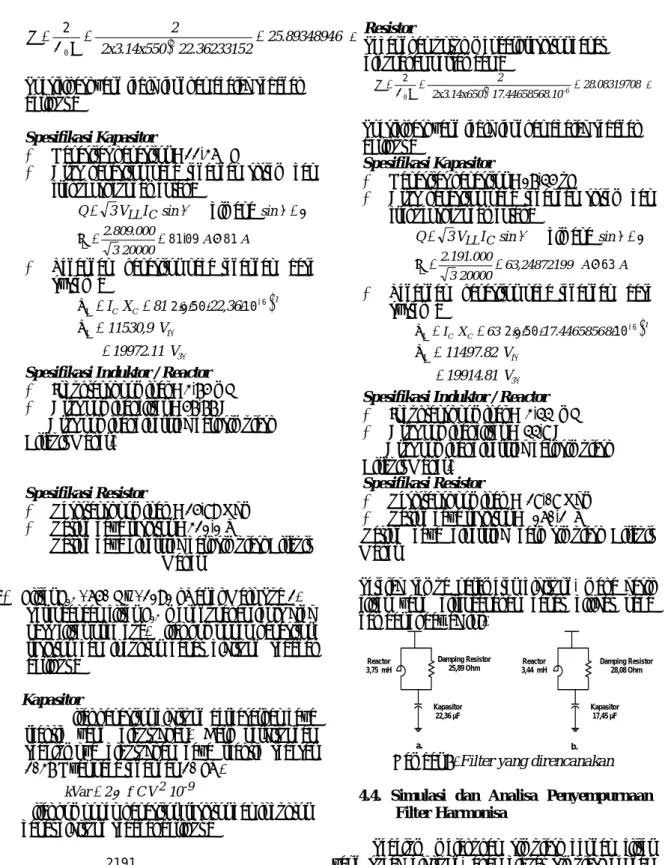

Setelah semua parameter dihitung, maka hasil filter yang direncanakan dapat dilihat pada gambar di bawah ini.

Reactor 3,75 mH Damping Resistor 25,89 Ohm Kapasitor 22,36 µF Reactor 3,44 mH Damping Resistor 28,08 Ohm Kapasitor 17,45 µF b. a.

Gambar 7. Filter yang direncanakan 4.4. Simulasi dan Analisa Penyempurnaan

Filter Harmonisa

Sebelum melakukan simulasi dengan filter yang sudah dihitung, akan dibuat simulasi dengan kapasitor yang sudah dipecah terlebih dahulu. Dalam simulasi ini sistem dipasang dengan kapasitor yang dihitung sebelumnya berdasarkan perbandingan persen arus pada rectifiernya sehingga diperoleh C1= 2809kVar dan C2= 2191 kVar. Hasil simulasinya dapat dilihat pada tabel 6 dan 7.

23

Tabel 6. Hasil Simulasi Aliran Daya setelah penyempurnaan filter harmonisa

SUMMARY OF TOTAL GENERATION , LOADING & DEMAND

Study : MW Mvar MVA % PF

Swing Bus (es) : 67,516 33,295 75,279 89,7 Lagging Generator : 0,000 0,000 0,000 100,0 Lagging Total Demand : 67,516 33,295 75,279 89,7 Lagging Total Motor Load 66,274 46,047 80,700 82,1 Lagging Total Static Load 0,393 -24,220 Apparent Loss : 0,849 11,468

Catatan : Tabel diatas adalah output Load Flow Report dari Software ETAP

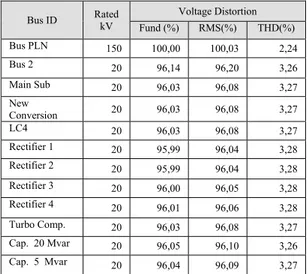

Tabel 7. Tingkat distorsi harmonisa pada bus-bus utama setelah penyempurnaan filter harmonisa

Bus ID Rated kV Voltage Distortion Fund (%) RMS(%) THD(%) Bus PLN 150 100,00 100,03 2,24 Bus 2 20 96,14 96,20 3,26 Main Sub 20 96,03 96,08 3,27 New Conversion 20 96,03 96,08 3,27 LC4 20 96,03 96,08 3,27 Rectifier 1 20 95,99 96,04 3,28 Rectifier 2 20 95,99 96,04 3,28 Rectifier 3 20 96,00 96,05 3,28 Rectifier 4 20 96,01 96,06 3,28 Turbo Comp. 20 96,03 96,08 3,27 Cap. 20 Mvar 20 96,05 96,10 3,26 Cap. 5 Mvar 20 96,04 96,09 3,27

Dari tabel di atas terlihat bahwa hasilnya menunjukkan perbaikan pada THD-nya.

Plot Impedansi dan Spektrum Tegangan Bu-Bus utama

Gambar 8. Plot impedansi bus 20 KV pada pembebanan 100 % setelah pemasangan filter

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 17 19 23 25 29 31

H a rmo nic o rde

Gambar 9. Spektrum tegangan 20 KV pada pembebanan 100 % setelah pemasangan filter

Gambar di atas menunjukkan bahwa terjadi perbaikan pada hamonisa tunggal utamanya harmonisa ke 11 dan 13 hingga di bawah ambang standar (3 %).

5. KESIMPULAN

Dari hasil perhitungan dan analisa yang telah dilakukan, dapat diambil kesimpulan sebagai berikut :

1. Penggunaan filter LC penalaan tunggal 5 MVar yang ditala pada frekuensi 204 Hz (berdasarkan data sekunder) dapat dioptimalkan menjadi damping filter yang ditala pada frekuensi ke-11 dan 13 sehingga dapat menurunkan harmonisa individu yang ada pada bus utama seperti pada tabel berikut. Frekwensi ke-11 Frekwensi ke-13 Dari Ke Dari Ke Bus 2 3,09 1,92 2,65 1,12 Bus PLN 2,1 1,35 1,77 0,78

¾ Data diatas diambil dari report harmonic loadflow Etap

2. Filter yang digunakan adalah High Pass Filter orde dua yang ditala pada frekuensi 550 Hz dan frekuensi 650 Hz di bus mainsubstation, karena terjadi resonansi pada frekuensi-frekuensi tersebut. High Pass Filter orde dua sebagai jalur yang dapat menyerap harmonisa pada frekuensi penalaan dan frekuensi diatas frekuensi penalaannya. Setelah pemasangan filter tersebut maka diperoleh perbaikan plot impedansi dan distorsi tegangan harmonisa yang rendah (VTHD < 5%).

6. DAFTAR PUSTAKA

1. Arrilaga J, “Power System Harmonic”, John Wiley & Sons, New York, 1985.

2. Dugan R.C, “Electrical Power Systems Quality”, McGraw-Hill, New York, 1996. 3. Keskar P.Y, “Spesification Of Variable

Frequency Drive Systems To Meet The New IEEE 519 Standard”, IEEE Transaction On Industry Aplications, Vol.32 No.2 March/April 1996.

4. Ned Mohan, “Power Electronics”, John Wiley & Sons, New York, 1987.

5. Rashid M.H, “Elektronika Daya”, Jilid 1, PT. Prenhallindo, Jakarta, 1993.

6. Stevenson W.D, “Analisis Sistem Tenaga Listrik”, edisi keempat, McGraw-Hill, London, 1993.

9. W. Mielczarski, “Quality of Electricity Supply & Management of Network Losses”, Puma Press, Melbourne, 1997.

7. BIODATA PENULIS

Margo Pujiantara, lahir 18 Maret 1966 di Pasuruan. Saat ini menjadi dosen di Jurusan Teknik Elektro – ITS dalam bidang Industrial Electrical sejak tahun 1989. Email: [email protected]