KAJIAN DISTORSI INTERMODULASI PADA PENGUAT DAYA RF LDMOS

Aip SaripudinDosen Jurusan Pendidikan Teknik Elektro

Fakultas Pendidikan Teknologi dan Kejuruan Universitas Pendidikan Indonesia Jl. Setiabudhi 229 Bandung, Telp. (022) 70821958, e-mail: [email protected]

ABSTRAK

Kajian distorsi intermodulasi LDMOS telah selesai dilakukan. Hal-hal yang dikaji meliputi pengaruh pemberian tegangan bias, beban, dan daya masukan pada distorsi intermodulasi orde ketiga. Pekerjaan dimulai dengan melakukan pengukuran karakteristik I-V LDMOS. Selanjutnya, parameter-parameter devais diekstrak berbasis model nonlinier TOM (Triquint Owned Model) menggunakan bantuan perangkat lunak FET-FIT 2.0. Simulasi untuk melihat perilaku distorsi intermodulasinya dilakukan dengan bantuan perangkat lunak SUPER DERRIV 4.0. Hasil simulasi menunjukkan bahwa nilai minimum distorsi intermodulasi dipengaruhi oleh tegangan bias VGS dan VDS, resistansi beban RL, dan daya masukan. Hasil simulasi juga

menunjukkan bahwa secara umum ACPR meningkat terhadap kenaikan daya masukan.

Kata Kunci: LDMOS, RF, distorsi intermodulasi, ACPR.

1. PENDAHULUAN

Linieritas penguat daya frekuensi radio (RF) memegang peranan penting dalam sistem komunikasi nirkabel. Akan tetapi, penguat daya itu sendiri memiliki sifat linier dan nonlinier sekaligus. Sifat nonlinier penguat daya RF mengakibatkan sinyal-sinyal keluarannya mengalami distorsi intermodulasi dan menghasilkan respon spurious. Pada sistem komunikasi multikanal padat, CDMA misalnya, distorsi intermodulasi atau spurious dapat berinterferensi dengan sinyal transmisi lain pada kanal lain yang berdekatan. Akibatnya, kanal-kanal komunikasi dapat menyalurkan bagian sinyal dari kanal lain sehingga terjadi keadaan tumpang tindih dan tidak teratur.

Oleh karena itu, pada penguat daya, sifat nonlinier merupakan sifat yang tidak dikehendaki kemunculannya. Dengan kata lain, diperlukan suatu kajian atau teknik tertentu agar sifat nonlinier ini bisa diredam. Hal ini menjadi penting, karena memang tidak pernah ada devais yang hanya memiliki sifat linier.

Salah satu metoda untuk menyelidiki perilaku nonlinier pada penguat daya adalah analisis distorsi intermodulasi. Ini merupakan parameter penting yang menunjukkan kinerja perilaku nonlinier transistor. Analisis distorsi intermodulasi relatif telah dipelajari dengan baik, baik secara teoretis maupun eksperimental, melalui eksitasi dua-nada (two-tone). Metoda ini digunakan untuk mendapatkan titik perpotongan orde-3 (IP3) yang menjadi nilai mutu (figure of

merit) linieritas penguat daya. Analisis ini dilakukan baik pada transistor bipolar maupun

transistor efek medan (FET), dan hasil yang baik diperoleh untuk masukan-masukan dengan amplitudo sama.

Tulisan pada paper ini difokuskan pada kajian distorsi intermodulasi pada penguat daya RF

LDMOS. Kajian ini meliputi pengaruh pemberian bias gate-source dan drain-source, resistansi

2. LANDASAN TEORI

2.1 Struktur Dasar dan Prinsip Kerja LDMOSFET

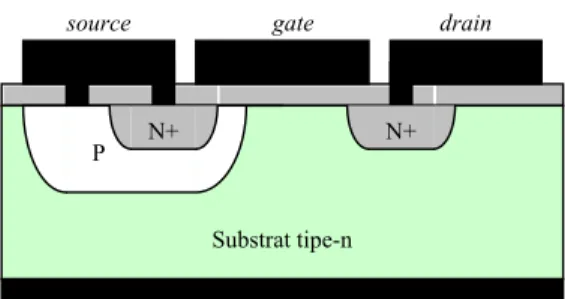

Struktur dasar LDMOS ditunjukkan pada Gambar 1. LDMOSFET (Lateral Diffusion Metal Oxide

Semiconductor Field Effect Transistor), atau sering disebut LDMOS saja, merupakan devais

dengan tiga terminal yaitu gate, drain, dan source. Substratnya terbuat dari silikon tipe-n. Drain dan source merupakan daerah dengan doping N+. Akan tetapi, berbeda dengan MOSFET biasa, pada LDMOS daerah source (N+) berada pada daerah P yang didoping secara lateral. Doping P ini dimaksudkan untuk meningkatkan gain RF dan mencegah punch-through pada tegangan drain-source, VDS, tinggi.

Gambar 1 Struktur dasar LDMOSFET

Prinsip kerja transistor dapat dipahami dari Gambar 1. Seperti FET pada umumnya, kerja

LDMOS didasarkan pada pengaturan arus drain ke source oleh tegangan gate. Pada tegangan gate-source, VGS, nol, source dan drain merupakan sambungan p-n yang terhubung saling

membelakangi. Hanya arus bocor yang dapat mengalir dari drain ke source. Jika VGS positif

diberikan, lapisan inversi permukaan atau kanal dibentuk pada daerah p sehingga source dan

drain terhubung oleh kanal n konduksi. Ketika tegangan drain-source, VDS, diberikan, arus akan

mengalir dari drain ke source. Konduktansi kanal ini dapat dimodulasikan dengan mengubah-ubah VGS.

Jika VDS kecil diberikan, arus akan mengalir dari drain ke source melalui kanal konduksi.

Kanal bertindak sebagai resistor dan arus drain sebanding dengan VDS. Ini merupakan daerah

linier. Jika tegangan drain meningkat, akan dicapai suatu titik dimana lebar kanal menjadi nol, disebut titik pinch-off. Pada titik pinch-off, arus drain-source relatif konstan. Arus drain sebagai fungsi VGS dan VDS ditunjukkkan pada Gambar 2.

Gambar 2 Kurva karakteristik I-V FET secara umum.

source gate drain

Substrat tipe-n

P N+ N+

VDS

2.2 Mekanisme Distorsi intermodulasi

Sebelum mendiskusikan hasil mengenai pengaruh bias dan beban pada distorsi, terlebih dahulu kita tinjau formulasi matematis mekanisme distorsi. Untuk itu, anggap skema penguat daya source bersama seperti yang ditunjukkan pada Gambar 3.

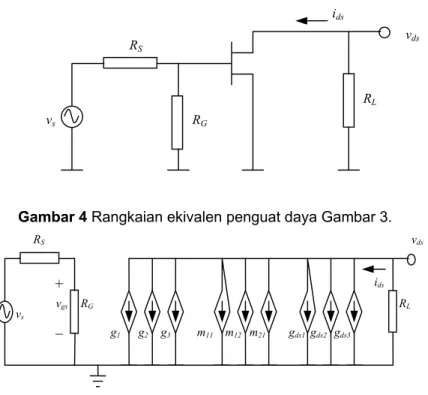

Gambar 3 Skema penguat daya konfigurasi source bersama.

Gambar 4 Rangkaian ekivalen penguat daya Gambar 3.

Analisis deret Volterra dapat digunakan untuk mengetahui parameter-parameter yang memengaruhi karakteristik distorsi secara umum. Untuk menyederhanakan analisis, kita menganggap bahwa impedansi masukan FET sangat besar (takhingga). Keadaan ini dapat didekati jika frekuensi masukan relatif kecil, dalam orde puluhan sehingga kapasitansi

gate-source, Cgs, terlihat sebagai masukan impedansi sangat tinggi (terbuka). Rangkaian ekivalen

penguat daya untuk analisis deret Volterra ditunjukkan pada Gambar 4. Arus drain-source di sekitar titik kerja dapat dinyatakan oleh persamaan:

2 12 2 21 11 3 3 2 2 1 3 3 2 2 1 ds gs ds gs ds gs ds ds ds ds ds ds gs m gs m gs m ds v v m v v m v v m v g v g v g v g v g v g i + + + + + + + + = (1) dengan gm1, gm2, dan gm3 menyatakan transkonduktansi orde ke-1, 2, dan 3; gds1, gds2, dan gds3

menyatakan transkonduktansi keluaran orde ke-1, 2, dan 3; m11, m21, dan m21 menyatakan

koefisien “silang” berkaitan dengan vgs dan vds sekaligus. Semua koefisien di atas

merepresentasikan turunan dari Persamaan (1), dan dalam hal ini disebut koefisien intrinsik. Sekarang tinjau dua sumber masukan dengan amplitudo sama dan frekuensi masing-masing ω1 dan ω2 sebagai berikut:

[

t t]

A

vs = cosω1 +cosω2 (2)

Untuk RG = RS, sesuai konsep pembagi tegangan, maka

vds ids RL RG RS vs vds + _ ids RL RG RS vs vgs g1 g2 g3 m11 m12 m21 gds1 gds2 gds3

[

t t]

A v v s gs cos 1 cos 2 2 2 = ω + ω = (3)Persamaan (3) disubstitusikan ke Persamaan (1) dengan menggunakan analisis deret Volterra. Hasilnya sebagai berikut [4]:

) ( ) (ω m1 Lef gs ω ds g R v v =− (4)

[

( ) ( ) ( ) ( )]

) 2 ( 2 2 11 2 2 ω ω ω ω ω Lef m gs ds gs ds ds ds R g v m v v g v v = + + (5)(

)

+ + + + + = ) ( ) 2 ( ) ( ) 2 ( 2 1 ) ( ) ( ) ( ) ( ) ( ) ( 4 1 ) 3 ( 2 11 3 3 2 21 2 12 3 3 ω ω ω ω ω ω ω ω ω ω ω ds ds ds gs ds ds ds gs ds gs ds gs m Lef ds v v g v v m v g v v m v v m v g R v (6) dengan 1 1 + = L ds L Lef R g R R (7)Persamaan (5) dan (6) diperoleh dengan memecahkan setiap komponen nonlinier secara iteratif pada frekuensi harmonik yang berkaitan. Prosedur yang sama dapat diterapkan untuk menghitung amplitudo tegangan pada frekuensi distorsi intermodulasi ω1-ω2 dan 2ω1-ω2.

Untuk mendapatkan pemahaman intuitif dari hubungan-hubungan dan pentingnya persamaan di atas, diperlukan penyederhanaan asumsi. Dalam hal ini diasumsikan bahwa term kedua pada Persamaan (5) dan Persamaan (6) tidak terlalu memengaruhi karakteristik distorsi orde ketiga. Pendekatan ini cukup beralasan karena pengaruhnya sangat kecil.

Sesuai dengan asumsi di atas, kita dapat mendeduksi Persamaan (5) dan Persamaan (6) sebagai berikut:

[

2]

2 11 2 1 2 2 1 1 ) ( ) ( ) 2 ( v ds v m gs Lef ds ds A g A m g v R v v + + ≈ − ≈ ω ω ω ω (8)[

3]

3 2 21 12 3 1 3 2 1 1 ) ( ) 2 ( ) 3 ( v ds v v m gs Lef ds ds A g A m A m g v R v v + + + ≈ − ≈ ω ω ω ω (9) dengan Lef m v g R A = 1 (10)Parameter intrinsik Persamaan (1) diperoleh dari model TOM untuk LDMOS D2081UK. Analisis deret Volterra dari Persamaan (5) hingga Persamaan (6) telah digunakan untuk mengamati bagaimana perubahan distorsi intermodulasi terhadap bias dan resistansi beban. Resistansi beban digunakan untuk memberikan variasi gain tegangan yang signifikan.

3. HASIL DAN PEMBAHASAN

Pekerjaan penelitian dimulai dengan melakukan pengukuran karakteristik I-V RF LDMOS

D2081UK. Selanjutnya, penyesuaian (fitting) hasil pengukuran dengan model TOM dilakukan

menggunakan perangkat lunak FET-FIT 2.0 untuk mendapatkan parameter-parameter model nonlinier. Parameter-parameter model ini digunakan untuk menganalisis distorsi intermodulasi penguat daya dengan bantuan perangkat lunak SUPER DERRIV 4.0. Hasilnya sebagai berikut.

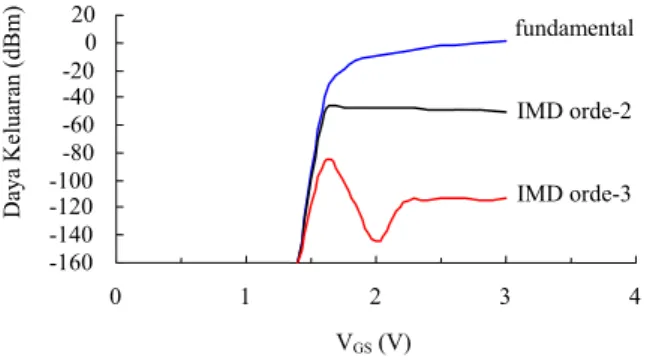

3.1 Pengaruh Bias VGS pada Distorsi intermodulasi

Distorsi intermodulasi penguat dapat diselidiki dengan mengamati plot distorsi sinyal kecil terhadap bias DC pada tegangan drain-source dan resistansi beban tetap. Pada paper ini, pengamatan dilakukan untuk LDMOSFET D2081UK dengan kondisi tegangan drain-source 8V, resistansi beban 50 Ω, dan daya masukan –30 dBm. Hasilnya ditunjukkan pada Gambar 5.

Dari Gambar 5 terlihat bahwa distorsi intermodulasi orde kedua maupun orde ketiga mencapai maksimum pada daerah dekat tegangan ambang. Nilai minimum distorsi orde ketiga terjadi pada VGS = 2V dengan level daya sekitar –140 dBm. Distorsi intermodulasi orde ketiga

naik lagi sampai pada VGS = 2,2 V dan kemudian hampir konstan terhadap kenaikan VGS.

Gambar 5 Daya keluaran terhadap tegangan bias VGS untuk

VDS = 8 V, RL = 50 Ω, dan Pin = -30 dBm.

3.2 Pengaruh Bias VDS pada Distorsi intermodulasi

Selain tegangan gate-source, tegangan drain-source pun memengaruhi distorsi intermodulasi FET. Ini terlihat dari grafik yang ditunjukkan pada Gambar 6.

Dari Gambar 6 terlihat bahwa minimum distorsi intermodulasi orde kedua terjadi pada tegangan drain-source ~1,4 V. Sementara, minimum distorsi intermodulasi orde ketiga terjadi pada ~0,4 V dan memiliki nilai maksimum pada tegangan ~1,4 V dengan level daya ~ -90 dBm. Pada tegangan VDS antara 1,4 V hingga 4,2 V kurva distorsi intermodulasi orde ketiga menurun

cukup besar. Selanjutnya, pada tegangan lebih besar dari 4,2 V, penurunannya relatif sangat kecil (hampir konstan).

Gambar 6 Daya keluaran terhadap tegangan bias VDS untuk

VGS = 2,2 V, RL = 50 Ω, dan Pin = -30 dBm.

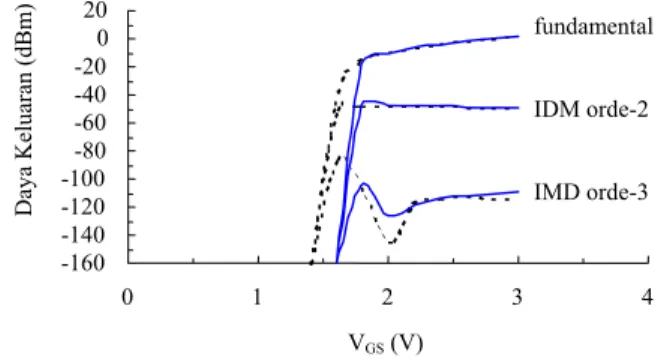

Agar lebih jelas, pada Gambar 7 ditampilkan grafik distorsi intermodulasi terhadap perubahan tegangan bias VGS untuk VDS = 5 V dan 8 V. Dari gambar terlihat bahwa peningkatan

VDS dari 5V hingga 8V menyebabkan penurunan nilai minimum distorsi intermodulasi orde

ketiga sekitar 20 dB. -160 -140 -120 -100 -80 -60 -40 -20 0 0 1 2 3 4 5 6 7 8 9 VDS (V) Daya Keluar an (dBm) fundamental IMD orde-2 IMD orde-3 -160 -140 -120 -100 -80 -60 -40 -20 0 20 0 1 2 3 4 VGS (V) Daya Keluar an (dBm) fundamental IMD orde-2 IMD orde-3

Gambar 7 Daya keluaran terhadap tegangan bias VGS untuk

VDS = 5 V (tegas) dan VDS = 8V (putus-putus), RL = 50 Ω, dan

Pin = -30 dBm.

3.3 Pengaruh Resistansi Beban RL pada Distorsi intermodulasi

Pengaruh resistansi beban pada distorsi intermodulasi ditunjukkan pada Gambar 8. Dari grafik tersebut terlihat bahwa untuk resistansi beban kurang dari 50 Ω, perubahan daya keluaran terjadi cukup signifikan. Minimum distorsi intermodulasi orde ketiga terjadi pada resistansi beban ~ 31 Ω. Di atas 50 Ω, distorsi internodulasi orde ketiga meningkat perlahan seiring peningkatan nilai resistansi beban.

Gambar 8 Daya keluaran terhadap resistansi beban untuk VGS

= 2,2 V dan VDS = 8V.

Gambar 9 menunjukkan distorsi intermodulasi terhadap tegangan bias VGS untuk VDS = 8V,

RL = 25 Ω dan 50 Ω. Terlihat bahwa minimum distorsi intermodulasi orde ketiga mengalami

pergeseran akibat perubahan resistansi beban ini.

Gambar 9 Daya keluaran terhadap VGS untuk resistansi beban

25 Ω (tegas) dan 50 Ω (putus-putus), VDS = 8 V.

fundamental IMD orde-2 IMD orde-3 -160 -140 -120 -100-80 -60 -40 -20 0 20 0 1 2 3 4 VGS (V) Daya Keluar an (dBm) fundamental IMD orde-2 IMD orde-3 -80 -60 -40 -20 0 20 40 0 50 100 150 200 250 300 RL (Ohm) Daya Keluar an (dBm) fundamental IDM orde-2 IMD orde-3 -160 -140 -120 -100 -80 -60 -40 -20 0 20 0 1 2 3 4 VGS (V) Daya Keluar an (dBm)

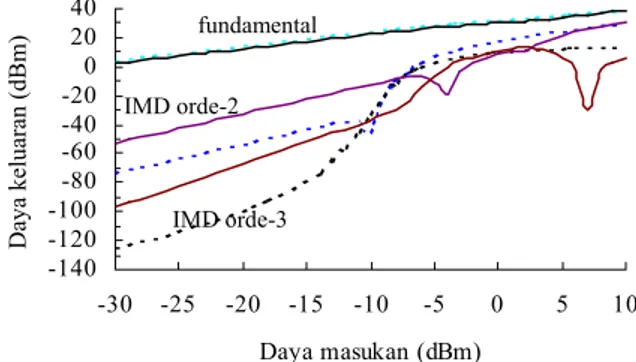

3.4 Pengaruh daya masukan pada distorsi intermodulasi

Distorsi intermodulasi penguat daya juga dipengaruhi oleh level daya masukan. Gambar 10 memperlihatkan pengaruh daya masukan terhadap distorsi intermodulasi. Dari sini terlihat bahwa level distorsi intermodulasi bergantung pada titik kerja penguat. Pada penguat kelas B, pada kasus ini VGS = 1,8 V, level distorsi intermodulasi lebih tinggi daripada kelas AB (VGS = 2,2

V), pada masukan sinyal kecil. Jika masukan berupa sinyal besar, sekitar 0 dBm, level distorsi penguat kelas AB menjadi lebih tinggi. Selain itu, terlihat bahwa pada level sinyal kecil, kenaikan distorsi intermodulasi linier terhadap daya masukan. Sementara, pada level sinyal besar, produk distorsi meningkat.

Gambar 10 Daya keluaran terhadap daya masukan untuk VGS

= 1,8 V (tegas) dan VGS = 2,2 V (putus-putus).

Selanjutnya, jika kita perpanjang kurva bagian linier pada Gambar 10 untuk fundamental dan distorsi intermodulasi orde ketiga, keduanya akan berpotongan di titik pada daya masukan ~15 dBm dan daya keluaran ~46 dBm (IP3 = 46 dBm) untuk VGS = 1,8 V. Sedangkan untuk VGS =

2,2 V, perpotongan terjadi pada daya masukan ~18 dBm dengan daya keluaran ~50 dBm (IP3 = 50 dBm).

Pengaruh daya masukan terhadap distorsi intermodulasi juga dapat terlihat jelas dari Gambar 11. Pada daerah kurang dari P1dB, kenaikan level distorsi intermodulasi orde ketiga

lebih besar dibandingkan dengan kenaikan level fundamental terhadap kenaikan daya masukan. Dengan kata lain, pada daerah ini ACPR (Adjacent Channel Power Ratio) meningkat seiring peningkatan daya masukan. Sementara itu, pada daerah daya saturasi, distorsi intermodulasi orde ketiga juga menunjukkan saturasi, meskipun ada satu nilai pada daya masukan tertentu yang menunjukkan notch atau adanya ACPR yang kembali rendah.

Gambar 11 Daya keluaran terhadap VGS untuk Pin = –10 dBm

(tegas) dan 0 dBm (putus-putus).

fundamental IMD orde-3 IMD orde-2 -160 -140 -120 -100-80 -60 -40 -200 20 40 0 1 2 3 4 VGS (V) Daya keluar an ( dBm ) fundamental IMD orde-2 IMD orde-3 -140 -120 -100 -80 -60 -40 -200 20 40 -30 -25 -20 -15 -10 -5 0 5 10 Daya masukan (dBm) Daya keluaran (dBm)

4. KESIMPULAN

Kajian distorsi intermodulasi pada penguat daya RF LDMOS telah dilakukan. Hasil simulasi menunjukkan bahwa perilaku distorsi intermodulasi penguat daya dipengaruhi oleh bias, baik VGS maupun VDS, resistansi beban, dan level daya masukan. Hasil simulasi juga menunjukkan

bahwa secara umum ACPR meningkat terhadap kenaikan daya masukan.

DAFTAR PUSTAKA

[1] Saripudin, A., Hutabarat, M.T., and Alam, B.R., 2002, Characterization of Nonlinear Behavior of GaAs HFET Power Amplifier IC Based on Multitone Measurement and Simulation, IEEE-APCCAS, Singapore.

[2] Saripudin, A., Hutabarat, M.T., and Alam, B.R., 2003, Nonlinear Characterization of LDMOS RF Power Amplifier Under Multitone Excitation, Asia-Pacific Microwave Conference, Soul, South Korea.

[3] Ataei, Gholamreza, 2000, Design of Linear and Nonlinear Circuits Using Derivative Superposition, Ph.D dissertation in University College London.

[4] Qu, G., and Parker, A.E., 1997, Analysis of Intermodulation in HEMT Common Source Amplifier, ISRMAT.

[5] Maas, S.A., 1999, FET Models for Volterra Series Analysis, Applied Wave Research Inc. [6] Passiopoulos, G., Webster, D.R., Parker, A.E., and Haigh, D.G., 1995, Nonlinear