Diajukan untuk memenuhi salah satu syarat Memperoleh gelar Sarjana Teknik

Program Studi Teknik Elektro Fakultas Teknik Universitas Sanata Dharma

Disusun oleh :

Gregorius Agung Kus Arianto NIM : 005114001

PROGRAM STUDI TEKNIK ELEKTRO FAKULTAS TEKNIK

UNIVERSITAS SANATA DHARMA YOGYAKARTA

FINAL PROJECT

ERROR DETECTING USING LINEAR BLOCK CODE

(15,11)

BASED ON DIGITAL CIRCUIT

Presented as a Partial Fulfillment of the Requirements To obtain the Sarjana Teknik Degree

In Electrical Engineering Study Program

By :

GREGORIUS AGUNG KUS ARIANTO Student Number : 005114001

ELECTRICAL ENGINEERING STUDY PROGRAM ELECTRICAL ENGINEERING DEPARTMENT

ENGINEERING FACULTY SANATA DHARMA UNIVERSITY

Pernyataan Keaslian Karya

Saya menyatakan dengan sesungguhnya bahwa tugas akhir yang saya tulis ini tidak memuat karya atau bagian karya orang lain, kecuali yang telah disebutkan dalam kutipan dan daftar pustaka, sebagaimana layaknya karya ilmiah.

Yogyakarta,. Maret 2007 Penulis

PERSEMBAHAN

Hidup tanpa mimpi itu hambar rasanya, dan mimpi itu untuk

diwujudkan…………dengan cara: bangun, mandi, bersiap diri, dan

berangkat melaksanakan tugas dengan penuh tanggung jawab.

Doa, Harapan, dan Pasrah pada Tuhan adalah suatu kekuatan yang

besar untuk kita agar tidak menjadi orang yang lemah, tetap belajar,

berusaha, dan selalu optimis dalam melangkah, jangan pernah sombong

dan hargai orang lain.

Ku persembahkan karya ilmiah ini untuk:

Tuhan Yesus, Bunda Maria yang senantiasa mendampingi dalam belajar,

Bapak Laurentius Yuwono tercinta yang selalu memberikan doa,dan senantiasa

mendampingi anak-anaknya untuk memberikan semangat dan dukungan,

Istriku tercinta Lusia Ayuning Tyas yang memberi dorongan, doa dan senantiasa

menungguku, dan…….Maaf kalau sudah bikin repot,

Elisabeth Karina Ayu Swastika Arianto dan Si kecil, you are my sweet heart,

semangat dan cinta kasih kalian senantiasa bersamaku,

Kakak-kakakku tercinta, terima kasih untuk doa, kasih sayang, dan dukungan

INTISARI

Dalam pengiriman atau transmisi data secara digital dikenal istilah menyandikan suatu data (encoding), yaitu proses pengubahan data yang akan dikirimkan menjadi suatu bentuk sandi-sandi atau kode-kode tertentu. Salah satu sandi yang digunakan untuk mendeteksi dan mengoreksi kesalahan pada pengiriman data adalah sandi blok linear.

Penelitian ini akan mengimplementasikan deteksi error menggunakan sandi blok linear (15,11). Perancangan perangkat keras menggunakan IC TTL tipe 74LS, dan LED. IC TTL yang digunakan yaitu diantaranya 74LS76 yang digunakan sebagai pencacah modulo 30, IC 74LS74 yang digunakan sebagai register geser, IC 74LS75 yang digunakan sebagai penyimpan data masukan, LED yang digunakan sebagai penampil dari keluaran. Cara kerja dari rangkaian ini adalah data yang terdiri dari 11 bit pesan akan dikirim melalui rangkaian pengiriman data kemudian data akan masuk ke dalam rangkaian encoder. Keluaran dari encoder akan menjadi 15 bit yang terdiri dari 4 bir paritas dan 11 bit pesan. Kemudian ke lima belas bit tersebut akan diberi

error. Error bisa diletakkan pada bit paritas, bit pesan maupun keduanya. Kemudian

data tersebut akan dikirimkan masuk ke dalam rangkaian deteksi. Di dalam rangkain

ini error yang masuk akan dideteksi.

Hasil dari rancangan alat ini yaitu LED yang menyala jika terdapat error.

Error yang pasti terdeksi adalah error yang mempunyai jarak kurang dari 3 error

yaitu 1 error dan 2 error yang terletak di semua posisi. Error yang lebih dari 2 error

ABSTRACT

In data transmission, there is a term which is called data encoding that means changing the data that will be sent into certain codes. One of the codes that is used to detect and correct errors is linear block code.

This research will implement error detection using (15,11) linear block code. The hardware were using 74LS TTL IC and LED. The TTL IC that were used in this research were: 74LS76 as a counter for modulo 30, 74LS74 as a shift register, and 74LS75 as a data storage. LED was used as the output display. The device works by sending the 11 message bits data through the data transmission circuit. The data then go through the encoder. The output of the encoder will be 15 bits data consists of 4 parity bits and 11 message bits that will be given some errors. The errors can be put in the parity bit, in the message bit, or in both of the bits. Finally, the data will be sent into the detector circuit. In this detector circuit the errors will be detected.

KATA PENGANTAR

Puji dan syukur penulis panjatkan ke hadirat Tuhan Yang Maha Esa, oleh karena kasih dan penyertaan-Nya sehingga penulis dapat meyelesaikan Tugas Akhir yang berjudul “Deteksi Galat Menggunakan Sandi Blok Linear (15,11) Berbasis Rangkaian Digital”. Tugas Akhir ini disusun sebagai salah satu syarat untuk memperoleh gelar Sarjana pada jurusan Teknik Elektro, Fakultas Teknik Universitas Sanatha Dharma Yogyakarta. Dalam penyusunannya, banyak pihak yang telah membantu dan memberikan dukungan pada penulis, oleh karena itu, penulis ingin mengucapkan terima kasih kepada:

1. Ir. Greg Heliarko, S.J., S.S., B.S.T., M.A., M.Sc., sebagai Dekan Fakultas Teknik Universitas Sanata Dharma Yogyakarta.

2. Bapak Damar Wijaya, S.T., M.T. sebagai pembimbing yang membagikan semua ilmu-ilmu elektronika digitalnya dan pengalaman yang dimilikinya dalam membantu proses penyusunan tugas akhir ini.

3. Ibu Wiwien Widyastuti, S.T., M.T., sebagai Pembimbing Akademik Angkatan 2000 terimakasih telah berkenan membagi ilmu dan pengalaman yang dimilikinya dalam membantu proses penyusunan tugas akhir ini.

4. Bapak Ir. Iswanjono, M.T., selaku Penguji.

5. Bapak B. Djoko Untoro S., S.Si., M.T., selaku Penguji. 6. Ibu Ir. Th. Prima Ari Setyani, M.T., selaku Penguji.

7. Bapak Laurentius Yuwono yang selalu mendoakan, mendukung dan memberi semangat untuk anak-anaknya.

8. Istriku Lusia Ayuning Tyas dan Elisabeth Karina Ayu Swastika Arianto My Family….Terimakasih untuk kasih dan sayangnya.

10.Keluarga besar X-Pat: Ari “Plink” + Meity, Andhika “Pay” + Oi, Bowo “Dono” + Ai, Arip + Oni, Ari “Jenong” + Rina, Wisnu “Bobo”, Rio “Koplo” Jadikan ini sebuah Kisah Klasik Untuk Masa Depan guys……….

11.Teman-teman seperjuangan di TE 2000 : Aan“Bodong” terimakasih untuk semuanya, Bram“Mbut” Thanks untuk semangat dan dorongannya, Aas“ganyong”, Andi “gepeng”, Hiung, Puguh”kumis”, Fredi”kampret”, Joko”jred”, Bowo, David Kurniawan, Andre”cutik”, Suryo, Nico, Hari”poter”, dan teman-teman yang tidak mungkin saya sebutkan satu persatu.

Semoga Tuhan membalas segala kebaikan yang telah diberikan kepada penulis. Penulis sungguh sangat menyadari bahwa masih banyak kekurangan dalam pembuatan dan penyusunan Tugas Akhir ini, maka dari itu segala saran dan kritik yang bersifat membangun sangat diharapkan penulis.

Yogyakarta, Maret 2007

DAFTAR ISI

Hal.

HALAMAN JUDUL …...……….…i

HALAMAN PERSETUJUAN ...………..…iii

HALAMAN PENGESAHAN ……….….iv

PERNYATAAN KEASLIAN KARYA ……….. …v

HALAMAN PERSEMBAHAN ……….…..vi

INTISARI ……….vii

ABSTRACT ………vii

KATA PENGANTAR ………...ix

DAFTAR ISI ………..xi

DAFTAR TABEL………..xiv

DAFTAR GAMBAR……….xv

DAFTAR LAMPIRAN………..xvi

BAB I PENDAHULUAN 1.1.Latar Belakang……… ………1

1.2.Batasan Masalah………. ………....2

1.3.Tujuan Penelitian……….………2

1.4.Manfaat Penelitian………...………....2

1.5.Sistematika Penulisan ……….3

BAB II DASAR TEORI 2.1. Sandi Blok Linear………4

2.2. Matrik Generator……….6

2.2.1. Perancangan Matrik Generator……….7

2.4. Pengujian Sindrom……….13

2.5. Register………..14

2.5.1. Register Geser Paralel In Serial Out (PISO)………...15

2.5.2. Register Geser Serial In Serial Out (SISO)……….16

2.5.3. Register Geser Serial In Paralel Out (SIPO)………...17

2.6. Gerbang Logika Dasar………18

2.6.1. Gerbang AND...………...18

2.6.2. Gerbang OR……….19

2.6.3. Gerbang NOT………..20

2.6.4. Gerbang XOR………..21

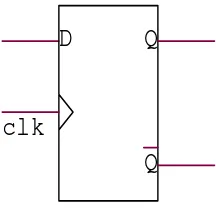

2.7. Flip Flop D……….22

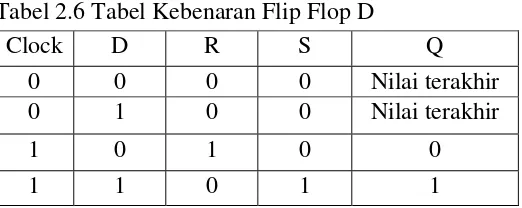

2.7.1. Flip Flop D dengan Preset dan Clear………..24

2.8. Dioda Cahaya (LED = Light Emiting Diode)……….25

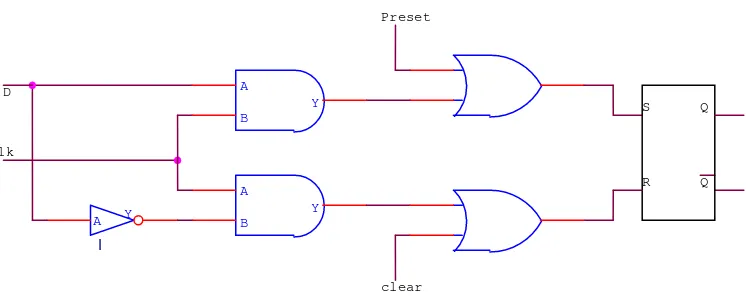

BAB III PERANCANGAN 3.1. Diagram Blok Rangkaian Sandi Blok………..27

3.2. Perancangan Hardwere Sandi Blok……….28

3.2.1. Perancangan Penyandi Sandi Blok………...28

3.2.1.1. Penyandi Sandi Blok………..29

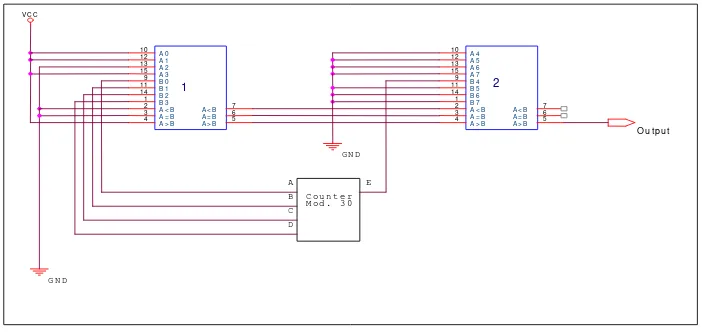

3.2.1.2.Komparator Pengendali Switch Pada Penyandi……..32

3.2.1.3. Pencacah / Counter Modulo 30……….35

3.2.1.4. Pembuat Galat………...37

3.2.1.5. Rangkaian Deteksi……….39

BAB IV HASIL PEMBAHASAN 4.1. Analisa Rangkaian Penyandi………..44

4.2. Analisa Rangkaian Pembuat Galat……….45

BAB V PENUTUP

5.1. Kesimpulan……….50

5.2. Saran………50

DAFTAR PUSTAKA ………..51

DAFTAR TABEL

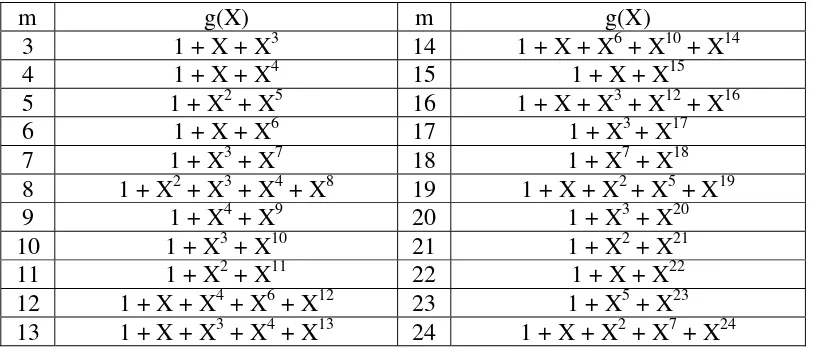

Tabel 2.1. Polinomial Primitif………9

Tabel 2.2. Tabel kebenaran untuk gerbang AND………..19

Tabel 2.3. Tabel kebenaran untuk gerbang OR……….20

Tabel 2.4. Tabel kebenaran untuk gerbang NOT………..21

Tabel 2.5. Tabel kebenaran untuk gerbang XOR………..22

Tabel 2.6. Tabel kebenaran untuk Flip Flop D………24

Tabel 3.1. Tabel kebenaran Switch………...34

Tabel 3.2. Tabel kebenaran Modulo 30………35

Tabel 4.1. Hasil keluaran penyandi………..44

Tabel 4.2. Pembuat Galat untuk beberapa posisi galat pada sandi (1 0 0 1 0 0 0 0 0 0 0 0 0 0 1 0)………46

DAFTAR GAMBAR

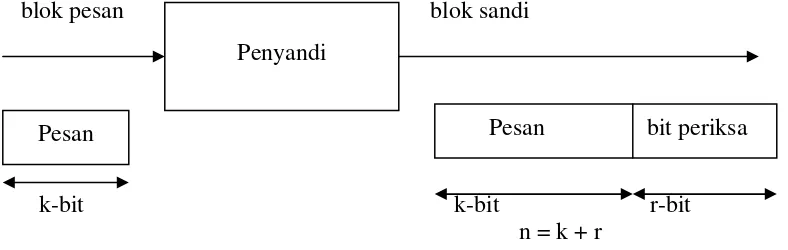

Gambar 2.1. Sandi Blok………4

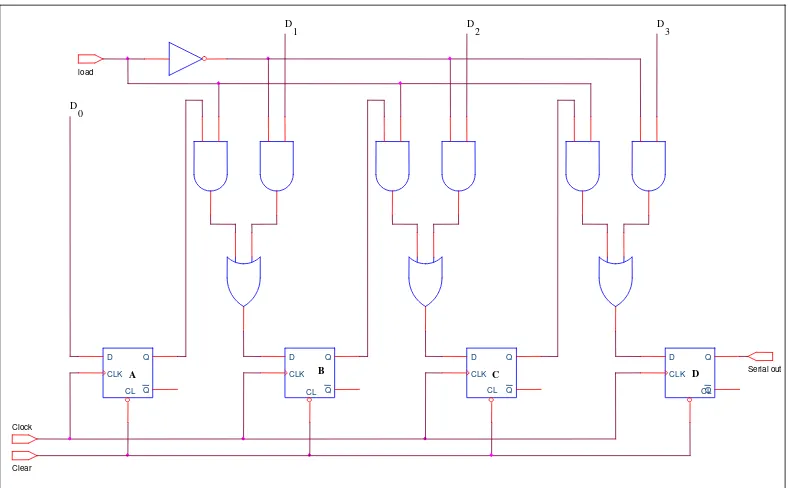

Gambar 2.2. Register Geser PISO 4 bit………..16

Gambar 2.3. Register Geser SISO 4 bit………..17

Gambar 2.4. Register Geser SIPO 4 bit………..18

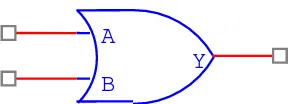

Gambar 2.5. Simbol logika gerbang AND……….18

Gambar 2.6. Simbol logika gerbang OR……….19

Gambar 2.7. Simbol logika gerbang NOT………..20

Gambar 2.8. Simbol logika gerbang XOR………..21

Gambar 2.9. Simbol logika untuk Flip Flop D………...22

Gambar 2.10. Rangkaian gerbang Flip Flop D………...23

Gambar 2.11. Rangkaian Gerbang flip flop D dengan preset dan clear………….25

Gambar 2.12. Rangkaian LED………26

Gambar 3.1. Diagram Blok……….27

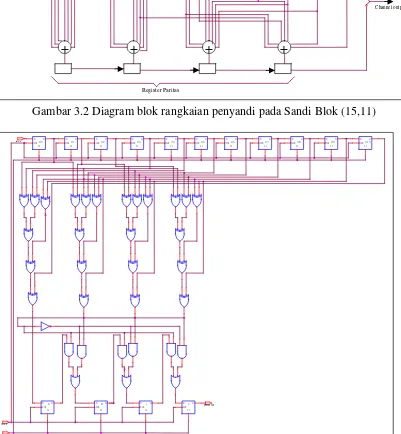

Gambar 3.2. Diagram blok rangkaian penyandi pada Sandi Blok (15,11)……….30

Gambar 3.3. Rangkaian digital untuk Ekoder……….30

Gambar 3.4. Keluaran unit kendali……….32

Gambar 3.5. Rangkaian komparator pada penyandi………...32

Gambar 3.6. Rangkaian digital Switch………35

Gambar 3.7. Rangkaian pencacah maju Modulo 30………37

Gambar 3.8. Rangkaian pembuat galat………38

Gambar 3.9. Gambar diagram blok Sindrom Sandi Blok (15,11)………41

DAFTAR LAMPIRAN

LAMPIRAN 1 Gambar 1 Register pada Enkoder………..L1 LAMPIRAN 2 Gambar 2 Register pada Sindrom……….L2 LAMPIRAN 3 Gambar 3 Komparator pada Enkoder………L3 LAMPIRAN 4 Gambar 4 Counter………..L4 LAMPIRAN 5 Gambar 5 Switch Enkoder………..L5 LAMPIRAN 6 Clock………..L6 LAMPIRAN 7 Rangkaian Enkoder………L7 LAMPIRAN 8 Rangkaian pembuat Galat………..L8 LAMPIRAN 9 Rangkaian Sindrom………L9 LAMPIRAN 10 Data Sheet

74LS04

74LS85

74LS86

74LS08

74LS32

74LS06

74LS173

74LS164

74LS74

BAB I

PENDAHULUAN

1.1.

Latar Belakang

Pada pengiriman atau transmisi data secara digital dikenal istilah menyandikan suatu data (encoding) yaitu proses pengubahan data yang akan dikirim menjadi suatu bentuk sandi-sandi atau kode-kode tertentu. Sering terdapat perbedaan antara data yang dikirim dengan data yang diterima. Hal ini disebabkan kegagalan dalam sistem transmisi. Kegagalan dapat bersifat sementara dan dapat pula bersifat permanen.

Galat dalam transmisi secara digital dapat didefinisikan sebagai perubahan dari bit “0” menjadi bit “1” dan sebaliknya, antara pengirim dan penerima. Galat yang terjadi merupakan hal yang fatal, sehingga perlu dideteksi untuk kemudian dikoreksi. Salah satu metode untuk mendeteksi dan mengoreksi galat pada pengiriman data adalah dengan metode Sandi Blok Linear.

1.2

. Batasan Masalah

Pada pelaksanaan dan penyusunan tugas akhir ini penelitian dibatasi permasalahannya sebagai berikut:

1. Sandi Blok Linear yang disimulasikan mempunyai data masukan 11 bit dan paritas 4 bit serta dengan data keluaran 15 bit

2. Simulasi dilakukan dengan menggunakan rangkaian digital untuk mendeteksi galat.

3. Simulasi dirancang untuk penyandi, pembuat galat dan pendeteksi kesalahan. 4. Masukan data (Input) menggunakan saklar dan tampilan dengan LED digunakan

sebagai penunjuk letak kesalahan.

1.3

. Tujuan Penelitian

Adapun tujuan yang ingin dicapai dalam penelitian ini adalah:

1.

Membuat rangkaian digital untuk deteksi galat Sandi Blok Linear (15,11)1.4

. Manfaat Penelitian

1.5

. Sistematika Penulisan

Pada penulisan tugas akhir ini penulis membuat sistematika penulisan sebagai berikut:

BAB I : PENDAHULUAN

Bab I berisi latar belakang masalah, batasan masalah, tujuan penelitian, manfaat penelitian, dan sistematika penulisan.

BAB II : DASAR TEORI

Bab II berisi dasar teori dari Sandi Blok dan dasar teori dari piranti atau komponen yang digunakan.

BAB III : PERANCANGAN

Bab III berisi diagram blok, diagram alir perancangan dan penjelasan diagram alir perancangan, rancangan peralatan yang meliputi pemilihan komponen serta penjelasan secara singkat tentang cara kerja peralatan tersebut.

BAB IV : HASIL DAN PEMBAHASAN

Bab IV berisi hasil pengamatan dan pembahasan, saerta spesifikasi yang diperoleh pada perancangan alat.

BAB V : PENUTUP

BAB II

DASAR TEORI

2.1. Sandi Blok Linear

Sandi Blok Linear adalah salah satu jenis sandi uji paritas yang mempunyai notasi (n, k). Penyandi mengubah blok k digit pesan (vektor pesan) menjadi blok yang lebih panjang dengan n digit kata sandi (vektor sandi), terbangun dari elemen alfabet yang diberikan. Jika alfabet terdiri dari dua elemen (0 dan 1), sandi adalah sandi biner yang terdiri dari digit-digit biner (bit). Pembahasan tentang sandi blok dibatasi pada sandi biner. (Damar Wijaya, 2002). Seperti terlihat pada gambar 2.1, bila

masing-masing sandi mempunyai 2k kata sandi yang dapat dinyatakan sebagai kombinasi

linear dari k vektor sandi secara bebas linear, maka disebut sebagai sandi Blok Linear. ( Iswanjono., 2001).

blok pesan blok sandi

pesa

Penyandi

Pesan bit periksa

Pesan

k-bit k-bit r-bit n = k + r

Pesan k-bit dari 2k urutan pesan yang berbeda disebut sebagai k-tuples (urutan

dari k digit). Blok n-bit dapat membentuk 2n urutan yang berbeda disebut n-tuples.

Prosedur penyandian mengalokasikan setiap 2k pesan k-tuples secara unik dipetakan

menjadi 2k kata sandi n-tuples. (Damar Wijaya, 2002)

Satu set n-tuples biner (Vn) disebut vector space dari medan biner. Medan biner ini mempunyai dua operasi yaitu penjumlahan dan perkalian, sehingga semua hasil operasi sama dengan elemen biner. Operasi aritmatika penjumlahan dan perkalian ditentukan dengan rumusan yang disepakati. Dalam medan biner, aturan untuk penjumlahan dan perkalian adalah sebagai berikut:

Penjumlahan (XOR) Perkalian 0 ⊕ 0 = 0 0 • 0 = 0

0 ⊕ 1 = 1 0 • 1 = 0

1 ⊕ 0 = 1 1 • 0 = 0

1 ⊕ 1 = 0 1 • 1 = 1

Operasi penjumlahan dengan lambang ⊕ menunjukkan penjumlahan

modulo-2. Untuk menentukan penyandian yang juga harus diketahui dahulu adalah

vector subspace. Vector ini adalah subset S vector space (Vn) hanya jika dapat

memenuhi persyaratan sebagai berikut:

1. Vektor dengan semua elemen 0 berada didalam S.

2.2.

Matrik Generator

Karena satu set vektor sandi yang membentuk sandi blok mempunyai

subspace berdimensi k dari vector space biner berdimensi n (k < n ), maka akan ada

satu himpunan n-tuples, kurang dari 2k

, yang dapat membangkitkan semua 2

k vektoranggota dari subspace. Sekelompok indipenden linear terkecil yang merentangkan

subspace disebut basis dari subspace, dan jumlah vektor dalam basis sama dengan

dimensi dari subspace. Setiap set basis dari k n-tuples yang indipenden linear

V1, V2, …. , Vk dapat digunakan untuk membangkitkan vektor-vektor sandi blok

yang diperlukan, karena setiap vektor sandi merupakan kombinasi linear dari

V1, V2, …. , Vk. Artinya setiap set dari 2k vektor sandi U dapat ditulis sebagai :

k kV m V m V m

U= 1 1+ 2 2+...+ ……….………...…(2.1) dengan mi = (0 atau 1) adalah digit pesan dan i = 1, 2, … , k.

Untuk mengatasi ukuran memori yang sangat besar, dapat dilakukan pembangkitan vektor sandi yang dibutuhkan saja, oleh karena itu kita bisa membentuk matrik generator. Pada dasarnya matrik generator dapat ditentukan dengan larik k × m. Matrik generator diambil dari vektor sandi yang membentuk

Vektor sandi biasanya ditunjukkan oleh vektor baris. Jadi bit paritas m dan

deretan bit pesan k, dituliskan sebagai vektor baris (matrik 1 × k yang mempunyai

satu baris dengan k kolom).

m = m1, m2, ….,mk

………...……….…..…(2.3)

Pembangkitan vektor sandi U, ditulis dalam notasi matrik sebagai hasil kali dari matrik m dan G :

U = mG………...……….(2.4) Jadi vektor sandi yang sesuai dengan vektor pesan adalah kombinasi linear dari baris matrik G. Karena sandi ditentukan oleh G, penyandi hanya perlu menyimpan k baris dari matrik G (tidak total 2k vektor sandi).

2.2.1. Perancangan Matrik Generator

Dalam pembuatan matriks generator untuk mendapatkan sandi blok dengan format sistematis diperlukan polinomial pembangkit. Polinomial yang dipilih adalah polinomial yang mempunyai pangkat tertinggi sama dengan panjang bit periksa.

Untuk membuat matriks generator G dan matriks periksa paritas H yang digunakan pada sandi blok linear dengan Hamming, dilakukan langkah sebagai berikut :

Dengan polinomial pembangkit, matriks generator dengan bentuk sistematis dapat dibuat dengan mudah. Jika Xn-k+1 dibagi dengan polinomial pembangkit g(X), dengan i = 0, 1, 2, … , 10, maka diperoleh :

X15-11+1 = ai (X) g(X) + bi (X) ...(2.5)

dengan bi (X) adalah sisa dalam bentuk :

bi (X) = bi0 + bi1X + … + bi,n-k-1X3 ………...……..(2.6)

Dari koefisien tersebut dibentuk matriks k x n sebagai berikut :

⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎣ ⎡ ⋅⋅ ⋅ ⋅⋅ ⋅ ⋅ ⋅ ⋅ ⋅⋅ ⋅ ⋅⋅ ⋅ ⋅⋅ ⋅ ⋅⋅ ⋅ = 1 0 0 0 1 0 0 0 1 3 , 10 1 , 10 0 , 10 3 , 1 11 10 3 , 0 01 00 b b b b b b b b b G

………(2.7)

matriks ini merupakan matriks generator dalam bentuk sistematis.

Polinomial dengan derajat m disebut primitif jika bilangan bulat positif terkecil n dimana p(x) dapat membagi Xn + 1 adalah n = 2m – 1. Sebagai contoh, p(X) = 1 + X + X4 dapat membagi X15 + 1 tetapi tidak dapat membagi setiap Xn + 1 untuk 1 n 15. Jadi 1 + X + X≤ ≤ 4 adalah polinomial primitif. Untuk bilangan m yang diberikan, terdapat lebih dari satu polinomial dengan derajat m.

Tabel 2.1. Polinomial Primitif

m g(X) m g(X) 3 1 + X + X3 14 1 + X + X6 + X10 + X14

4 1 + X + X4 15 1 + X + X15

5 1 + X2 + X5 16 1 + X + X3 + X12 + X16 6 1 + X + X6 17 1 + X3 + X17 7 1 + X3 + X7 18 1 + X7 + X18 8 1 + X2 + X3 + X4 + X8 19 1 + X + X2 + X5 + X19 9 1 + X4 + X9 20 1 + X3 + X20 10 1 + X3 + X10 21 1 + X2 + X21 11 1 + X2 + X11 22 1 + X + X22 12 1 + X + X4 + X6 + X12 23 1 + X5 + X23 13 1 + X + X3 + X4 + X13 24 1 + X + X2 + X7 + X24

Jika m = 4 (sama dengan panjang bit paritas), maka polinomial pembangkit yang digunakan adalah g(X) = 1 + X + X4 . Jika X4, X5, X6, X7, X8, X9, X10, X11, X12, X13, dan X14 dibagi dengan g(X), akan diperoleh :

X4 = g(X) + (1 + X) X5 = X g(X) + (X + X2) X6 = X2 g(X) + (X2 + X3)

X7 = (X3 + 1) g(X) + (1 + X + X3) X8 = (X4 + X + 1) g(X) + (1 +X2) X9 = (X5 + X2 + X) g(X) + (X + X3)

X10 = (X6 + X3 + X2 + 1) g(X) + (1 + X + X2) X11 = (X7 + X4 + X3 + X) g(X) + ( X + X2 + X3)

Sedangkan untuk data yang lain adalah sebagai berikut :

X4, X8, X9, X10 = (X6 + X5 + X4 + X3 + 1) g(X) + (1 + X + X3) X9, X10, X11 = (X7 + X6 + X5 + X4 + 1) g(X) + (1 + X)

X8, X9... X12 = (X8 + X7 + X6 + X4 + X2 + X + 1) g(X) + (1 + X3)

X4, X5... X14 = (X10 + X9 + X8 + X6 + X5 +X2 + 1) g(X) + (X3 + X2 + X + 1) Jika V adalah sisa ditambah dengan variabel yang dibagi, maka

:

V0 (X) = 1 + X

V1 (X) = X + X2

V2 (X) = X2 +X3

V3 (X) = 1 + X + X3

V4 (X) = 1 + X2

V5 (X) = X+ X3

V6 (X) = 1 + X + X2

V7 (X) = X + X2 + X3

V8 (X) = 1 + X + X2 + X3

V9 (X) = 1 + X2 + X3

V10 (X) = 1 + X3

V11 (X) = 1 + X + X3

V12 (X) = 1 + X

V13 (X) = 1 + X3

Koefisien polinomial v di atas diambil sebagai baris-baris dari matriks G, sehingga : ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎣ ⎡ = 1 0 0 0 0 0 0 0 0 0 0 1 0 0 1 0 1 0 0 0 0 0 0 0 0 0 1 1 0 1 0 0 1 0 0 0 0 0 0 0 0 1 1 1 1 0 0 0 1 0 0 0 0 0 0 0 1 1 1 0 0 0 0 0 1 0 0 0 0 0 0 0 1 1 1 0 0 0 0 0 1 0 0 0 0 0 1 0 1 0 0 0 0 0 0 0 1 0 0 0 0 0 1 0 1 0 0 0 0 0 0 0 1 0 0 0 1 0 1 1 0 0 0 0 0 0 0 0 1 0 0 1 1 0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 1 0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 1 G

Nilai vektor sandi sistematis (U) yang nantinya akan digunakan dalam input

data dapat dinyatakan sebagai berikut :

U = p1, p2, … , p4, m1, m2, … ,m11 ……….…….(2.8)

dengan p1, p2, … , p4 adalah bit – bit paritas

m1, m2, … ,m11 adalah bit – bit pesan

p1 = m1p11 + m2p21 + … + m11p11,1

p2 = m1p12 + m2p22 + … + m11p11,2

pn-k = m1p1,(n-k) + m2p2,(n-k) + … + mkpk,(n-k)

sehingga diperoleh :

p1 = m1p1,1 + m2p2,1 + …. + m8p8,1 + m9p9,1 + m10p10,1 + m11p11,1

p2 = m1p1,2 + m2p2,2 + …. + m8p8,2 + m9p9,2 + m10p10,2 + m11p11,2

p3 = m1p1,3 + m2p2,3 + …. + m8p8,3 + m9p9,3 + m10p10,3 + m11p11,3

2.3. Matrik Uji Paritas

Matrik uji paritas, H, digunakan untuk mengawasandi (decode) vektor sandi yang diterima. Untik setiap matrik generator (k x n), G, terdapat matrik H (n – k) X n, sedemikian sehingga baris pada G ortogonal dengan baris H, dan GHT= 0. HT adalah transpos dari H dan 0 adalah matrik nol k X (n – k). Untuk memenuhi ortogonalitas, komponen matrik H ditulis :

H = [ In - k PT ] ...(2.9)

dan matrik HT dapat ditulis :

HT = ⎥⎦ ⎤ ⎢⎣ ⎡ −

P

In k

= ………...………...……….(2.10)

⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎣ ⎡ − − − ) ( , 2 1 ) ( , 2 22 21 ) ( , 1 12 11 ... ... ... 1 ... 0 0 . . .. . . . 0 ... 1 0 0 ... 0 1 k n k k k k n k n P P P P P P P P P

Perkalian UHT untuk setiap vektor sandi U yang dihasilkan G, dengan matrik HT, menghasilkan vektor nol :

UHT = p1 + p1, p2 + p2, ..., pn-k + pn-k = 0 ...(2.11)

dengan p1, p2, p3, ..., pn-k adalah bit – bit paritas.

set kata sandi yang benar. Matrik U adalah vektor sandi yang dibangkitkan oleh

matrik G jika, dan hanya jika, UHT = 0.

2.4. Pengujian Sindrom

Setelah data sampai di pendeteksi galat, dengan melihat bit data dan bit paritas yang ada, maka akan dibangkitkan suatu kode (sindrom) yang akan menunjukkan dan mengoreksi letak bit yang mengalami galat pada saat pengiriman. Selanjutnya dengan melihat sindrom yang ada, galat akan diperbaiki oleh rangkaian pengoreksi.

Jika r = r1,r2,….,rn adalah vektor sandi yang diterima, yang merupakan hasil

dari pengiriman U = u1,u2,….,uk, maka r dapat ditulis sebagai berikut :

r = U + e....………...……….(2.12) dengan e = vektor galat yang terjadi pada kanal yaitu e = e1,e2,…,ek. Pengujian

sindrom i didapat dari persamaan :

S = rHT…....………...………(2.13) Sindrom adalah hasil uji paritas yang dilakukan pada r untuk menentukan apakah r merupakan anggota himpunan kata sandi yang benar. Jika r adalah anggota himpunan kata sandi, maka S akan sama dengan 0. Jika r mengandung galat yang dapat terditeksi, maka S mempunyai elemen bernilai tidak nol yang dapat menandai adanya pola galat tertentu.

S = (U + e)HT

=UHT + eHT ……….……….(2.14) karena UHT = 0 untuk semua himpunan kata sandi, maka :

S = eHT ...………...……(2.15) Pengujian sindrom yang dilakukan dari persamaan (2.12) sampai (2.15), yang dilakukan pada vektor sandi yang terkena galat, maupun pada pola galat itu sendiri menghasilkan sindrom yang sama. Dalam matrik uji paritas terdapat dua hal yang penting adalah :

1. Tidak ada kolom H yang semua elemennya bernilai nol, atau galat yang terjadi pada posisi vektor sandi yang bersesuaian tidak akan memberikan efek pada sindrom dan tidak dapat terdeteksi.

2. Semua kolom H harus unik. Jika ada dua kolom yang sama, maka galat pada dua posisi vektor sandi yang bersesuaian tidak dapat dibedakan.

2.5. Register

Register geser digunakan untuk menyimpan sementara antar unit pengelola data dan penyandi, serta dapat digunakan dalam hal lain dalam suatu sistem digital. Salah satu karakteristik register geser, adalah bagaimana data dimuat ke dan dibaca dari unit-unit penyimpanannya. Empat kategori register geser adalah :

1. Serial In- Serial Out 2. Serial In- Paralel Out 3. Paralel In- Serial Out 4. Paralel In- Paralel Out

2.5.1. Register Geser Paralel In Serial Out (PISO)

Pada register ini data dimasukkan secara paralel dan data keluaran dikeluarkan secara seri. Data pada D0 pada gambar 2.2 akan dimasukkan langsung

kedalam D-FF A, tetapi data D1, D2, dan D3 menunggu keluaran dari D-FF

sebelumnya. Seperti pada data D1, data yang masuk akan di AND-kan terlebih dahulu

dengan data load yang di NOT-kan, kemudian data load yang tidak di NOT-kan akan di AND-kan dengan data keluaran D0, setelah melalui gerbang AND, data akan

dimasukkan ke gerbang OR, keluaran dari gerbang OR ini akan menjadi masukan pada D-FF B. Dan begitu seterusnya sampai dengan data yang diinginkan.

D

CLK Q

Q CL D

CLK Q

Q CL D

CLK Q

Q CL D

CLK Q

Q CL

load

Serial out

Clear Clock

D

D D D

0

1 2 3

D C

B A

Gambar 2.2 Register Geser PISO 4 bit

2.5.2. Register Geser Serial In Serial Out (SISO)

Register geser SISO diperlihatkan pada gambar 2.3 dengan data MSB dimasukkan terlebih dahulu. Saat pulsa clock pertama tiba, flip flop A akan terisi data MSB. Ketika pulsa clock kedua tiba, flip flop B akan terisi data flip flop A, dan flip flop A akan terisi oleh data masukan berikutnya. Ketika pulsa clock ketiga tiba, flip flop C akan terisi oleh data flip flop B, flip flop B akan terisi oleh data flip flop A, dan flip flop A akan terisi oleh data masukan berikutnya. Ketika pulsa clock keempat

tiba, flip flop D akan terisi data pada flip flop C, flip flop C akan terisi data flip flop B, flip flop B akan terisi data flip flop A, dan flip flop A akan terisi data

Jadi, jika data input 4 bit, maka pulsa clock yang dibutuhkan adalah 4 kali. Sedangkan clear berfungsi untuk me-reset data pada setiap flip flop. Clear akan bekerja jika berlogika 1.

Clear Data input

Clock

Serial out D

CLK Q

Q CL

D

CLK Q

Q CL

D

CLK Q

Q CL

D

CLK Q

Q CL

A B C D

Gambar 2.3 Register geser SISO 4 bit

2.5.3. Register Geser Serial In Paralel Out (SIPO)

Register geser SIPO diperlihatkan pada gambar 2.4 dengan data MSB dimasukkan terlebih dahulu. Saat pulsa clock pertama tiba, flip flop A akan terisi data MSB dengan keluaran QA. Ketika pulsa clock kedua tiba, flip flop B akan terisi data flip flop A, dan flip flop A akan terisi oleh data masukan berikutnya dengan keluarannya adalah QB. Ketika pulsa clock ketiga tiba, flip flop C akan terisi oleh data flip flop B, flip flop B akan terisi oleh data flip flop A, dan flip flop A akan terisi oleh data masukan berikutnya dan keluarannya adalah QC. Dan ketika pulsa clock

Jadi jika input 4 bit, maka pulsa clock yang dibutuhkan adalah 4 kali. Sedangkan clear berfungsi untuk me-reset data pada setiap flip flop. Clear akan bekerja jika berlogika 1.

D

CLK Q

CL

D

CLK Q

CL

D

CLK Q

CL

D

CLK Q

CL Data input

QA QB QC QD

Clok

Clear

Gambar 2.4 Register geser SIPO 4 bit

2.6.

Gerbang Logika Dasar

2.6.1. Gerbang

AND

Gerbang AND mempunyai dua atau lebih masukan atau keluaran. Keluaran dari gerbang AND akan bernilai logika 1 jika semua masukan bernilai juga logika 1. Oleh karena itu gerbang AND kadang-kadang juga disebut “gerbang semua atau tidak”. Simbol logika gerbang AND dua masukan dapat dilihat pada gambar 2.5.

A

B

Y

Dalam Aljabar Boolean, persamaan untuk gerbang AND dapat ditulis :

..…….(2.16)

Atura

Tabel kebenaran dari gerbang logika AND dua masukan ditunjukkan pada tabel 2.2.

Y = A • B………

n-aturan aljabar Boolean mengatur bagaimana gerbang AND beroperasi. Aturan formal untuk fungsi AND adalah :

A • 0 = 0

A • 1 = A

A • A = A

A • A = 0

Tabel 2.2 Tabel kebenaran untuk gerbang logika AND dua masukan B A Y

0 0 1 1

0 1 0 1

0 0 0 1

2.6.2. Gerbang

OR

asukan dan satu keluaran. Keluaran dari ge

Gerbang OR mempunyai dua atau lebih m

mbar 2.6 Simbol logika gerbang Ga

Persamaan dalam Aljabar Boolean untuk gerbang OR adalah :

………...(2.17) Aturan-aturan aljaba

Tabel kebenaran dari gerbang OR dua masukan ditunjukkan pada tabel 2.3.

B A Y

OR

Y = A + B………

r Boolean mengatur bagaimana suatu gerbang OR akan

beroperasi. Aturan-aturan formal untuk fungsi OR adalah : A + 0 = A

A + 1 = 1 A + A = A A + A = 1

Tabel 2.3 Tabel kebenaran untuk gerbang OR dua masukan

0 0 0

0 1 1

1 0 1

1 1 1

.6.3. Gerbang

NOT

ika di atas mempunyai paling sedikit dua masukan dan satu keluaran. Akan tetapi gerbang NOT hanya mempunyai satu masukan dan satu

2

Semua gerbang log

A

B

keluaran. Gerbang NOT berfungsi untuk memberikan suatu keluaran yang tidak sama (terbalik) dengan masukan. Jika nilai masukan gerbang NOT bernilai logika 0, maka keluaran logika akan bernilai 1. Sebaliknya jika masukan gerbang bernilai logika 1, maka keluarannya akan bernilai logika 0. Oleh karena itu gerbang NOT sering kali disebut “pembalik”. Gerbang NOT disimbolkan seperti pada gambar 2.7

A Y

Gambar 2.7 Simbol logika gerbang NOT

Persamaan Aljabar Boolean untuk gerbang NOT adalah sebagai berikut: _

…..………...(2.18)

NOT.

_ _

_

0, ma 1

Tabel k benara dari g pada tabel 2.4. Tabel 2 Tabe keben ran ge T

A Y

Y = A………

Aturan-aturan aljabar Boolean mengatur aksi dari pembalik atau gerbang Aturan aljabar Boolean formal untuk gerbang NOT adalah :

0 = 1 1 = 0 Bila A = 1, maka A = 0

_

Bila A = ka A = =

A = A

e n erbang NOT ditunjukkan .4 l a rbang NO

0 1

2.6.4. Gerbang

XOR

Gerbang XOR disebut sebagai gerbang “setiap tetapi tidak semua”. Istilah singkat sebagai XOR. Gerbang XOR hanya akan terbuka bila muncul satuan bilangan ganjil pada m

Gam XOR

_ _

Y = A • …...………..(2.19)

Tabel 2.5 Tabel kebenaran gerbang XOR

B A Y

Ekslusif-OR sering kali di

asukan. Gerbang XOR dapat disebut sebagai suatu rangkaian pemeriksa bit-ganjil. Gerbang XOR disimbolkan seperti pada gambar 2.8

A

B

Y

bar 2.8 Simbol logika gerbang

Aljabar Boolean untuk gerbang XOR dapat dituliskan sebagai berikut: B + A • B ....………

Tabel k benara dari ge n erbang XOR ditunjukkan pada tabel 2.5.

0 0

0 1

0 1 1

1

0 1

2.7. Flip Flop D

Adapun flip flop D (delay = tunda) merupakan flip flop yang dapat mencegah ran sampai berlangsungnya pulsa clock. Flip flop D tersebut hanya m

nilai D mencapai kelua

empunyai masukan data tunggal (D) dan masukan clock (CK). Flip flop D sering disebut dengan flip flop tunda. Nama ini menggambarkan dengan tepat operasi unit ini. Apapun bentuk masukan pada masukan data (D), masukan tersebut akan tertunda selama satu pulsa detak untuk mencapai keluaran normal (Q). Data dipindahkan ke keluaran pada transisi pulsa detak RENDAH ke TINGGI. Simbol logika untuk flip flop D adalah seperti gambar 2.9

clk

Q

D

Q

Gambar 2.10 Rangkaian Gerbang Flip flop D

Cara Kerja Flip Flop D adalah sebagai berikut :

1. Bila D=1 dan clock dan karena D

dihubungkan ke gerbang NOT sebelum masuk gerbang AND-B, maka keluaran gerbang AND-B akan bernilai 0, sehingga S=1 dan R=0, keluaran Q=1.

2. Bila D=1 dan clock=0, maka keluaran gerbang AND-A adalah 0 dan keluaran gerbang AND-B adalah 0, sehingga S=0 dan R=0 keluaran Q=tetap pada nilai terakhir (kondisi tertahan).

3. Bila D=0 dan clock=1, maka keluaran gerbang AND-A adalah 0 dan keluaran gerbang AND-B adalah 1, sehingga S=0 dan R=1 maka keluaran Q=0.

4. Bila D=0 dan clock=0, maka keluaran gerbang AND-A adalah 0 dan keluaran gerbang AND-B adalah 0, sehingga S=0 dan R=0, keluaran Q=tetap pada nilai terakhir (kondisi tertahan). Untuk tabel kebenarannya dapat dilihat pada tabel 2.6.

=1, maka keluaran gerbang AND-A adalah 1

Q

A Y

A

B

Y

Q S

S

R D

clock

A

B

Tabel 2.6 Tabel Kebenaran Flip Flop D

Clock D R S Q

0 0 0 0 Nilai terakhir 0 1 0 0 Nilai terakhir

1 0 1 0 0

1 1 0 1 1

Dari tabel terlihat bahwa bila = apun nilai D tidak berpengaruh (Q = nilai terakhir). Keluaran Q akan berubah bila clock = 1. Pada flip flop D,

eluaran terlarang tidak didapatkan, sehingga terbebas dari keluaran terlarang.

Rangkaian flip flop sering mengeluarkan data dalam kondisi acak kalau kita memberikan suatu sinyal paksa agar keluaran sesuai dengan yang kita inginkan. Sinyal paksa tersebut adalah preset

dan clear. Preset yang tinggi memaksa keluaran Q berlogika tinggi. Clear yang tinggi

memaksa keluaran Q berlogika rendah. Preset dan clear adalah masukan tidak serempak, karena masukan ini mengaktifkan D flip flop tanpa tergantung pada pulsa

clock. Masukan tak serempak tersebut untuk rangkaian aktif tinggi. Sedangkan untuk

rangkaian aktif rendah, berlogika sebaliknya. Kalau dibuat rangkaian gerbangnya, maka akan tampak seperti pada gambar 2.11.

clock 0, maka berap

k

2.7.1. Flip flop D dengan

Preset

dan

Clear

Preset

clear

S

A Y

I

R Q

A

B

Y

Q

A

B

Y

clk D

Gambar 2.11 Rangkaian Gerbang flip flop D dengan preset dan clear aktif tinggi

2.8. Dioda cahaya (LED

= Light Emiting Diode

)

Dioda atau LED, adalah jenis dioda yang apabila diberi tegangan prasikap maju (forward bias voltage), elektron-elektron yang terdapat pada daerah transisi akan melepaskan energinya. Selanjutnya energi dari elektron-elektron tersebut akan menghasikan cahaya atau panas.

Cahaya yang dipancarkan oleh LED ada bermacam-macam, misalnya kuning, merah, hijau, dan biru. Bentuknya pun bermacam-macam pula seperti bulat, bujur sangkar, persegi empat dan segitiga.

dibutuhkan untuk menghidupkan LED sebesar 1,7 volt. Agar LED yang digunakan dapat menyala maka diberikan suatu pembatas arus yang melewati LED yaitu dibatasi dengan resistor. Resistor ini dipasangkan secara seri dengan LED seperti pada gambar 2.12.

VCC

GND R

Gambar 2.12 Rangkaian LED Nilai resistor dapat dicari dengan rumus :

I Vled Vcc

BAB III

PERANCANGAN

3.1 Diagram Blok Rangkaian Sandi Blok

Diagram blok rangkaian Sandi Blok dapat dilihat pada gambar 3.1. Bit data yang akan dikirim dimasukkan dengan menggunakan saklar, bit paritas ini akan dikirimkan secara serial dengan bit data yang ada. Pada rangkaian penyandi, data masukkan yang diterima menjadi 15 bit, yaitu terdiri dari 11 bit informasi dan 4 bit paritas. Setelah data diterima, data tersandi masuk pada rangkaian pembuat galat. Data tersandi yang mengandung bit galat akan dikirim secara serial dan diterima oleh rangkaian deteksi sebagai data terima. Data terima masuk kedalam rangkaian deteksi guna menentukan apakah dalam data yang diterima terdapat galat atau tidak.

LED

15 bit

1 error

Deteksi galat Pembuat

galat ENCODER

11 bit data

4 bit paritas

Pembangkit paritas Data input

Saklar sebagai

LED LED LED

Perancangan hardware Sandi Blok ini terdiri dari beberapa bagian yaitu : penyandi, pembuat galat, pendeteksi galat. Bagian ini akan membahas perancangan

hardware pada tiap bagian.

3.2 Perancangan

Hardware

Sandi Blok

Pada perancangan, LED digunakan sebagai penampil, baik sebagai masukan maupun keluaran. Agar LED dapat menyala maka diberikan suatu pembatas arus yang melewati LED yaitu dengan memberikan resistor. Resistor dapat dipasangkan secara seri dengan LED seperti pada gambar 2.10. Bila tegangan untuk menyalakan LED adalah sebesar 1,7 volt, dan arus yang dibutuhkan adalah 10mA, maka :

Ω = =

⋅ − =

− =

−

330 01 , 0

3 , 3

10 10

) 7 , 1 5 (

) (

3

A V

A V V

I V VCC

R LED

Pemilihan resistor ini untuk menjaga agar LED tidak mudah padam.

3.2.1 Perancangan Penyandi Sandi Blok

S0 = b0,0 + b3,0 + b4,0 + b6,0 + b8,0 + b9,0 + b10,0

S1 = b0,1 + b1,1 + b3,1 + b5,1 + b6,1 + b7,1 +b8,1

S2 = b1,2 + b2,2 + b4,2 + b6,2 + b7,2 + b8,2 + b9,2

S3 = b2,3 + b3,3 + b5,3 + b7,3 + b8,3 + b9,3 + b10,3

3.2.1.1 Penyandi Sandi Blok

Pada pengiriman data, masukan berasal dari saklar yang memberikan bit “0” dan “1” dan sebagai penampil masukan tersebut adalah LED. LED akan menyala bila saklar ON (logika 1) dan akan padam bila saklar OFF (logika 0).

Pada rangkaian penyandi, komponen – komponen yang digunakan meliputi

saklar, LED, resistor, 4 buah IC 74LS173 yang masing – masing berisi 4

delay flip flop, 5 buah IC 74LS08 yang masing – masing berisi 10 gerbang AND 2

Channel output

Input U0 U1 U2 U3 U4 U5 U6 U7 U8 U9 U10

+ +

+

+

Register Paritas

Register Pesan

Gambar 3.2 Diagram blok rangkaian penyandi pada Sandi Blok (15,11)

B

data in D Q

CLK CL Q D CLK CL CLEAR A D U3 Q D CLK CL U0 Q D CLK CL U1 Q D CLK CL U2 U4 Q D CLK CL Q D CLK CL Q D CLK CL

U5 U6 U7

SERIAL OUT Q D CLK CL Q D CLK CL Q D CLK CL Q D CLK CL U8 Q D CLK CL Q D CLK CL CLOCK U9 C Q D CLK CL U10

Pada rangkaian penyandi ini, pesan U yang terdiri dari 11 buahregisterpesan yaitu U0, U1, U2, U3, U4, U5, U6, U7, U8, U9, U10, yang disandikan dimasukan kedalam

register pesan dan sekaligus juga kedalam channel (output) dan 4 buah register paritas yaitu V0, V1, V2, dan V3 .

Setelah pesan memenuhi register pesan, kemudian digit paritas dimasukkan ke dalam penjumlahan modulo 2, dengan kondisi terhubung bila bernilai “1” dan tidak terhubung bila bernilai “0”. Digit dalam uji paritas dibentuk dari keluaran dari penjumlahan modulo 2.

Setelah bit-bit paritas terbentuk, maka keluaran dari rangkaian ini akan masuk ke dalam rangkaian register. Pada register ini data dimasukkan secara paralel dan data keluaran dikeluarkan secara seri. Data pada D0 akan dimasukkan langsung kedalam

D-FF A, tetapi data D1, D2, dan D3 menunggu keluaran dari D-FF sebelumnya.

Seperti pada data D1, data yang masuk akan di AND-kan terlebih dahulu dengan data

load yang di NOT-kan, kemudian data load yang tidak di NOT-kan akan di AND-kan dengan data keluaran D0, setelah melalui gerbang AND, data akan dimasukkan ke

gerbang OR, keluaran dari gerbang OR ini akan menjadi masukan pada D-FF B. Dan begitu seterusnya sampai dengan data yang diinginkan.

3.2.1.2 Komparator Pengendali

Switch

Pada Penyandi

Komparator ini dibuat untuk memilih data yang akan dikeluarkan. Data yang dikirim berjumlah 11 bit. Jadi clock yang dibutuhkan adalah 11 clock. Clock

akan menjalankan counter, ketika counter mencacah dari 0 sampai 11 clock yang dibutuhkan sebanyak 11 clock, maka keluaran dari komparator akan bernilai 1. Setelah cacahan ke 11, keluaran kompartor akan bernilai 0. Ketika komparator bernilai 0 maka isi register terakhir akan keluar. Gambar 3.4 keluaran unit kendali.

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34

clock output

Gambar 3.4 Keluaran unit kendali

2 1 0 1 2 1 3 1 5 9 1 1 1 4 1 2 3 4 7 6 5 A 4 A 5 A 6 A 7 B 4 B 5 B 6 B 7 A < B A = B A > B

A < B A = B A > B

C o u n t e r

1 1 0 1 2 1 3 1 5 9 1 1 1 4 1 2 3 4 7 6 5 A 0 A 1 A 2 A 3 B 0 B 1 B 2 B 3 A < B A = B A > B

A < B A = B A > B

E

G N D

O u tp u t G N D

M o d . 3 0

V C C

A B C D

Gambar 3.5 Rangkaian komparator pada penyandi

Pada komparator 1 masukan A (A0, A1, A2, A3) akan diberi masukan

data 1 0 1 1 dengan cara menyambungkan ke Vcc untuk mendapatkan nilai 1 dan ke

ground untuk mendapatkan nilai 0. Pada komparator 2 masukan A (A4, A5, A6, A7)

akan disambungkan dengan ground. Pada komparator 1 masukan B (B0, B1, B2, B3)

akan di beri masukan data A, B, C, D yang merupakan keluaran dari counter modulo 30. Masukan B pada komparator 2 (B4) akan diberi masukan data E dan yang

lainnya (B5, B6, B7) akan disambungkan ke ground. Keluaran di-set agar A>B dengan

cara menyambungkan cascading input A>B dengan Vcc pada komparator 1 saja dan

cascading input pada komparator 2 diberi masukan dari keluaran komparator 1.

Keluaran yang digunakan adalah keluaran pada komparator 2 yaitu A>B.

Pada rangkaian penyandi digunakan switch yang berfungsi sebagai pengatur data keluaran dari data masukan maupun pada register. Switch berfungsi sebagai pengatur data masukan ke dalam register, apakah jumlah data yang masuk

data 11 bit, switch akan on dan setelah data 11 bit tersebut terkirim maka switch akan

off. (Gambar rangkaian lihat gambar 5 L5).

Switch berfungsi sebagai pengatur data keluaran, baik dari data masukan

maupun data dari isi register terakhir. Proses pertama, data akan dimasukkan kedalam register dan dikirimkan sehingga switch akan memilih keluaran, jika K bernilai 0 maka switch akan memilih register sebagai keluarannya, dan jika K bernilai 1 maka

switch akan memilih data terkirim sebagai keluaran. Setelah data terkirim habis

dikirimkan dan dikeluarkan maka isi register merupakan paritas. Supaya isi register tidak berubah, switch dibuka sedangkan paritas dikirimkan. Berikut ini akan ditunjukkan perancangan switch menggunakan tabel kebenaran dan peta Karnough. Tabel 3.2. Tabel kebenaran switch.

Data (D)

Register (R)

Kendali (K)

Output

Dari tabel 3.2 dapat dibuat peta Karnough sebagai berikut.

K

K

D

D D

R

R R R

D 0 1

1 0 0 1

1 0

Dari peta karnough diatas didapat D·K + R·K yang dapat diimplementasikan dalam rangkaian digital sepaerti gambar 3.6.

Output R

K

D

Gambar 3.6 Rangkaian digital switch .

Data terkirim selain akan masuk kedalam register juga akan langsung dikeluarkan melalui switch. Pada kondisi itulah isi register terakhir akan dikeluarkan.

3.2.1.3 Pencacah/

Counter

Modulo 30

balik dengan gerbang NAND. Berdasarkan tabel 3.3 akan dibahas pembuatan counter

menurut perhitungan digital.

Tabel 3.3. Tabel Kebenaraan Modulo 30

Data masukkan

No. E D C B A

0 0 0 0 0 0

1 0 0 0 0 1

2 0 0 0 1 0

3 0 0 0 1 1

4 0 0 1 0 0

5 0 0 1 0 1

6 0 0 1 1 0

7 0 0 1 1 1

8 0 1 0 0 0

9 0 1 0 0 1

10 0 1 0 1 0

11 0 1 0 1 1

12 0 1 1 0 0

13 0 1 1 0 1

14 0 1 1 1 0

15 0 1 1 1 1

16 1 0 0 0 0

17 1 0 0 0 1

18 1 0 0 1 0

19 1 0 0 1 1

20 1 0 1 0 0

21 1 0 1 0 1

22 1 0 1 1 0

23 1 0 1 1 1

24 1 1 0 0 0

25 1 1 0 0 1

26 1 1 0 1 0

27 1 1 0 1 1

28 1 1 1 0 0

29 1 1 1 0 1

30 1 1 1 1 0

Cacahan normal setelah 11101 adalah 11110. Agar 11110 terlompati menjadi 00000, maka keluaran dari flip flop A dan flip flop E diumpan balik menggunakan gerbang NAND. Keluaran dari gerbang NAND akan terhubung dengan clear pada masing- masing flip flop. Dengan demikian setelah clock ke – 30 tiba semua flip flop

akan direset. Gambar 3.7 rangkaian pencacah maju modulo 30 dengan menggunakan rangkaian digital. PRESET E 330 LED C J CLK K Q Q PR CL D CLOCK LED 330 LED LED 330 B 330 A GND VCC 330 LED J CLK K Q Q PR CL J CLK K Q Q PR CL J CLK K Q Q PR CL J CLK K Q Q PR CL

Gambar 3.7 Rangkaian pencacah maju modulo 30

3.2.1.4 Pembuat Galat

Pengiriman data antara penyandi dan deteksidilakukan secara paralel. Maka untuk itu digunakan rangkaian pembuat galat. Rangkaian ini berfungsi untuk

mengubah posisi keluaran penyandi Q ke posisi Q dengan menggunakan saklar.

Rangakaian pembuat galat dibuat setelah sandi keluar dari penyandi, hanya

saja salah satu dari keluaran flip flop yang digunakan adalah keluaran Q yang

dihubungkan oleh switch (Sw) pada salah satu flip flop pada gambar 3.8. Switch ini harus dikembalikan lagi pada keluaran Q setelah mendapatkan clock. Kondisi ini

untuk menjaga agar bit yang berikutnya tidak terkena galat. Keluaran Q ini yang

330 D CLK Q Q CL D CLK Q Q CL 330 330 D CLK Q Q CL 1 LED GND 330 D CLK Q Q CL 330 D CLK Q Q CL LED 330 VCC_CIRCLE GND D CLK Q Q CL 330 LED 330 VCC D CLK Q Q CL LED 0 LED Clk D CLK Q Q CL 330 D CLK Q Q CL Clear 1 LED 330 0 Output E d LED LED LED D CLK Q Q CL LED LED LED LED D CLK Q Q CL 330 LED 330 VCC GND LED VCC_CIRCLE 330 D CLK Q Q CL D CLK Q Q CL 330 D CLK Q Q CL D CLK Q Q CL 330

Gambar 3.8 Rangkaian pembuat galat

3.2.1.5 Rangkaian Deteksi

Dari matriks generator bisa diperoleh sebuah matriks H sebagai berikut :

maka dari matriks H ini kita bisa membuat matriks H transpos (HT) sebagai berikut :

⎥⎥

⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎣ ⎡ = 1 0 0 1 1 1 0 1 1 1 1 1 1 1 1 0 0 1 1 1 1 0 1 0 0 1 0 1 1 0 1 1 1 1 0 0 0 1 1 0 0 0 1 1 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 T H

Perancangan rangkaian deteksi sandi blok (15,11) ini dilakukan dengan mengacu pada substitusi persamaan (2.12) dan (2.13), sehingga didapatkan persamaan (2.11) sebagai berikut :

Jika, U = 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 r = 0 1 1 1 0 0 0 1 0 0 1 1 0 1 0 + maka, e = 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 Sehingga S = rHT bisa didapatkan sebagai berikut :

S = [ 0 1 1 1 0 0 0 1 0 0 1 1 0 1 0 ] HT

sedangkan untuk S = eHT adalah sebagai berikut : S = [ 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 ] HT = [ 1; 0; 0; 0 ]

= [ 1 0 0 0 ] = sindrom dari pola galat

Karena sindrom yang dilakukan pada vektor sandi terkena galat, maupun pada pola galat yang menyebabkannya, menghasilkan sindrom yang sama. Karena terdapat korespondensi satu-satu antara pola galat dan sindrom, maka ini merupakan petunjuk bahwa pola galat dapat dikoreksi. Berikut perhitungan untuk rangkaian deteksi dan gambar 3.9 menunjukkan diagram blok sindrom pada sandi blok (15,11) dan gambar 3.10 gambar rangkaian digital untuk deteksi. (Gambar rangkaian lihat gambar 9 L9). Sesusai dengan persamaan (2.13), diperoleh hasil sebagai berikut :

⎥⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎥ ⎦ ⎤ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎢ ⎣ ⎡ = 1 0 0 1 1 1 0 1 1 1 1 1 1 1 1 0 0 1 1 1 1 0 1 0 0 1 0 1 1 0 1 1 1 1 0 0 0 1 1 0 0 0 1 1 1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1 T H

Maka : S0 = r7 + r10 + r13

S1 = r1 + r7 + r10 + r11

S2 = r2 + r10 + r11 + r13

S3 = r3 + r7 + r11 + r13

Gambar 3.9 diagram blok sindrom pada sandi blok.

r r0 r1 r2 r3 r4 r5 r6 r7 r8 r9 r10 r11 r12 r13 r14

+ + + +

r2 r3 Q D CL KCL Q D CL KCL Q D CL KCL Q D CL KCL r4 Q D CL KCL r5 Q D CL KCL Q D CL KCL r6 data i r8 Q D CL KCL Q D CL KCL Q D CL KCL r7 Q D CL KCL Q D CL KCL SERIAL OUT r9 B r10 clea r11 C Q D CL KCL r12 A Q D CL KCL r13 Q D CL KCL r0 r14 Q D CL KCL Q D CL KCL D

r1 D Q

CL KCL Q D CL KCL clock

Gambar 3.10 Rangkaian digital deteksi

Rangkaian deteksi ini tersusun dari 15 buahregister yaitu r0, r1, r2, r3, r4, r5, r6,

r7, r8, r9, r10, r11, r12, r13, dan r14. Register tersebut dapat diimplementasikan dengan

menggunakan delay flip flop (D FF), dan penambah modulo 2 dapat diimplementasikan dengan menggunakan gerbang XOR.

Pada rangkaian deteksi ini digunakan beberapa komponen antara lain LED sebagai penampil output, sebuah IC 74LS86 yang berisi 4 buah gerbang XOR dengan 2 masukan.

Pada register ini data dimasukkan secara paralel dan data keluaran dikeluarkan secara seri. Data pada D0 akan dimasukkan langsung kedalam D-FF A,

tetapi data D1, D2, dan D3 menunggu keluaran dari D-FF sebelumnya. Seperti pada

data D1, data yang masuk akan di AND-kan terlebih dahulu dengan data load yang di

NOT-kan, kemudian data load yang tidak di NOT-kan akan di AND-kan dengan data keluaran D0, setelah melalui gerbang AND, data akan dimasukkan ke gerbang OR,

keluaran dari gerbang OR ini akan menjadi masukan pada D-FF B. Dan begitu seterusnya sampai dengan data yang diinginkan.

BAB IV

HASIL DAN PEMBAHASAN

Bab ini akan membahas hasil pengujian alat yang dibuat. Pengujian diperlukan untuk mengetahui apakah alat yang dibut sesuai dengan perancangan. Pengujian dianggap benar apabila data yang diterima sama dengan data yang dikirim.

4.1 Analisa Rangkaian Penyandi.

Pengujian dilakukan dengan memasukkan data seperti pada tabel 4.1. Hasil keluaran dari alat penyandi akan dibandingkan dengan keluaran dari penyandi secara teori pada BAB II.

Tabel 4.1 Hasil keluaran Penyandi. No. Pesan Keluaran penyandi pada

alat

Keluaran penyandi pada teori

Tabel 4.1 (Lanjutan) Hasil keluaran Penyandi

No. Pesan Keluaran penyandi pada alat

Keluaran penyandi pada teori

10 0 0 0 0 0 0 0 0 0 1 0 1 0 1 1 0 0 0 0 0 0 0 0 0 1 0 1 0 1 1 0 0 0 0 0 0 0 0 0 1 0 11 0 0 0 0 0 0 0 0 0 0 1 1 0 0 1 0 0 0 0 0 0 0 0 0 0 1 1 0 0 1 0 0 0 0 0 0 0 0 0 0 1 12 1 0 0 0 1 1 1 0 0 0 0 1 1 0 1 1 0 0 0 1 1 1 0 0 0 0 1 1 0 1 1 0 0 0 1 1 1 0 0 0 0 13 0 0 0 0 0 1 1 1 0 0 0 1 1 0 0 0 0 0 0 0 1 1 1 0 0 0 1 1 0 0 0 0 0 0 0 1 1 1 0 0 0 14 0 0 0 0 1 1 1 1 1 0 0 1 0 0 1 0 0 0 0 1 1 1 1 1 0 0 1 0 0 1 0 0 0 0 1 1 1 1 1 0 0 15 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

Dari hasil pengujian pada rangkaian penyandi, diketahui bahwa penyandi akan mengeluarkan data sebagai keluaran pada saat clock pertama sampai clock ke lima belas. Pada clock pertama sampai dengan clock ke sebelas, keluaran dari penyandi merupakan bit pesan, sedangkan pada clock ke dua belas sampai clock ke lima belas, keluaran penyandi merupakan bit paritas. Dari pengamatan diketahui bahwa keluaran dari rangkaian penyandi alat sama dengan teori.

4.2 Analisa Rangkaian Pembuat Galat.

Tabel 4.2 Pembuat galat untuk beberapa posisi galat pada sandi (1 0 0 1 0 0 0 0 0 0 0 0 0 0 1)

No. Posisi galat pada bit ke- Keluaran pembuat galat 1 Tanpa galat 1 0 0 1 0 0 0 0 0 0 0 0 0 0 1

2 1 0 0 0 1 0 0 0 0 0 0 0 0 0 0 1

3 2 1 1 0 1 0 0 0 0 0 0 0 0 0 0 1

4 3 1 0 1 1 0 0 0 0 0 0 0 0 0 0 1

5 4 1 0 0 0 0 0 0 0 0 0 0 0 0 0 1

6 5 1 0 0 1 1 0 0 0 0 0 0 0 0 0 1

7 6 1 0 0 0 0 1 0 0 0 0 0 0 0 0 1

8 7 1 0 0 1 0 0 1 0 0 0 0 0 0 0 1

9 8 1 0 0 1 0 0 0 1 0 0 0 0 0 0 1

10 9 1 0 0 1 0 0 0 0 1 0 0 0 0 0 1

11 10 1 0 0 1 0 0 0 0 0 1 0 0 0 0 1

12 11 1 0 0 1 0 0 0 0 0 0 1 0 0 0 1

13 12 1 0 0 1 0 0 0 0 0 0 0 1 0 0 1

14 13 1 0 0 1 0 0 0 0 0 0 0 0 1 0 1

15 14 1 0 0 1 0 0 0 0 0 0 0 0 0 1 1

16 15 1 0 0 1 0 0 0 0 0 0 0 0 0 0 0

17 1 dan 5 0 00 1 1 0 0 0 0 0 0 0 0 0 1 18 2 dan 8 1 1 0 1 0 0 0 1 0 0 0 0 0 0 1 19 2, 3 dan 4 1 1 1 0 0 0 0 0 0 0 0 0 0 0 1 20 3, 4, 5 dan 6 1 0 1 0 1 1 0 0 0 0 0 0 0 0 1 21 5, 6, 8 dan11 1 0 0 1 1 1 0 1 0 0 1 0 0 0 1 22 9, 10, 11 dan 13 1 0 0 1 0 0 0 0 1 1 1 0 1 0 1 23 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, dan15 0 1 1 0 1 1 1 1 11 1 1 1 10

Bit data yang terkena galat

4.3 Analisa Rangkaian Sindrom.

Data yang keluar dari rangkaian pembuat galat terdiri dari empat bit paritas dan 11 bit pesan. Data tersebut akan dikirimkan ke dalam rangkaian sindrom. Pada rangkaian sindrom ini, galat yang masuk dapat dideteksi. Jika sindrom tidak bernilai 0000 maka pada data tersebut terdapat galat dan jika sindrom bernilai 0000 maka data tersebut adalah data yang benar. Jika dalam data terdapat galat, maka LED pada rangkaian deteksi akan menyala, yang berarti bernilai 1. Jika tidak terdapat galat, maka LED pada rangkaian deteksi akan padam, yang berarti bernilai 0. Tabel 4.3 menunjukkan hasil deteksi dari data yang terkirim.

Tabel 4.3 Hasil deteksi data yang diterima dengan sandi (1 0 0 1 0 0 0 0 0 0 0 0 0 0 1).

Tabel 4.3 (Lanjutan) Hasil deteksi data yang diterima sandi (1 0 0 1 0 0 0 0 0 0 0 0 0 0 1 )

No. Data yang diterima LED Deteksi Keterangan 20 1 0 1 0 1 1 0 0 0 0 0 0 0 0 1 1 0 0 1 Terdapat error 21 1 0 0 1 1 1 0 1 0 0 1 0 0 0 1 1 0 0 1 Terdapat error 22 1 0 0 1 0 0 0 0 1 1 1 0 1 0 1 1 1 1 0 Terdapat error

23 0 1 1 0 1 1 1 1 11 1 1 1 10 0 0 0 0 Tidak terdapat error

Bit data yang terkena galat

Dari tabel 4.3 diketahui bahwa tidak semua data yang diberi galat akan terdeteksi

karena LED pada rangkaian deteksi tidak semuanya hidup, tetapi ada beberapa yang padam. Hal tersebut terjadi karena data yang diberi galat masih merupakan bagian dari polinomial kata sandi. Untuk mengetahui data yang diterima oleh rangkaian deteksi yang pasti mengalami galat, maka panjang bit periksa harus diketahui dengan menggunakan rumus dmin - 1.Untuk mengetahui bahwa sindrom yang dihasilkan tidak bernilai 0000, maka dilakukan pembagian antara data yang terkirim dengan polinomial pembangkit (g(X) = 1 + X + X4) berikut ini. Sebagai contoh apakah data pada percobaan 11 dari tabel 4.3 sudah sesuai dengan teori, maka dilakukan perhitungan sebagai berikut:

2 3 1 2 5 1 3 5 3 4 7 1 4 5 7 4 5 8 1 7 8 7 8 11 1 11 11 12 15 1 12 15 4 1 X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X + + + + + + + + + + + + + + + + + + + + + + +

BAB V

PENUTUP

5. 1. Kesimpulan

Kesimpulan yang didapat dari penelitian ini adalah:

1. Alat dapat mensimulasikan sandi blok (15,11) dengan baik karena sudah sesuai dengan teori.

2. Deteksi galat menggunakan sandi blok (15,11) dapat disimulasikan dengan rangkaian digital.

3. Rangkaian pembuat galat dapat digunakan untuk membuat galat tunggal,galat ganda dan galat yang lebih dari dua di semua posisi.

4. Rangkaian deteksi mampu mendeteksi galat baik galat tunggal, galat ganda maupun galat yang lebih dari dua, dan galat maksimal adalah lima belas.

5. 2. Saran

Adapun saran yang dapat penulis berikan berkaitan dengan deteksi galat menggunakan sandi blok (15,11) berbasis rangkaian digital adalah adalah:

DAFTAR PUSTAKA

Lin, S., and Costello, D. J., Jr., (1983). Error Control Coding : Fundamental’s and

Application’s, Prentice-Hall, Inc., Engelwood Cliffs, New Jersey.

Tokheim, M.S., Roger, L., (1996). Prinsip-Prinsip digital, Edisi Kedua, Erlangga, Jakarta.

Sklar, Bennard, (1988). Digital Communications : Fundamental’s and Applications,

Prentice-Hall, Inc., Engelwood Cliffs, New Jersey.

Floyd, Thomas, L., (1997). Digital Fundamental’s, 6thed, Prentice-Hall, Inc., Upper Saddle River, New Jersey.

Muhsin, Muhammad., (2004). Elektronika Digital : Teori dan Soal Penyelesaian,

Andi Offset, Yogyakarta.

Malvino, A. P., and Leach, D. P., (1992). Prinsip-prinsip dan Penerapan Digital,

Edisi Ketiga, Erlangga, Jakarta.

Damar, W., (2002). Sistem Pengolahan Sinyal : Diktat Kuliah.

GND

1

B

1

F

1

G

1

CLK

1

H

1

I

1

74164

1 2 3 4 5 6 7

14 13 12 11 10 9 8

J

1

E

1

A

1

C

1

CLEAR

1

VCC

1

K

1

74164

1 2 3 4 5 6 7

14 13 12 11 10 9 8

IN

1

D

1

74164 1 2 3 4 5 6 7 14 13 12 11 10 9 8 J 1 B 1 CLEAR 1 O 1 N 1 74164 1 2 3 4 5 6 7 14 13 12 11 10 9 8 IN 1 M 1 L 1 E 1 CLK 1 K 1 I 1 D 1 GND 1 H 1 G 1 VCC 1 A 1 F 1 C 1

E

1

7485

1 2 3 4 5 6 7 8

16 15 14 13 12 11 10 9

C

1

A 1

output

1

GND

1

F

1

D

1

B

1

VCC

1

7485

1 2 3 4 5 6 7 8

16 15 14 13 12 11 10 9

7493 1 2 3 4 5 6 7 14 13 12 11 10 9 8 LA LB vcc 1 LC clear 1 E LD 7432 1 2 3 4 5 6 7 14 13 12 11 10 9 8 B 7408 1 2 3 4 5 6 7 14 13 12 11 10 9 8 LE D 7493 1 2 3 4 5 6 7 14 13 12 11 10 9 8 LF A F clock 1 C gnd 1

7404

1 2 3 4 5 6 7

14 13 12 11 10 9 8

GND

1

KENDALI

1

VCC

1

7432

1 2 3 4 5 6 7

14 13 12 11 10 9 8

7408

1 2 3 4 5 6 7

14 13 12 11 10 9 8

OUTPUT REG

1

DATA

1

OUTPUT

1

10k

out 1

C1

100uF Vcc

1

555

1 2 3 4

5 6 7 8

10k

D1

LED

0,01uF 330

Gnd 1 saklar

1 2 3 1uF

B

data in D Q

CLK CL Q D CLK CL CLEAR A D U3 Q D CLK CL U0 Q D CLK CL U1 Q D CLK CL U2 U4 Q D CLK CL Q D CLK CL Q D CLK CL

U5 U6 U7

SERIAL OUT Q D CLK CL Q D CLK CL Q D CLK CL Q D CLK CL U8 Q D CLK CL Q D CLK CL CLOCK U9 C Q D CLK CL U10

D7 74l s74 1 2 3 4 5 6 7 14 13 12 11 10 9 8 R8 saklar7 1 2 3 D4 74l s74 1 2 3 4 5 6 7 14 13 12 11 10 9 8 D5 R4 vcc 1 D5 74l s74 1 2 3 4 5 6 7 14 13 12 11 10 9 8 saklar13 1 2 3 saklar2 1 2 3 saklar9 1 2 3 D3 D2 data in 1 saklar10 1 2 3 saklar3 1 2 3 74l s74 1 2 3 4 5 6 7 14 13 12 11 10 9 8 D1 saklar11 1 2 3 saklar4 1 2 3 R6 R2 GND 1 J30 Output 1 saklar14 1 2 3 D1 R7 R1 R4 74l s74 1 2 3 4 5 6 7 14 13 12 11 10 9 8 R7 D6 74l s74 1 2 3 4 5 6 7 14 13 12 11 10 9 8 74l s74 1 2 3 4 5 6 7 14 13 12 11 10 9 8 saklar1 1 2 3 R3 D3 saklar8 1 2 3 R1 R2 74l s74 1 2 3 4 5 6 7 14 13 12 11 10 9 8 D8 R6 saklar6 1 2 3 saklar15 1 2 3 D4 D7 R3 CLK 1 saklar12 1 2 3 clear 1 D2 R5 D6 saklar5 1 2 3 R5

r2 r3 D Q CL KCL Q D CL KCL Q D CL KCL Q D CL KCL

r4 D Q

CL KCL r5 Q D CL KCL Q D CL KCL r6 data i r8 Q D CL KCL Q D CL KCL Q D CL KCL r7 Q D CL KCL Q D CL KCL SERIAL OUT r9 B r10 clea r11 C Q D CL KCL r12 A Q D CL KCL r13 Q D CL KCL r0 r14 Q D CL KCL Q D CL KCL D

r1 D Q

CL KCL Q D CL KCL clock