CPU

( Central Processing Unit )

PERKEM BANGAN ARSITEKTUR CPU

CPU t erdiri dari beberapa bagian yang berbeda yang saling berint egrasi dalam m em bent uk fungsinya secara bersam aan. Pada bagian ini akan dibahas perkem bangan arsit ekt ur CPU dari t iga generasi yait u generasi pra kom put er yang akan diw akili oleh arsit ekt ur m esin Analit is Babagge, generasi kom put er pert am a yang st ored program yang diw akili oleh m esin Von Noum ann dan generasi kom put er m odern.

Arsitektur M esin Analitis Babbage (1843)

Pada t ahun 1843, seorang professor m at em at ika dari Universit as Cam bridge Inggris yang bernam a Charles Babbage, m enem ukan suat u konsep pem rosesan dat a yang m enjadi dasar kerja dan prot ot ipe dari komput er-kom put er jam an sekarang. M esin t ersebut dikenal dengan nam a Babbage’s Analyt ical Engine.

Gambar 3.1. Babbage’s Analytical Engine

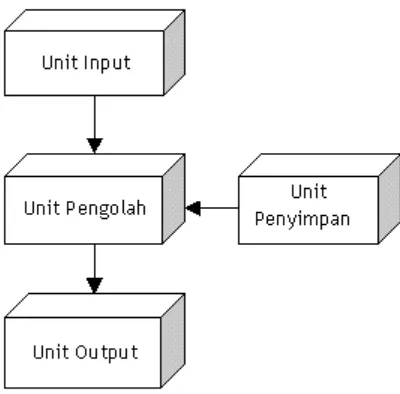

Gambar 3.2. Arsitektur Babbage’s Analytical Engine

M esin Babbage m emiliki em pat blok ut am a dalam m enjalankan fungsinya (lihat gam bar 3.2).

Bagian input, digunakan untuk membaca instruksi-instruksi dan data dari kartu berlubang.

Bagian penyimpanan, memuat 1000 Word yang masing-masing terdiri dari 50 digit desimal. Bagian tersebut digunakan untuk menyimpan operand-operand matematika dari suatu perhitungan.

Bagian pengolah, digunakan untuk melakukan pemrosesan data berdasarkan instruksi yang diberikan oleh kartu-kartu plong.

Bagian output, terdiri dari output tercatat dan output tercetak yang digunakan untuk menyimpan serta menampilkan hasil pengolahan.Salah sat u kelem ahan m esin ini yang bukan m erupakan konsep kom put er m odern adalah bahw a m esin ini belum st ored program at au t idak m am pu m enyim pan program secara t et ap.

Arsitektur M esin Von Neumann (1952)

M esin Von Neum ann dalam hal ini m ew akili m esin kom put er generasi pert am a yang bersifat st ored program . John Von Neum ann adalah seorang ahli m at em at ika dan anggot a Inst it ut e of Advance St udy di Princent ion New Jersey yang bekerja sam a dengan H.H. Goldstine dan A.W. Binks m engajukan suat u m akalah yang m enyarankan bahw a dalam pem buat an kom put er sebaiknya m enggunakan angka binary. Konsep t ersebut pada akhirnya m enjadi t onggak sejarah dalam t ercipt anya kom put er digit al yang akhirnya m em baw a Neum ann pada julukan “promot er of t he st ored program (soft ware) concept ”.

Rancangan dasar m esin yang diberi nam a IAS ini adalah konsep Neum ann yang m enyat akan bahw a pem rogram an kom put er secara langsung dengan m enggunakan banyak t om bol dan kabel adalah sesuat u yang m elelahkan, lam bat dan t idak fleksibel.

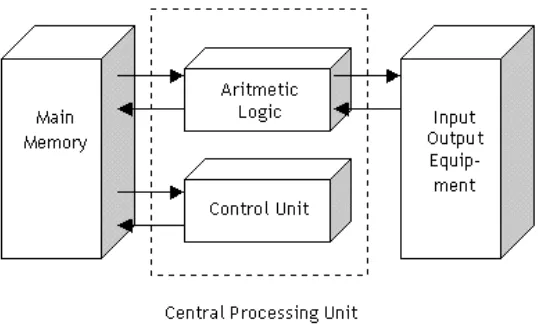

Unt uk it u dia berpikiran bahw a sebuah program dapat diw akili dalam bent uk digit al dan t ersim pan secara t et ap dalam m em ori kom put er secara bersam a-sama. Sket sa arsit ekt ur dari rancangan t ersebut adalah sepert i pada gam bar 3.4 di baw ah ini.

Gambar 3.4. Sketsa arsitektur dari rancangan Neumann

Dari gam bar di at as, dapat diket ahui bahw a m esin Neum ann m em iliki lim a bagian ut am a sebagai berikut :

Unit Input untuk membaca data dan instruksi yang diberikan.

M ain M emory terdiri dari 4096 Word satu word memuat 40 bit biner.

Arithmetic Logic sebagai bagian yang berfungsi sebagai unit pemrosesan.

Control Unit sebagai pengendali kerja antar komponen arsitektur.

Unit Output untuk menampilkan hasil pengolahan data yang dilakukan ALU dan CU. Dari arsit ekt ur m esin t ersebut t erlihat bahw a m esin ini sudah m em iliki bagian-bagian yang m enjadi prot ot ipe kom put er m odern yait u Arit hmet ic Logic dan Cont rol Unit yang m erupakan bagian dari Cent ral Processing Unit.Arsitektur Mesin Komputer Modern (1980 …)

Arsit ekt ur CPU kom put er m odern, secara um um dapat dilihat sepert i pada gam bar berikut :

Pada gam bar 3.5 di at as, dapat dilihat bagian-bagian CPU yang lebih lengkap sepert i Regist er, Cont rol Unit , Kendali I/ O (Int erconect ion) dan Arit hmetic Logic Unit.

BAGIAN-BAGIAN CPU

Arithmetic and Logic Unit (ALU), bert ugas membent uk fungsi - fungsipengolahan dat a komput er

Control Unit, bert ugas mengont rol operasi CPU dan secara keseluruhanmengont rol komput er sehingga t erjadi sinkronisasi kerja ant ar komponen dalam menjalankan fungsi - fungsi operasinya

Registers, adalah media penyim pan int ernal CPU yang digunakan saat prosespengolahan dat a

CPU Interconnections, adalah sist em koneksi dan bus yang menghubungkankomponen int ernal CPU, yait u ALU, unit kont rol dan regist er - regist er dan juga dengan bus - bus ekst ernal CPU yang menghubungkan dengan sist em lainnya

FUNGSI CPU

Fungsi CPU adalah penjalankan program - program yang disimpan dalam memoriut ama dengan cara mengambil inst ruksi - inst ruksi, menguji inst ruksi t ersebut dan mengeksekusinya sat u persat u sesuai alur perint ah

Proses Eksekusi Program adalah dengan mengambil pengolahan inst ruksi yangt erdiri dari dua langkah, yait u operasi pembacaan inst ruksi (fet ch) dan operasi pelaksanaan inst ruksi (execut e).

Siklus Fetch Eksekusi Program :1. CPU aw alnya akan membaca inst ruksi dari memori.

2. Terdapat regist er dalam CPU yang berfungsi mengaw asi dan menghit ung inst ruksi selanjut nya, yang disebut Program Count er (PC).

AKSI-AKSI DI DALAM CPU.

CPU - M emori, perpindahan dat a dari CPU ke memori dan sebaliknya

CPU - I/ 0, perpindahan dat a dari CPU ke modul I/ 0 dan sebaliknya

Pengolahan Data, CPU membent uk sejumlah operasi arit mat ika dan logikat erhadap dat a

Kontrol, merupakan inst ruksi unt uk pengont rolan fungsi at au kerja. M isalnyainst ruksi pengubahan urut an eksekusi

SIKLUS INSTRUKSI DALAM CPU.

Instruction Addess Calculation (IAC), yait u mengkalkulasi at au menent ukanalamat inst ruksi berikut nya yang akan dieksekusi. Biasanya melibat kan penambahan bilangan t et ap ke alamat inst ruksi sebelumnya

Instruction Fetch (IF), yait u membaca at au pengambil inst ruksi dari lokasimemorinya ke CPU

Instruction Operation Decoding (IOD), yait u menganalisa inst ruksi unt ukmenent ukan jenis operasi yang akan dibent uk dan operand yang akan digunakan

Operand Address Calculation (OAC), yait u menent ukan alamat operand, hal inidilakukan apabila melibat kan referensi operand pada memori

Operand Fetch (OF),adalah mengambil operand dari memori at au dari modul i/ o

Data Operation (DO), yait u membent uk operasi yang diperint ahkan dalaminst ruksi

Operand store (OS),yait u menyimpan hasil eksekusi ke dalam memoriTENTANG INTERUPT.

Fungsi int erupsi adalah mekanisme penghent ian at au pengalihan pengolahan inst ruksi dalam CPU kepada rout ine int erupsi. Hampir semua modul (memori dan I/ 0) mem iliki mekanisme yang dapat mengint erupsi kerja CPU.

Tujuan int erupsi secara umum unt uk manajemen pengeksekusian rout ineinst ruksi agar efekt if dan efisien ant ar CPU dan modul - m odul I/ 0 maupun memori.

Set iap komponen komput er dapat menjalankan t ugasnya secara bersamaan, t et api kendali t erlet ak pada CPU disamping it u kecepat an eksekusi masing - masing modul berbeda sehingga dengan adanya fungsi int erupsi ini dapat sebagai sinkronisasi kerja ant ar modul.SINYAL INTERUPSI DALAM CPU.

Program, yait u int erupsi yang dibangkit kan dengan beberapa kondisi yang t erjadipada hasil eksekusi program. Cont ohnya: arimat ika overflow , pembagian nol, oparasi ilegal

Timer, adalah int erupsi yang dibangkit kan pew akt uan dalam prosesor. Sinyal ini

I/ 0, sinyal int erupsi yang dibangkit kan oleh modul I/ 0 sehubungan pemberit ahuan kondisi error dan penyelesaian suat u operasi

Hardw are failure, adalah int erupsi yang dibangkit kan oleh kegagalan daya at aukesalahan parit as memori

INTERUPSI GANDA.

M enolak at au t idak mengizinkan int erupsi lain saat suat u int erupsi dit angani prosesor. Kemudian set elah prosesor selesai menangani suat u int erupsi maka int erupsi lain baru di t angani. Pendekat an ini disebut pengolahan interupsi berurut an / sekuensial

Priorit as bagi int erupsi dan int errupt handler mengizinkan int erupsi berpriorit as lebih t inggi dit angani t erlebih dahulu. Pedekat an ini disebut pengolahan int erupsi bersarangINTERUPSI BERSARANG.

Sist em memiliki t iga perangkat I/ 0: print er, disk, dan saluran komunikasi

Pada aw al sist em melakukan pencet akan dengan print er, saat it u t erdapat pengiriman dat a pada saluran komunikasi sehingga modul komunikasi memint a int erupsi

Proses selanjut nya adalah pengalihan eksekusi int erupsi modul komunikasi, sedangkan int erupsi print er dit angguhkan

Saat pengeksekusian modul komunikasi t erjadi int erupsi disk, namun karena priorit asnya lebih rendah maka int erupsi disk dit angguhkan

Set elah int erupsi modul komunikasi selesai akan dilanjut kan int erupsi yang memiliki priorit as lebih t inggi, yait u disk

Bila int erupsi disk selesai dilanjut kan eksekusi int erupsi print er

Selanjut nya dilanjut kan eksekusi program ut amaPerkembangan Desain Prosessor

Tanem baun (2001) m engem ukakan adanya prinsip-prinsip pent ing dalam m elakukan desain prosessor kom put er m odern. Dikenal dengan prinsip RISC (Reduced Inst ruct ion Set Comput er), yang ant ara lain sebagai berikut :

1. Prinsip 1 : M emaksimalkan kecepatan di mana instruksi-instruksi dikeluarkan.

Prinsip ini m enekankan pengem bangan jum lah inst ruksi yang dapat diproses per det ik pada sebuah prosesor. Dari konsep ini akhirnya lahir ist ilah M IPS (M ilion of Inst ruct ion Per Second) yang nant inya akan m enunjukan bahw a paralelism e prosesor akan dapat m eningkat kan kinerja sebuah kom put er.

2. Prinsip 2 : M emperbanyak instruksi yang secara langsung dapat dijalankan hardw are untuk mempercepat kinerja.

Unt uk m eningkat kan kecepat an proses eksekusi sebuah perint ah, m aka salah sat u cara yang dapat dit em puh adalah dengan m em perbanyak jum lah inst ruksi yang dapat secara langsung dijalankan oleh hardw are kom put er.

3. Prinsip 3 : Instruksi-instruksi harus mudah untuk di kodekan.

Bat as krit is pada t ingkat kecepat an adalah dekode dari set iap inst ruksi. Sem akin sedikit form at inst ruksi m aka akan sem akin baik kinerja dan kecepat an sebuah eksekusi inst ruksi. 4. Prinsip 4 : Hanya instruksi LOAD dan STORE yang diakses ke memory.

Prinsip ini m em berikan pandangan kepada para penelit i dan pengem bang kom put er unt uk berusaha m em perkecil inst ruksi yang langsung diakses dari m emory ut am a.