Implementasi FFT (Fast Fourier Transform) 16-Titik pada

FPGA ALTERA Keluarga FLEX-10K menggunakan VHDL

Agfianto Eko Putra

1), Eka Budi Santosa

2)1,2)Jurusan Ilmu Komputer dan Elektronika, Fak. MIPA – UGM, Yogyakarta

email: 1)agfi@ugm.ac.id, 2)ekabudi@yahoo.co.id

Abstrak– Telah dilakukan implementasi FFT 16-titik berbasis FPGA Altera keluarga FLEX-10K menggunakan deskripsi VHDL . Implementasi FFT ini didasarkan pada algoritma Radix-2 Decimation-In-Frequency. Implementasi dilakukan pada 2 (dua) macam FPGA Altera Keluarga FLEX-10K, yaitu EPF10K20TC144-3 (FLEX-10K) dan EPF10K30ETC144-1 (FLEX-10KE). Analisis pewaktuan, untuk FPGA tipe EPF10K20TC144-3, menunjukkan bahwa sistem mampu diberikan detak (clock) hingga 26,73 MHz dan melakukan proses FFT 16-titik dalam waktu 16,75 mikrodetik. Sedangkan tipe EPF10K30ETC144-1, maksimum frekuensi detak-nya adalah 60,97MHz dan melakukan proses yang sama dalam waktu 7,35 mikrodetik.

Kata kunci: FPGA, FFT, VHDL

1. PENDAHULUAN

Transformasi Fourier Diskrit atau Discrete Fourier Transform (DFT) merupakan salah satu bagian penting dalam Pemrosesan Sinyal Digital (PSD). Proses komputasi DFT memerlukan sejumlah besar operasi aritmatika yang memiliki masalah dalam kecepatan proses komputasinya dan berpengaruh pada proses waktu-nyata (real-time). Untuk melakukan proses komputasi DFT yang lebih cepat, diperlukan suatu algoritma yang dapat mengurangi banyaknya jumlah operasi aritmatika. Salah satu algoritma yang efisien untuk melakukan DFT adalah Fast Fourier Transform (FFT). Selain efisien, faktor lain yang mempengaruhi kecepatan pemrosesan adalah prosentase penggunaan perangkat lunak dan perangkat keras. Implementasi sistem menggunakan perangkat keras cenderung lebih cepat dibandingkan perangkat lunak.

Field Programable Gate Array atau FPGA adalah sebuah emping (chip) yang dapat digunakan untuk mengimplementasikan suatu rancangan sistem digital. Sistem digital diimplementasikan ke dalam FPGA sehingga akan terbentuk sebuah emping ASIC (Application Specific Integrated Circuit) yang memiliki kecepatan proses lebih cepat dibandingkan implementasi perangkat lunak [1]. Dalam penelitian

ini dirancang dan dimplementasikan sebuah prosessor FFT 16-titik menggunakan FPGA Altera Keluarga FLEX-10K.

Fast Fourier Transform (FFT) merupakan algoritma yang digunakan untuk melakukan proses DFT secara efisien. Algoritma FFT sendiri ada beberapa jenis, sedangkan yang digunakan dalam penelitian ini adalah algoritma FFT Cooley-Tukey Radix-2. Algoritma ini memiliki dua macam bentuk yaitu Decimation-in-Time (DIT) dan Decimation-in-Frequency (DIF) [2]. Kedua algoritma tersebut mempunyai tingkat kompleksitas yang sama akan tetapi berbeda dalam urutan komputasinya. Implementasi FFT dalam penelitian ini menggunakan algoritma FFT radix-2

Decimation-in-Frequency.

Algoritma decimation-in-frequency menguraikan DFT N-titik menjadi DFT yang lebih kecil dan secara berurutan melalui persamaan

𝑋 𝑘 = 𝑁−1𝑥 𝑛 𝑊𝑁𝑘𝑛

𝑛=0 (1)

Untuk 0 ≤ k ≤ N-1 dengan 𝑊𝑁=𝑒−𝑗2𝜋/𝑁

Melalui persamaan (1), untuk mendapatkan hasil FFT, yaitu 𝑋(𝑘), melibatkan 𝑥(𝑛) sebagai data-data diskrit dalam ranah waktu, 𝑁 sebagai jumlah data dan 𝑛 merupakan indeks data yang bersangkutan.

FFT 16-titik dapat dikerjakan menggunakan algoritma

Decimation-in-Frequency sesuai dengan diagram alir sinyal yang ditunjukkan pada Gambar 1. Dasar dari komputasi algoritma ini adalah proses butterfly FFT radix-2 yang ditunjukkan pada Gambar 2, proses

butterfly itu sendiri terdiri dari operasi penjumlahan, pengurangan, dan perkalian [3].

P

Gambar 1. Diagram Alir sinyal FFT 16-titik radix-2 DIF

Gambar 2. Diagram butterfly FFT radix-2 DIF

2. PERANCANGAN

2.1.RANCANGAN PROSESOR FFT 16-TITIK SECARA UMUM

Rancangan prosessor FFT 16-titik dapat dibagi menjadi tiga macam proses utama yaitu pemasukan data, komputasi FFT dan proses pengeluaran data hasil FFT. Siklus pemrosesan dimulai dengan memasukkan data yang kemudian disimpan ke dalam RAM. Setelah data satu periode sinyal tersimpan dalam RAM, dilanjutkan dengan proses komputasi

FFT, melalui proses butterfly dan hasilnya disimpan lagi di RAM pada alamat yang sama. Data hasil komputasi FFT didalam RAM dihasilkan melalui port luaran.

Dalam komputasi FFT 16-titik digunakan algoritma FFT radix-2, artinya prose FFT 16-titik diuraikan menjadi menjadi beberapa FFT 2-titik. Komputasi FFT 2-titik merupakan satu operasi butterfly yang terdiri dari penjumlahan dan pengurangan antara dua variabel komplek kemudian perkalian antara hasil pengurangan dengan twiddle-factor (Wn kN ) yang ditunjukkan oleh diagram alir sinyal pada Gambar 2. Untuk FFT 16-titik akan terbentuk 32 operasi butterfly

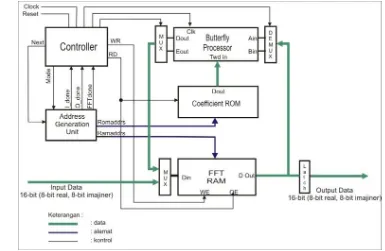

yang terbagi dalam 4 tahap (stage) sehingga tiap tahap terdiri dari 8 operasi butterfly. Diagram alir sinyal dari FFT 16-titik ditunjukkan oleh Gambar 1. Gambaran umum perancangan sistem ditunjukkan dalam diagram blok pada Gambar 3. Dari diagram blok tersebut dapat kita ketahui blok atau modul rancangan apa saja yang digunakan.

Modul pengontrol (controller) menghasilkan sinyal-sinyal kontrol yang digunakan untuk mengendalikan seluruh modul. Address Generation Unit (AGU) berfungsi sebagai penghasil alamat yang digunakan untuk mengalamati RAM dan ROM selama proses pemasukan, pengeluaran dan komputasi FFT. Cara pengalamatan RAM dan ROM berbeda-beda untuk setiap proses. Pengalamatan ROM hanya dilakukan pada saat proses komputasi FFT.

RAM dan ROM merupakan tempat penyimpanan data yang digunakan selama proses komputasi. RAM

dugunakan untuk menyimpan data masukan yang akan diproses dan menyimpan data pada hasil proses komputasi FFT yang sedang berlangsung. RAM yang digunakan dalam sistem ini ada dua yaitu RAM1 dan RAM2. RAM1 digunakan untuk menyimpan data koefisien bagian real, sedangkan RAM2 untuk menyimpan koefisien bagian imajiner. ROM (Read Only Memory) digunakan untuk menyimpan konstanta

perkalian, Twiddle-Factor (Wn kN ). Konstanta yang

diperlukan dalam perhitungan ada tiga macam sehingga membutuhkan tiga ROM.

2.2.MODUL BUTTERFLY

Modul ini merupakan komponen utama dalam proses komputasi Fast Fourier Transform (FFT). Modul prosessor butterfly mengerjakan komputasi FFT 2-titik. Operasi aritmatik yang dikerjakan prosessor

butterfly melalui persamaan

𝐷𝑅𝑒+𝑗𝐷𝐼𝑚 = 𝐴𝑅𝑒+𝑗𝐴𝐼𝑚 + 𝐵𝑅𝑒+𝑗𝐵𝐼𝑚 (2)

𝐸𝑅𝑒+𝑗𝐸𝐼𝑚 =

𝐴𝑅𝑒+𝑗𝐴𝐼𝑚 − 𝐵𝑅𝑒+𝑗𝐵𝐼𝑚 ∙ 𝐶+𝑗𝑆 (3)

𝐴 dan 𝐵 merupakan variabel kompleks masukan ke prosessor butterfly, sedangkan 𝐷 dan 𝐸 merupakan luaran hasil komputasi prosessor butterfly yang masing masing terdiri dari koefisien real dan imajiner. Dalam persamaan (3), twiddle-factor (𝑊𝑁𝑘𝑛) diubah ke dalam bentuk 𝐶+𝑗𝑆 .

Nilai semua peubah dalam proses komputasi menggunakan format 8-bit 2’s complement, yang dapat menyajikan nilai antara -128 sampai 127. Koefisien 𝐶 dan 𝑆 pada pengali twiddle-factor

mempunyai nilai antara 0 hingga 1, tetapi dalam proses komputasi nilai tersebut dikonversi kedalam format 8-bit 2’s complement karena format 2’s complement, dengan cara ini maka jika untuk nilai, misalnya, 𝑊𝑁𝑘𝑛 =𝑒𝑗𝜋/9 maka dalam bilangan 8-bit 2’s complement menjadi 𝐶+𝑗𝑆 = 256∙ 𝑒𝑗𝜋/9= 121 +

𝑗39.

Perkalian dengan twiddle-factor merupakan perkalian antara dua bilangan komplek yaitu antara hasil operasi

)

Untuk proses komputasi algoritma tersebut digunakan algoritma yang telah dimodifikasi sebagai berikut

C

Pada saat perancangan, nilai C dan S dihitung terlebih dahulu dan disimpan dalam tabel didalam ROM. Nilai-nilai yang harus dihitung terlebih dahulu untuk disimpan didalam ROM adalah

C

,C

S

, danS

C

. Nilai-nilai tersebut disimpan dalam ROM terpisah sehingga memerlukan tiga komponen ROM.Perancangan modul prosessor butterfly dilakukan dalam dua tahap yaitu perancangan komponen pengali

twiddle factor “ccmul” yang mengerjakan operasi

)

(

R

j

I

=(

X

j

Y

)

(

C

j

S

)

dan modul prosessor butterfly sendiri dimana didalamnya terdapat komponen “ccmul”. Modul prosessor butterfly juga terdiri dari penjumlah (adder) dan pengurang (subtractor) yang mengerjakan operasi 𝐴𝑟𝑒+𝑗 ∙𝐴𝑖𝑚+𝐵𝑟𝑒+𝑗∙𝐵𝑖𝑚 dan 𝐴𝑟𝑒+𝑗∙𝐴𝑖𝑚−𝐵𝑟𝑒+𝑗∙𝐵𝑖𝑚.

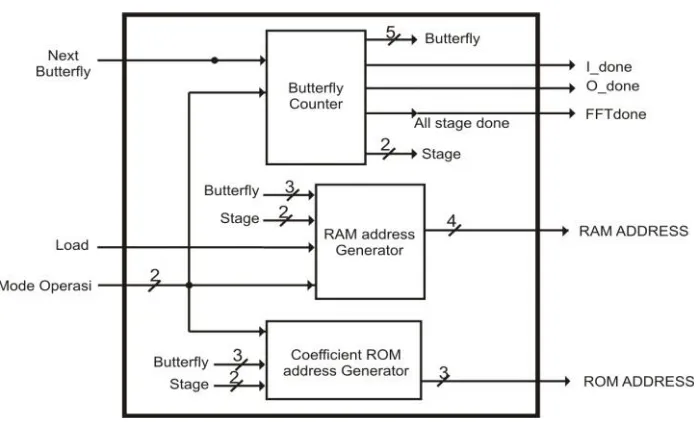

2.3.Modul Pengontrol

Modul ini merupakan komponen yang menghasilkan sinyal-sinyal kontrol untuk seluruh blok komponen yang ada. Fungsi dari sinyal-sinyal luaran modul ini ditunjukkan pada Tabel 1.

Tabel 1. Fungsi sinyal keluaran pengontrol

Sinyal Fungsi

WRITE Penulisan data ke RAM

READ Pembacaan data dari RAM/ROM

LOAD Indeks data A atau B. LOAD=0 untuk

alamat A, LOAD=1 untuk B

PROSES Sinyal detak untuk Butterfly Prosessor

SEL Memilih data (Ain atau Bin) dan (Dout

atau Eout)

MUAT Pembuka kunci Demultiplekser

UNMUAT Pembuka kunci Multiplekser 1 dan 2

MODE

Indikator proses. 00=proses pemasukan, 01= proses FFT, 10= proses

Pengeluaran

NextButter Sinyal detak untuk Adress Generator

Address Generator

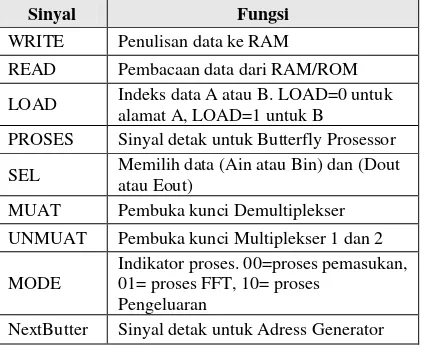

Modul Address Generator digunakan untuk menghasilkan alamat RAM dan ROM. Modul ini juga ikut menentukan operasi butterfly mana yang akan diproses dan pada stage berapa. Selain itu, modul ini juga akan memberikan sinyal kepada modul pengontrol jika terjadi suatu proses pemasukan data, komputasi FFT, maupun pengeluaran data telah selesai. Diagram blok dari modul ini ditunjukkan pada Gambar 5.

Butterfly Counter adalah pencacah 5-bit dimana untuk 16-titik FFT terdiri dari 8 proses butterfly tiap stage -nya. Blok ini akan menghasilkan empat sinyal yaitu I_done, O_done, FFTdon dan stage. Nilai dari sinyal stage akan naik jika nilai pencacah butterfly bernilai 8 yang menandakan perpindahan ke stage berikutnya. Perilaku Address Generator dalam menyediakan

alamat untuk tiap-tiap proses berbeda-beda. Sinyal MODE yang berasal dari pengontrol akan memberikan informasi mode proses yang sedang berlangsung dan akan mempengaruhi penyediaan alamat oleh modul ini. Alamat untuk ROM hanya diperlukan pada saat proses komputasi FFT.

2.4.Modul RAM

Modul RAM digunakan untuk menyimpan 16 data masukan dan tempat penyimpanan data pada proses komputasi FFT. Sistem ini menggunakan dua modul RAM, untuk memisahkan penyimpanan data real dengan data imajiner. Pembacaan RAM dikontrol oleh sinyal READ dari controller yang masuk ke port

outclock sedangkan untuk penulisan dikontrol oleh sinyal WRITE yang masuk ke port we.

Gambar 4. Diagram mesin keadaan komponen pengontrol

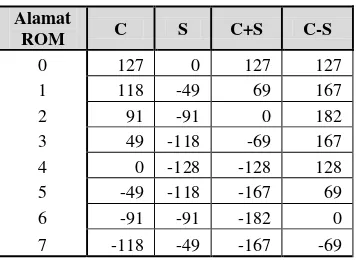

2.5.Modul ROM

Modul ROM digunakan untuk menyimpan data-data koefisien yang dibutuhkan pada saat perkalian dengan

twiddle-factor (Wn kN ) di Prosessor Butterfly. Data-data tersebut antara lain C, (C+S), dan (C-S). Data-data tersebut dihitung terlebih dahulu pada saat perancangan, hasilnya ditunjukkan pada Tabel 2. Jumlah ROM yang dibutuhkan ada tiga yaitu ROM1 dengan ukuran 8x8-bit, ROM2 dengan ukuran 8x9-bit, dan ROM3 8x9-bit.

Tabel 2. Data koefisien ROM C, (C+S), dan (C-S)

Alamat

ROM C S C+S C-S

0 127 0 127 127

1 118 -49 69 167

2 91 -91 0 182

3 49 -118 -69 167

4 0 -128 -128 128

5 -49 -118 -167 69

6 -91 -91 -182 0

7 -118 -49 -167 -69

2.6.Multiplekser, Demultiplekser dan Latch Multiplekser digunakan untuk memilih masukan data yang akan diteruskan ke satu jalur luaran. Multiplekser yang digunakan ada dua macam yaitu multiplekser sinkron dan multiplekser asinkron. Demultiplekser merupakan kebalikan dari multiplekser yaitu digunakan untuk memilih jalur data luaran. Latch digunakan untuk menahan data agar data dari pembacaan RAM tidak keluar pada port keluaran sistem sebelum masuk proses pengeluaran data. Letak penggunaan dari komponen ini dapat dilihat pada blok diagram sistem.

2.7.Penggabungan Modul

Semua modul yang telah dibuat dalam perancangan digabungkan sehingga menghasilkan sistem yang lengkap. Penggabungan modul-modul dilakukan dengan membuat entitas baru dalam VHDL dengan nama fftprosessor. Dalam entitas penggabungan ini, modul-modul yang telah dibuat dideklarasikan sebagai komponen sehingga tinggal disusun secara structural menggunakan VHDL. Tiap modul digabungkan sesuai dengan rancangan umum sistem yang telah diuraikan

sebelumnya.

2.8.Rangkaian Simulasi

Untuk menguji sistem yang telah digabungkan diperlukan komponen pengirim data ke port masukan Prosessor FFT secara streaming. Untuk itu dibuat rangkaian yang terdiri dari komponen pengirim data dan Prosessor FFT, sebagaimana ditunjukkan pada Gambar 6. Pada rangkaian simulasi, data yang akan diproses disimpan dalam ROM, kemudian dikirim ke prosesor FFT. Selain itu juga diperlukan pembagi frekuensi yang digunakan untuk mengatur detak untuk pengalamatan ROM. Untuk mengalamati ROM digunakan pencacah 4-bit karena data akan dibaca secara urut. Frekuensi detak untuk pencacah pengalamatan ROM adalah setengah dari detak untuk prosesor.

3. HASIL DAN PEMBAHASAN

3.1.Pengujian Komputasi FFT dengan Simulator Pengujian komputasi FFT dilakukan dengan melalui simulasi fungsional (functional simulation) menggunakan rangkaian simulator. Data yang akan dihitung adalah cuplikan 16-titik dari sinyal periodik sebagai berikut :

xn = [0, 1, 2, 3, 4, 5, 6, 0, 1, 2, 3, 4, 5, 6, 7, 8]

data tersebut diubah dalam format biner two’s

complement 8-bit kemudian disimpan ke dalam ROM. Data hasil komputasi FFT adalah sebagai berikut:

out_real = Xk real =

[57, 3, -14,1, -8, -3, -3, -8, -1, -7, -2, -3, -8, 2, -13, 5]

out_imag = Xk imag =

[0, 4, 13, 7, 1, 7, -2, 2, 0, -2, 2, -7, -1, 7, -14, -6]

Untuk mengetahui dan membuktikan kebenaran data hasil pemrosesan dengan sistem Prosessor FFT dilakukan pembandingan hasil perhitungan dengan fungsi “dfs” pada Matlab. Untuk membandingkan dalam bentuk grafik, data hasil pemrosessan Prosessor FFT diplot ke grafik menggunakan matlab. Hasilnya kemudian dibandingkan dengan grafik dari hasil pemrosesan dengan fungsi matlab. Grafik hasil pemrosessan dengan Prosessor FFT dan hasil fungsi „dfs‟ matlab ditunjukkan pada Gambar 7. Hasil tersebut menunjukkan bahwa bentuk keduanya hampir sama.

3.2.Analisis Pewaktuan

Analisis pewaktuan dilakukan menggunakan Timing Analyzer pada perangkat lunak Max+plus II. Ada beberapa pilihan yang dapat di analisis yaitu analisis

Delay matrix, Setup/hold matrix, dan Registered performance. Hasil analisis dengan Timing Analyzer, sebagaimana ditunjukkan pada Tabel 3, untuk 16-titik FFT adalah 448 detak. Jadi waktu minimum yang dibutuhkan untuk pemrosesan 16-titik FFT adalah 448 dikalikan periode detak yaitu 38,84 s.

Tabel 3. Hasil Timing Analyzer

Modul

Demultiplekser 8,0 125,00 11,0

Latch - - 13,7

Prosessor FFT 86,7 11,53 27,5

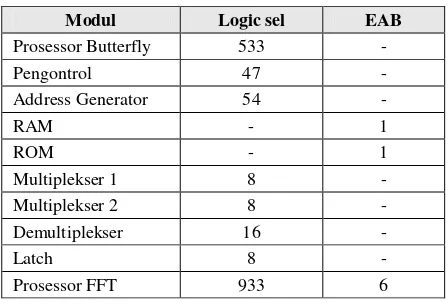

3.3.Analisis Sumber Daya

Dari proses kompilasi tersebut diperoleh hasil bahwa kode untuk sistem Prosessor FFT membutuhkan 933 Logic Element dan 6 EAB. Compiler memilih device

EPF10K20TC144-3. Hasil penggunaan sumber daya

untuk masing-masing modul ditunjukkan pada Tabel 4.

Tabel 4.Penggunaan Logic Element dan EAB

Modul Logic sel EAB

Prosessor Butterfly 533 -

Pengontrol 47 -

3.4.Optimasi Kecepatan dan Sumber Daya

Optimasi sistem Prosessor FFT yang pertama dilakukan pada piranti EPF10K20TC144-3 keluarga FLEX-10K. Menu optimize di set pada nilai 8. Hasil yang diperoleh ditunjukkan oleh Tabel 5.

Tabel 5. Optimasi Prosessor FFT pada piranti keluarga FLEX-10K

Piranti 10K Resource

(LC)

Optimasi yang kedua dilakukan pada piranti EPF10K30ETC144-1 keluarga FLEX-10KE. Hasil optimal diperoleh dengan mengatur menu optimize

pada nilai 7. Hasil yang diperoleh ditunjukkan oleh Tabel 6.

Tabel 6. Optimasi Prosessor FFT pada piranti keluarga FLEX-10KE

Dari hasil analisis Timing Analyzer Max+Plus II, diperoleh bahwa rancangan sistem Prosessor FFT pada piranti EPF10K20TC144-3 dapat memproses komputasi 16-titik FFT dalam waktu 16,75 d dengan menggunakan frekuensi detak maksimum sebesar 26,73 Mhz. Sedangkan pada piranti EPF10K30ETC144-1, dapat memproses komputasi 16-titik FFT dalam waktu 7,35 d dengan menggunakan frekuensi detak maksimum 60,97 Mhz.

DAFTAR REFERENSI

[1] Altera, 1997, MAX+PLUS II Getting Started (version 8.1). San Jose: Altera Corporation. [2] Meyer-Baese, U., 2007. Digital Signal

Processing with Field Programable Gate Arrays. Springer-Verlag, Berlin.

[3] Sunkara, L.D., 2004. Design of Custom Instruction Set for FFT using FPGA –Based Nios Processors. Thesis

(a)

(b)