BAB VIII REGISTER DAN COUNTER

8.1

Register

Dalam elektronika digital seringkali diperlukan penyimpan data sementara sebelum data diolah lebih lanjut. Elemen penyimpan dasar adalah flip-flop. Setiap flip-flop menyimpan sebuah bit data. Sehingga untuk menyimpan data n-bit, diperlukan n buah flip-flop yang disusun sedemikian rupa dalam bentuk register. Suatu memori register menyimpan data 1001 dapat ditunjukkan secara blok diagram seperti gambar 8.1.

1 0 0 1

Gambar 8.1 Blok diagram register memori 4-bit

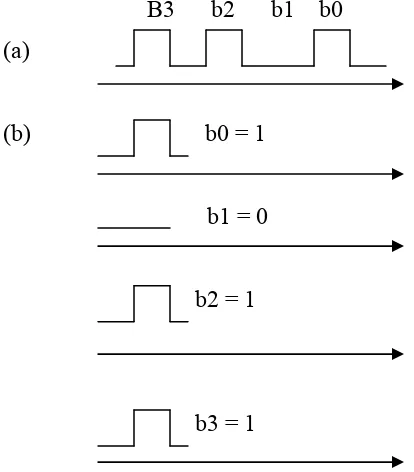

Data biner dapat dipindahkan secara seri atau parallel (lihat gambar 8.2) B3 b2 b1 b0

(a)

(b) b0 = 1

b1 = 0

b2 = 1

b3 = 1

Gambar 8.2 Transfer data (a) mode seri , dan (b) mode paralel

clock. Ada empat cara dimana register dapat digunakan untuk menyimpan dan memindahkan data dari satu bagian ke bagian sistem yang lain :

1. Serial input paralel output ( SIPO ) 2. Serial input serial output ( SISO ) 3. Paralel input parallel output ( PIPO ) 4. Paralel input serial output ( PISO )

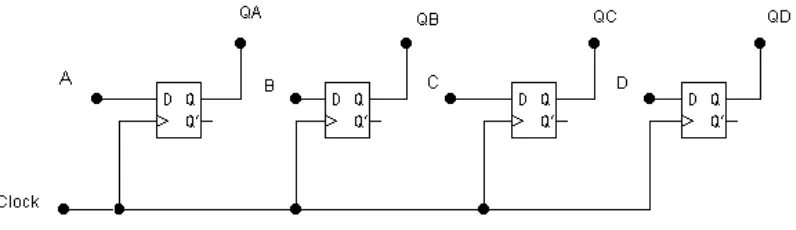

Beberapa tipe flip-flop dapat digunakan untuk membuat suatu register. Jika D FF digunakan untuk membentuk register memori 4-bit, susunannya dapat dilihat pada gambar 8.3.

Gambar 8.3 Rangkaian register memori 4-bit

Pada gambar 8.3 ditunjukkan sebuah register memori 4 bit yang terdiri dari 4 buah D FF. Data input dimasukkan secara paralel pada terminal A, B, C, dan D. Data pada input akan di transfer ke output setiap ada pulsa clock secara paralel juga. Karena data input masuk secara paralel dan output juga secara paralel maka rangkaian di atas disebut sebagai Paralel Input dan Paralel Output (PIPO).

Data yang disimpan pada rangkaian 8.3 tidak dapat digeser dari satu D FF ke D FF yang lainnya. Jika output QA dihubungkan ke input B, data akan di geser dari kiri ke kanan yang dikenal sebagai shift register, seperti ditunjukkan pada gambar 8.4.

kedua berpindah ke output QA. Proses perpindahan data akan berlanjut sampai 4-bit. Data dapat dibaca secara paralel dari QA, QB, QC, dan QD secara simultan, dikenal sebagai Serial Input Serial Output (SISO).

Gambar 8.4 Shift Register 4-bit

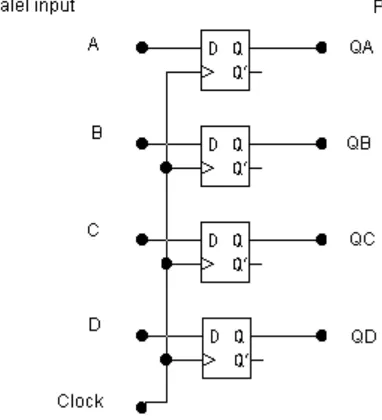

Shift register juga dapat disusun dari SR FF atau JK FF, dengan penambahan fasilitas Preset dan Clear. Rangkaian dapat digunakan untuk serial input maupun paralel input. Untuk paralel input dan paralel output dapat ditunjukkan pada gambar 8.5

Gambar 8.5 Register paralel input paralel output

8.2

Counter

dipelajari beberapa jenis rangkaian counter yang paling luas penggunaannya secara mendetail. Meskipun rangkaian – rangkaian tersebut tersedia sebagai IC, namun operasi internalnya masih patut mendapat perhatian karena pentingnya teknik-teknik dan prinsip-prinsip yang digunakan dan dapat diperluas untuk pemakaian-pemakaian lain.

8.2.1

Counter-Counter Asinkron

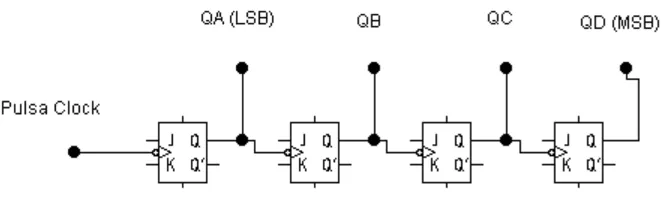

Gambar 8.6 menunjukkan suatu rangkaian counter biner 4-bit, poin-poin berikut yang berkenaan dengan operasinya :

1. Pulsa clock hanya diberikan kepada CLK input dari FF A. Jadi, FF A akan toggle setiap saat pulsa-pulsa CLK melakukan transisi negatip (Tinggi ke Rendah). Ingat bahwa untuk semua J=K=1.

2. Output FF A berfungsi sebagai CLK input untuk FF B, sehingga FF B akan toggle setiap saat output A berubah dari 1 ke 0. Demikian juga FF C akan toggle pada saat B berubah dari 1 ke 0 dan FF D akan toggle apabila C berubah dari 1 ke 0. 3. Tabel 8.1 menunjukkan urutan keadaan-keadaan biner, dengan D sebagai MSB

dan A sebagai LSB maka akan dihasilkan urutan counting biner dari 0000 sampai 1111.

4. Setelah terjadi pulsa ke 15, counter FF berada dalam keadaan 111. Atas komando pulsa clock yang ke 16 FF A beruabah dari 1 ke 0, yang menyebabkan FF B berubah dari 1 ke 0, dan seterusnya sampai counter berada dalam keadaan 0000. Dengan kata lain, counter tersebut telah melewati satu cycle lengkap dan telah recycled kembali ke 0000, dimana counter akan mulai suatu cycle counting baru apabila diberikan pulsa-pulsa clock berikutnya.

* Semua J dan K input diasumsikan sama dengan 1.

cycle lengkap sebelum recycle kembali ke kedudukan permulaannya. Mod number dengan mudah dapat diperbesar dengan menambah lebih banyak FF pada counter. Yaitu :

Modulo number = 2N

Dimana N adalah jumlah FF yang dihubungkan dalam susunan counter. Misalnya apabila digunakan lima FF, maka akan didapatkan mod-32 counter (25 = 32), yang berarti

memiliki 32 kedudukan yang berbeda (00000 sampai 11111).

8.2.2

Self-Stopping Ripple Counter

Ada kemungkinan untuk memakai counter gambar 8.6 dan memodifikasi sedemikian rupa hingga hanya menghitung sampai nilai biner tertentu dan kemudian berhenti menghitung meskipun pulsa clock terus menerus diberikan. Misalnya, 4-bit ripple counter normalnya akan menghitung sampai 1111 (15). Apabila kita akan menghitung sampai 1001 (desimal 9) dan kemudian berhenti, rangkaiannya dapat ditunjukkan seperti gambar 8.7.

* Input J dan K dari FF B, C, D semuanya sama dengan 1

Gambar 8.7 Self stopping ripple counter yang berhenti pada 1001

8.2.3

Counter-Counter dengan Sembarang/Setiap Mod Number

* Semua input J dan K dari FF A, B, dan C semuanya sama dengan 1

Gambar 8.8 Mod-6 counter dengan meng-clear suatu mod-8 counter pada saat terjadi hitungan keenam (110)

8.2.4

Counter Sinkron

Masalah yang dihadapi ripple counter disebabkan oleh berakumulasinya penundaan perambatan FF. Kesukaran-kesukaran ini dapat diatasi dengan menggunakan counter sinkron atau paralel, dimana semua FF di-trigger secara serentak (secara paralel) oleh pulsa clock. Karena pulsa-pulsa input diberikan kepada semua FF, maka harus digunakan beberapa cara untuk mengontrol kapan tiap-tiap FF harus toggle atau diam tak terpengaruh oleh suatu pulsa clock.

Berikut dibahas bagaimana merancang counter sinkron modulo-8 dengan menggunakan JK Flip-Flop.

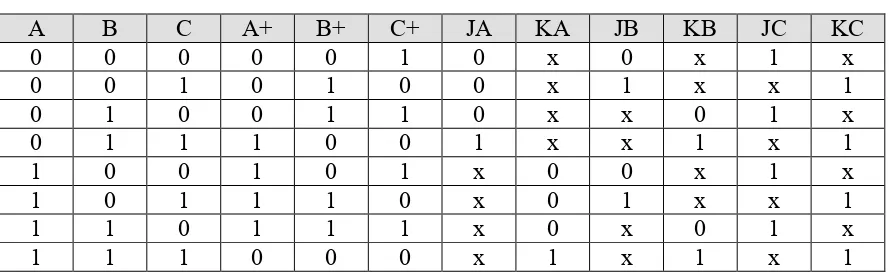

Tabel 8.2 Tabel counter mod-8 binary counter

Untuk menganalisis lebih lanjut harus diingat tabel exitasi dari JK FF, seperti ditunjukkan pada tabel 8.3

Tabel 8.3 tabel exitasi untuk JK Flip-Flop Present

Langkah perancangan selanjutnya yaitu dengan menggunakan tabel present state, next state dan exitasi Jk FF seperti ditunjukkan tabel 8.4

Tabel 8.4

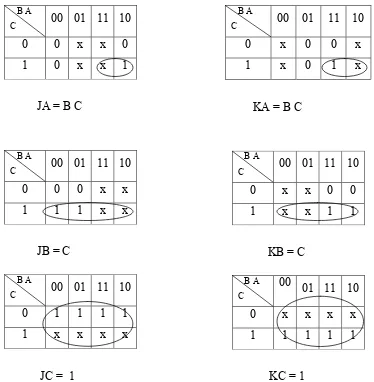

JA = B C Gambar 8.9 Implementasi JK FF sebagai counter sinkron modulo-8

Soal :

1. Buatlah counter asinkron modulo-5 dari JK Flip-Flop 2. Buatlah counter sinkron modulo-5 dari JK Flip-Flop