1

BAB I. PENDAHULUAN

1.1. Latar Belakang

Failure adalah ketidakmampuan dari sebuah sistem untuk melakukan operasi dari kebutuhan yang telah ditetapkan (Chillarege, 2014). Fault adalah beberapa sebab yang mengakibatkan terjadinya failure (Chillarege, 2014). Sebuah sistem mempunyai peluang terjadinya fault dan failure, sehingga diperlukan fault tolerance.

Fault Tolerance adalah watak sistem yang didesain untuk tetap dapat menjalankan operasinya secara normal walaupun terjadi fault pada sistem (Straka et al., 2010). Ide untuk mengatasi fault tolerance dengan menambahkan redundancy dalam rangka menambah reliabilitas sistem telah dilakukan (Neumann, 1956). Pendekatan umum pada desain fault tolerance adalah dengan menggunakan redundancy untuk memungkinkan operasi berjalan dengan normal pada sebuah sistem setelah terjadinya fault pada bagian tertentu (Shinghal dan Chandra, 2011).

Sub sistem satelit On-Board Computer (OBC) harus robust, karena OBC mempunyai peran penting dalam mengatur operasi-operasi satelit. OBC bertugas untuk monitoring, pengendalian, akusisi, analisa, pengambilan keputusan dan eksekusi dari suatu perintah (Maral dan Bousquet, 2002). Karena perannya yang penting maka OBC tersebut harus mempunyai fault tolerance yang baik.

Terdapat beberapa keuntungan jika OBC dibuat dengan Field Programmable Gate Array (FPGA). FPGA memungkinkan desainer untuk melakukan rekonfigurasi gerbang (logic) dan sambungan (route). Desainer akan diberikan keleluasaan untuk memilih komponen-komponen yang dibutuhkan. Pada perkembangan terakhir ini FPGA mampu direkonfigurasi secara dinamik disebut dengan Dynamic Partial Reconfiguration (DPR) (Lagger et al., 2006). Bagian/porsi FPGA lain akan tetap bekerja pada saat dilakukan rekonfigurasi, sehingga tidak mengganggu sistem operasi yang sedang berlangsung (Upegui et al., 2005). Berikut beberapa alasan dalam pemilihan FPGA (Xilinx, 2014):

2 1. Customize: Pemilihan komponen dapat dilakukan sesuai dengan kebutuhan OBC secara spesifik, dipastikan komponen yang tidak dibutuhkan tidak berada pada FPGA.

2. Mampu bekerja secara paralel: FPGA dapat menjalankan tugas-tugasnya secara paralel karena FPGA dapat dikonfigurasi untuk bekerja pada time frame yang sama pada masing-masing pekerjaan. 3. Dynamic Partial Reconfiguration (DPR): Konfigurasi FPGA secara

dinamik dari sebagian porsi FPGA tanpa menganggu porsi FPGA lain yang sedang running dapat dilakukan. FPGA mengakomodasi task atau fungsi lebih banyak tanpa memenuhi memori dari FPGA, karena task akan dimasukkan pada memori FPGA hanya pada saat task dibutuhkan. DPR juga dapat digunakan untuk melakukan efisiensi dalam penggunaan power pada FPGA.

4. Non-Recurring Engineering (NRE): biaya untuk penelitian, pengembangan, desain, dan tes pada produk baru pada FPGA lebih sedikit dibandingkan dengan Application-Specific Integrated Circuit (ASIC). ASIC membutuhkan tools dan fabrication labs yang lebih lengkap dan mahal.

5. Time To Market lebih cepat dibandingkan dengan ASIC karena development yang lebih cepat.

6. Unjuk kerja lebih baik dibandingkan dengan Mikrokontroler dari sisi kecepatan dan fleksibilitas pemrograman.

Beberapa permasalahan atau isu yang tidak dapat dipecahkan pada saat menggunakan mikrokontroler pada pembuatan OBC sebelumnya diantaranya adalah:

1. Mikrokontroler mempunyai limitasi terhadap waktu, untuk mencapai hasil operasi yang lebih, membutuhkan clock yang lebih besar pada mikrokontroler tersebut. Dengan FPGA kendala pada saat pemrosesan data gambar hyper spectral yang membutuhkan komputasi yang besar dapat dilakukan dengan cepat (Gonzalez et al., 2009).

3 2. OBC berperan sebagai data handling yang harus menangani berbagai macam data dari beberapa sub sistem satelit. Ketika data tersebut datang bersamaan dan diperlukan penanganan secara bersamaan maka akan muncul kekhawatiran tentang Interrupt Service Rutin (ISR). Seberapa lama penanganan data tersebut dan apakah mampu menangani seluruh interrupt yang datang dari sub sistem yang lain. Berbeda dengan FPGA, FPGA bekerja dengan memfokuskan pada sistem paralel sehingga tidak khawatir akan kehilangan interrupt. 3. FPGA mampu dikonfigurasi dengan mudah untuk beradaptasi dengan

misi requirement satelit (Huber et al., 2007). Pada mikrokontroler tidak akan mampu mengubah-ubah konfigurasi komponen yang sudah ada hal ini menyebabkan kesulitan dalam beradaptasi pada perubahan misi satelit yang sudah di orbit.

Seperti komponen elektronik lainnya, FPGA termasuk salah satu komponen yang rentan terhadap radiasi. Pada lingkungan luar angkasa, radiasi adalah suatu hal yang sering terjadi. Efek dari radiasi menyebabkan error pada sirkuit elektronik (Fleetwood, 2004). Salah satu efek radiasi pada satelit adalah terjadinya Single Event Effects (SEE), yang menyebabkan perubahan nilai pada memori yang dikenal dengan istilah Single Event Upset (SEU) atau Multiple Event Upset (MEU) (Dodd dan Massengill, 2003). Semakin tinggi orbit akan semakin rentan terhadap SEE. Satelit mikro mempunyai berat antara 10 s.d. 100 kg. Satelit mikro pada umumnya beroperasi pada Low Earth Orbit (LEO) dengan ketinggian orbit dibawah 2000 km. Tercatat beberapa kali terdeteksi SEE pada satelit mikro yang berorbit di LEO (Bentoutou et al., 2010), dengan demikian desain dan implementasi fault tolerance pada sub sistem satelit mikro menjadi penting.

Terdapat beberapa teknik fault tolerance diantaranya adalah Triple Modular Redundancy (TMR), Nine Modular Redundancy (NMR), Readback memory, Checker, Error Detection and Correction (EDAC), dan lain lain. TMR adalah sistem fault tolerance dengan cara tripelisasi modul atau fungsi tertentu. Voter pada TMR bertindak membandingkan hasil dari ketiga modul, minimal dua dari modul tersebut menghasilkan hasil yang sama maka sistem dianggap berjalan

4 dengan baik (Sterpone dan Violante, 2005). TMR merupakan desain yang banyak digunakan (Sterpone dan Violante, 2005). TMR sistem sederhana dan tidak terlalu overhead. TMR telah dikembangkan diantaranya oleh Pratt et al. (2006), Straka et al. (2010), Sterpone dan Violante (2005) dan Straka et al. (2010). TMR tidak cukup untuk menanggulangi fault di orbit sepenuhnya, tercatat pada Alsat-1 bahwa terjadi radiasi yang menyebabkan kegagalan pada dua modul secara bersamaan (Bentoutou dan Mohammed, 2012). Untuk mengatasi keterbatasan TMR, Nine Modular redundancy (NMR) dikembangkan (Bentoutou, 2012). Sehingga NMR membutuhkan resource yang besar. Fault tolerance lain yang dikembangkan adalah dengan readback memory error (Altera, 2006) dan (Carmichael et al., 2000). Dengan melakukan pembacaan konfigurasi memori pada FPGA. Data yang telah dibaca dicek apakah ada yang error, jika ada error dilakukan mitigasi pada data yang error tersebut. Tetapi pendekatan ini memerlukan tambahan perangkat keras (Salewski dan Taylor, 2007). Readback memory menambahkan overhead pada sistem (Becker et al., 2009). Pada penelitian fault tolerance (Yui et al., 2003) metode Checker telah dikembangkan, akan tetapi membutuhkan effort kerja yang lebih karena kerumitan yang bertambah dalam desain (Salewski dan Taylor, 2007). Teknik lain adalah EDAC, yang dapat menambahkan tingkat robustness pada sistem. Jika terdapat kesalahan pada bit tertentu maka data masih akan tetap mampu dibaca dan dimitigasi. Sistem EDAC toleran terhadap kesalahan atau error pada data (Jacinto et al., 2011). EDAC digunakan untuk memitigasi jika terjadi Single Event Upset (SEU) (Jacinto et al., 2011). Penelitian yang dikembangkan hanya sebatas pada penanganan data. Seluruh fault tolerance yang dibahas tersebut bekerja pada seluruh lintasan orbit tanpa ada perubahan konfigurasi pada fault tolerance.

1.2. Rumusan Masalah

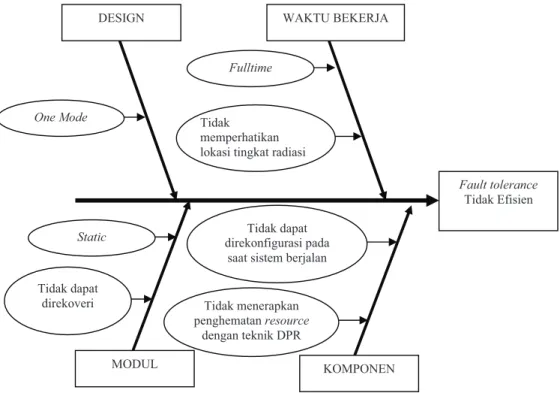

Pada umumnya desain sistem fault tolerance yang ada tidak mempertimbangkan tingkat radiasi pada orbit. Fault tolerance tersebut bekerja secara penuh baik dalam kondisi banyak radiasi atau tidak. Fault tolerance yang tidak mempertimbangkan tingkat radiasi pada lintasan orbit mengakibatkan pemakaian resource secara penuh tanpa ada efisiensi. Gambar 1.1 adalah diagram

5 tulang ikan rumusan masalah pada fault tolerance yang ada. Ada empat kelompok penyebab yang membuat fault tolerance tidak efisien yaitu ditinjau dari desain, waktu bekerja, modul dan komponen.

Gambar 1.1 Diagram diagram tulang ikan rumusan masalah

Kebutuhan robustness yang tinggi memerlukan resource yang besar, sedangkan resource pada satelit sangat terbatas (Ronga et al., 2008). Oleh karena itu diperlukan suatu sistem fault tolerance yang lebih efisien dengan memperhatikan tingkat radiasi, dimana tingkat radiasi kosmik dan proton yang berbahaya pada lintasan orbit berbeda-beda (Poivey et al., 2003). Merujuk pada penelitian tersebut perlu dikembangkan sebuah sistem fault tolerance yang memperhatikan kondisi tingkat radiasi pada orbit untuk mendapatkan tingkat efisiensi penggunaan resource yang ada secara maksimal.

1.3. Tujuan dan Manfaat Penelitian

Tujuan dari penelitian ini adalah untuk mengembangkan desain fault tolerance dan menganalisa desain yang dibuat. Pada penelitian ini dikembangkan

Tidak dapat direkonfigurasi pada

saat sistem berjalan

Fault tolerance Tidak Efisien KOMPONEN MODUL WAKTU BEKERJA DESIGN Tidak memperhatikan lokasi tingkat radiasi

Fulltime

One Mode

Static

Tidak dapat

direkoveri Tidak menerapkan

penghematan resource dengan teknik DPR

6 sebuah fault tolerance yang mampu beradaptasi pada lingkungan orbit sehingga penggunaan resource lebih efisien. Penggunaan resource yang besar hanya diterapkan pada saat dibutuhkan yaitu ketika satelit melintasi lokasi yang terdapat banyak radiasi berbahaya.

Manfaat dari penelitian ini adalah resource satelit yang terbatas dapat digunakan secara efisien sesuai dengan kebutuhan fault tolerance. Efisiensi dilakukan dengan mengurangi penggunaan resource pada saat satelit melewati lokasi yang tidak banyak terdapat radiasi berbahaya.

1.4. Batasan Penelitian

1. Fokus pada desain dan analisis fault tolerance yang bertujuan untuk mengatasi kegagalan operasi yang terjadi pada OBC yang disebabkan oleh radiasi berbahaya.

2. Fault tolerance menangani fault yang diakibatkan oleh Single Event Upset (SEU) atau Multiple Event Upset (MEU). Tidak diterapkan pada hardware yang diakibatkan oleh kerusakan atau kebakaran pada hardware atau chip FPGA.

3. Belum dilakukan pengujian yang mewakili kondisi orbit ruang angkasa, untuk mendapatkan tingkat efisiensi energi pada perbedaan kondisi seperti: gravitasi, kecepatan, dan temperatur.

4. Untuk memudahkan uji coba fault tolerance, tugas modul dibuat sederhana, sehingga sinkronisasi pada modul dapat dilakukan dengan memberikan clock. Sinkronisasi belum dilakukan pada modul yang komplek. Tidak dibahas analisa time dependant dan efisiensi komputasi. 5. Tidak dilakukan pengujian dengan fault injection wihtout contact,

sehingga belum dilakukan pemodelan skolastik radiasi pada orbit satelit dan analisis probabilistik.

6. Data GPS receiver yang digunakan diasumsikan selalu valid.

7. Fault tolerance hanya diterapkan pada non Geosynchronous orbit, pada penelitian ini akan dianalisa hanya pada Sun Synchronous Polar Orbit (SSPO). SSPO dipilih dikarenakan untuk menunjang kebutuhan misi penginderaan jauh.

7

1.5. Kontribusi

Penelitian tentang radiasi pada orbit menunjukkan bahwa tingkat radiasi pada lintasan orbit berbeda-beda, radiasi berbahaya banyak terjadi pada saat satelit berada pada area tertentu. Penelitian tentang fault tolerance yang ada, khususnya untuk satelit, tidak memperhatikan kondisi lintasan orbit tersebut. Apakah pada lintasan orbit tertentu mempunyai banyak radiasi berbahaya yang menyebabkan terjadinya fault pada sistem atau tidak. Jika fault tolerance yang didesain membutuhkan resource yang besar sebagai akibat kebutuhan robustness yang tinggi maka penghematan resource tidak dapat dilakukan, dalam hal ini fault tolerance yang didesain bekerja sepanjang waktu tanpa perubahan konfigurasi. Melihat hal tersebut, diperlukan kontribusi baru dalam cara pandang penerapan fault tolerance dengan dua mode. Pada saat terjadi banyak radiasi pada OBC maka diterapkan Critical Mode, jika tidak kembali ke Default Mode. Dengan penerapan hal itu membuat sistem yang didesain menjadi lebih efisien karena bekerja hanya pada saat yang dibutuhkan dan tingkat robustness akan tetap terjaga pada saat yang dibutuhkan. Sehingga kontribusi dari penelitian ini adalah menghasilkan desain fault tolerance dua mode yang lebih efisien yang dapat diimplementasikan pada FPGA.