TAPIS PELEWAT RENDAH DENGAN KAPASITOR TERSAKLAR (LOW PASS SWITCHED CAPASITOR FILTER )

TUGAS AKHIR

Diajukan untuk memenuhi salah satu Syarat Memperoleh Gelar Sarjana Teknik

Program Studi Teknik Elektro

Disusun oleh : Maria Rosanti Dadi Ramba

NIM : 995114065

JURUSAN TEKNIK ELEKTRONIKA

FAKULTAS TEKNIK

UNIVERSITAS SANATA DHARMA

YOGYAKARTA

TUGAS AKHIR

Diajukan untuk memenuhi salah satu Syarat Memperoleh Gelar Sarjana Teknik

Program Studi Teknik Elektro

Disusun oleh : Maria Rosanti Dadi Ramba

NIM : 995114065

JURUSAN TEKNIK ELEKTRONIKA

FAKULTAS TEKNIK

UNIVERSITAS SANATA DHARMA

YOGYAKARTA

2007

Tuhan tidak berjanji langit akan selalu biru

Bunga di sepanjang jalanmu,

Lautan tanpa gelombang.

Tapi ……

Ia berjanji beserta kita

Mendampingi kita dalam segala keadaan

Bersyukurlah untuk kesalahanmu, karena

Semuanya akan memberikan pelajaran berharga

Bersyukurlah untuk semua kesusahannmu dan itu semua akan menjadi berkatmu.

Bersyukurlah bila kamu tidak mengetahui semuanya, karena

Hal itu memberikan kesempatan padamu untuk belajar.

Skripsi ini kupersembahkan untuk :

Kemuliaan Tuhan di Surga dan untuk

Kedua orang tuaku serta kakak dan

adik-adikku.

Saya menyatakan dengan sesungguhnya bahwa skripsi yang saya tulis ini tidak memuat karya atau bagian karya orang lain, kecuali yang telah disebutkan dalam kutipan dan daftar pustaka, sebagaimana layaknya karya ilmiah.

Yogyakarta, 29 Januari 2007 Penulis

Maria Rosanti Dadi Ramba

Nama : Maria Rosanti Dadi Ramba Nim : 995114065

INTISARI

Berawal dari semakin berkembangnya teknologi khususnya teknologi

telekomunikasi antara lain telepon , radio dan berbagai alat elektronik, filter digunakan untuk membatasi arus listrik dengan frekuensi tertentu.

Penelitian ini membicarakan tentang tapis kapasitor tersaklar di mana nilai dari resistansi akan di ganti dengan sebuah kapasitor dan sakar MOS.

Penapis kapasitor tersaklar terdiri atas sebuah amplifier, kapasitor, dan saklar MOS. Nilai frekuensi cuttoff 5 Khz, dan frekuensi penyaklaran 150 Khz. Keluaran dari frekuensi generator digunakan sebagai masukan dari penapis kapasitor dan batasannya dari 10Hz sampai 50Khz.

Kata kunci : Penapis aktif, kapasitor tersaklar, penapis pelewat rendah.

Name: Maria Rosanti Dadi Ramba Nim :995114065

ABSTRACT

Early from progressivelly expand technological on specially telecomunications technology, for example telephone, radio, and various all electronic appliance, filter is used to limit the electrics current with the certain frequency that is required.

The objective of this research is about the low pass switched capasitor , where the value of resistansi of the filter would be change by capasitor and Mos switched.

The low pass switched capasitor filter consists of amplifier, capacitor,and MOS switched. Cutt off frequency is design about 5khz and the clock frequency is 150 Khz. The output from frequency generator is used as input to capasitor filter and it is about 10 Hz up to 5OKhz.

Keyword: Active filter,switched capasitor, low pass filter.

Puji dan syukur kepada Allah Bapa di surga, Allah Putera dan Allah Roh Kudus yang telah memberikan limpahan anugerah, kekuatan,kesabaran, kesehatan dan penghiburan sehingga penulis dapat menyelesaikan skripsi yang berjudul "TAPIS PELEWAT RENDAH DENGAN KAPASITOR TERSAKLAR “.

Penulisan skripsi ini dapat diselesaikan bukan atas usaha penulis sendiri melainkan juga berkat bantuan , dorongan dan bimbingan dari berbagai pihak. Oleh karena itu penulis ingin mengucapkan banyak terima kasih terutama kepada semua pihak yang telah membantu penulis hingga terselesaikannya skripsi ini. Ucapan terima kasih penulis sampaikan kepada :

1. Bapak A. Bayu Primawan, ST,M.Eng, selaku Ketua Jurusan Teknik Elektro Fakultas Teknik Universitas Sanata Dharma.Bapak Martanto, ST, MT, selaku dosen pembimbing skripsi yang telah membimbing dan memberikan saran.

2. Seluruh staf pengajar teknik elektro yang telah banyak memberikan pengetahuan dan bimbingan kepada penulis selaMa kuliah di Universitas Sanata Dharma.

4. Karyawan laboratorium Teknik Elektro yang telah banyak memberikan bantuan selama penulis mencari data di lab.

untuk menyelesaikan tugas akhirku.

6. Kakak dan adekku, Yani, Oscar, Helmin, Gundis yang selalu memotivasi diriku untuk cepat lulus dan mandiri.

7. Teman Seperjuanganku, Maya, Dagoel, Tutus, Bramsi, Guntur,lnyong, Dwi, Roni. Terima kasih untuk dukungan dan kebersamaan kita dalam penyelesaian skripsi ini.

8. Wulan dan Yono yang selalu membangkitkan semangatku disaat aku mulai merasajenuh dan lelah.

9. Temen-temen Teknik Elektro angkatan'99, terutama : Agnes, Maya, Edi Hesti, Cipuk, Winda, Ratin, Dini, Catur ...dan teman-teman yang tidak bisa penulis sebut satu persatu. Terima kasih atas kebersamaan, dan kekompakan kita.

10. Teman -teman di Griya Amada 52, Ida (thanks banget untuk komputemya), Yovika, Indah, Lia kuadrat, Aya ( thanks dipinjamin printemya), Ade, Ika, Nur, Helena.

I1. Mace Vero dan Pace Illy ( trims atas segala bantuan dan kebersamaan kita selama ini).

12. Semua pihak yang telah membantu penulis menyelesaikan skripsi ini.

membangun, sehingga di masa yang akan datang penulis mampu menghasilkan karya yang lebih baik.

Yogyakarta, 29 Januari 2007

Penulis

Maria Rosanti Dadi Ramba

HALAMAN JUDUL………. LEMBAR PENGESAHAN PEMBIMBING……….. LEMBAR PENGESAHAN PENGUJI……… HALAMAN PERSEMBAHAN ………. LEMBAR PERYATAAN KEASLIAN ARYA………. INTISARI………. ABSTRACT………. KATA PENGANTAR……….. DAFTAR ISI ………... DAFTAR GAMBAR……… DAFTAR TABEL ………..

BAB I PENDAHULUAN………

1.1 JUDUL………. 1.2 LATAR BELAKANG……….. 1.3 TUJUAN PENELITIAN……….. 1.4 MANFAAT PENELITIAN………. 1.5 PERUMUSAN MASALAH………. 1.6 BATASAN MASALAH……….. 1.7 SISTEMATIKA TULISAN ……….

BAB II DASAR TEORI……….

2.1.Pengertian Tapis………..

i ii iii iv v vi vii viii xi xiv xvi 1 1 1 2 3 3 4 4 6 6

12 12 14 15 17 19 20 20 20 20 22 23 24 26 31 31 32 35 36 37

2.4.Penapis Butterworth……….

2.4.1. Pendekatan Butterworth………..

2.4.2. lokasi kutub Butterworth………. 2.4.3. Untai tapis pelewat rendah orde satu……….. 2.4.4. Tapis pelewat rendah orde dua……… 2.4.5. Untai tapis pelewat rendah orde lebih dari dua………..

2.5.Kapasitor Tersaklar………

2.5.1. Saklar MOS………..

2.5.2. Konfigurasi saklar MOS……….

2.5.2.1. Saklar SPST……… 2.5.2.2.Saklar SPDT……… 2.5.2.3.Saklar DPDT………. 2.5.3. Dasar Kapasitor Tersaklar……….. 2.5.4. Operasi analog dari kapasitor tersaklar………..

BAB III PERANCANGAN TAPIS KAPASITOR TERSAKLAR………

3.1. Pembangkit detak dua fase non overlap……….. 3.2.Untai tapis pelewat rendah dengan kapasitor tersaklar

3.3. Nilai dari untai Tapis………..

BAB IV DATA PENGAMATAN DAN PEMBAHASAN………..

4.1. Pengamatan………..

DAFTAR PUSTAKA……….

LAMPIRAN

41

Gambar Halaman

2. 1. Kurva umum karakteristik penapis lolos rendah……….. 2.2. Kurva umum karakteristik penapis lolos inggi………. 2.3. Kurva umum karakteristik tapis pelewat jalur……….. 2.4. Kurva umum karakteristik tapis jalur henti……….. 2.5. Karakteristik Butterworth……….. 2.6. Tapis pelewat rendah orde I……… 2.7. Tapis pelewat rendah orde 2………. 2.8. Transistor MOS……… 2.9. Saklar SPST………. 2.10 Bentuk gelombang untuk mengaktifkan filter……….

2.11.Saklar SPDT………

2.12.Saklar DPDT………..

2.13.Untai dasar kapasitor tersaklar………. 2.14.Untai integrator analog………. 2.15.Untai integrator Dua Masukan………. 2.16.Untai Integrator tak membalik………. 2.17.Untai Integrator tak membalik masukan beda………..

3.1.Untai frekuensi detak dalam penyaklaran MOS………. 3.2.Tapis pelewat rendah orde I kapasitor tersaklar………. 3.3.Tapis Pelewat rendah orde 2 kapasitor tersaklar………..

8 9 10 11 15 16 17 20 21 21 22 24 25 26 27 28 29 30 31 32

Tabel Penguatan Teoritis……… 34

1.1.JUDUL

Tapis pelewat rendah dengan kapasitor tersaklar ( Low Pass Switched Capasitor Filter )

1.2. LATAR BELAKANG

Dewasa ini perkembangan teknologi baik dunia audio maupun visual sangatlah pesat. Ini terbukti dengan adanya temuan baru yang terus dikembangkan agar memperoleh hasil yang terbaik dan tidak ada habisnya dalam perkembangan.

Telah banyak kemudahan yang telah disumbangkan oleh dunia teknologi bagi kehidupan manusia. Salah satu bentuk kemajuan teknologi elektronika yang dapat dirasakan manfaatnya adalah penapis aktif. Banyak peralatan elektronika yang sering digunakan manusia dalam kehidupan sehari-hari menggunakan tapis sebagai salah satu komponennya; contohnya : radio, telephone, televisi, dan modem. Dengan adanya penapis, arus listrik dengan frekuensi-frekuensi tertentu bisa diatur sesuai kebutuhan sehingga memudahkan kita dalam mengatur atau menjalankan suatu alat yang hanya membutuhkan arus listrik dengan frekuensi tertentu.

Peran suatu penapis aktif yang begitu besar bagi peralatan-peralatan elektronik terkadang tidak disadari atau bahkan tidak diketahui. Memang bagi sebagian orang yang terpenting adalah bagaimana suatu peralatan dapat bekerja dengan baik. Bagi elektronis, penapis aktif adalah sesuatu hal yang harus diketahui, sehingga dengan pengetahuan yang dimiliki itu dapat menciptakan suatu alat yang menggunakan penapis sebagai salah satu komponennya.

Tapis tersusun atas komponen R,C dan sebuah amplifier yang sering disebut untai analog. Di sini penulis mencoba untuk merealisasikan untai analog tersebut ke dalam suatu rangkaian di mana resistor akan diganti dengan kapasitor dan saklar MOS yang disebut kapasitor tersaklar.

Diharapkan dengan adanya ide pembuatan Tapis pelewat rendah dengan kapasitor tersaklar ini dapat menumbuhkan dorongan bagi orang elektro untuk menciptakan sesuatu hal yang baru dalam dunia elektronika khususnya yang menggunakan penapis sebagai salah satu komponennya.

1.3. TUJUAN PENELITIAN

Tujuan dari penelitian ini adalah :

1.3.1. Mencoba mengimplementasikan pelajaran elektronika analog khususnya penapis aktif elektronika. 1.3.2. Menerapkan sistem kapasitor tersaklar sebagai pengganti resistor

1.4. MANFAAT PENELITIAN. Manfaat penelitian adalah :

1.4.1. Dengan terciptanya alat ini diharapkan dapat memperoleh suatu hasil yang akurat dan stabil dalam sistem analog.

1.4.2. Menambah pengetahuan tentang implementasi dan realisasi dalam pelajaran elektronika analog.

1.4.3. Timbulnya minat untuk mencoba menciptakan sesuatu hal baru dengan menggunakan penapis sebagai salah satu komponennya.

1.5. PERUMUSAN MASALAH

Dalam hal ini yang akan dibuat adalah merancang suatu penapis analog dengan nilai hambatannya diganti dengan sebuah kapasitor dan saklar MOS. Nilai hambatan equivalennya adalah 1 / ( Fclk x CR ) di mana Fclk adalah frekuensi penyaklaran dan CR adalah resistansi dari kapasitor yang disaklarkan.Tapis yang digunakan pada perancangan tersebut menggunakan tapis aktif pelewat rendah orde tiga yang telah diketahui nilai Fc dan Fclknya.

1.6. BATASAN MASALAH

1.6.1. Filter yang digunakan adalah low pass filter dengan orde tiga.

1.6.2. Frekuensi cut off (Fc) adalah 5 Khz dan frekuensi penyaklaran (Fclk ) adalah 150 Khz.

1.6.3. Tanggapan yang digunakan adalah tanggapan Butterworth. 1.6.4. Masukan frekuensi menggunakan AFG ( Audio Function Generator ) yang batasannya 10 Hz sampai dengan 50Khz.

1.7. SISTEMATIKA PENULISAN

Bab I. Pendahuluan

Menjelaskan tentang latar belakang, tujuan penelitian, manfaat penelitian, perumusan masalah, batasan masalah, dan sistematika penulisan.

Bab II. Dasar Teori.

Menjelaskan tentang teori dasar dari komponen-komponen yang akan digunakan dalam penelitian tersebut.

Bab III. Perancangan Alat.

Menjelaskan dan merancang untai tapis analog dengan kapasitor tersaklar pelewat rendah orde tiga.

Bab IV. Pengamatan dan pembahasan Alat.

Bab V. Penutup.

Berisi tentang kesimpulan terhadap seluruh pembahasan tentang Tapis pelewat rendah dengan kapasitor tersaklar.

2.1.Pengertian Tapis.

Tapis merupakan sebuah alat atau rangkaian yang menghasilkan karakteristik tangapan frekuensi yang telah ditentukan dengan tujuan melewatkan frekuensi tertentu dan menolak atau menahan frekuensi yang diinginkan.

2.2. Klasifikasi Tapis.

Berdasarkan komponen yang membentuknya maka tapis terdiri atas dua macam yaitu :

1. Tapis aktif

yaitu tapis yang tersusun atas resistor, kapasitor, dan sebuah penguat atau amplifier.

Kelebihannya :

a. Tidak perlu elemen induktor sehingga tidak ada masalah pada frekuensi rendah dan mudah diimplementasikan pada frekuensi rendah.

b. Karakteristik tanggapan frekuensi mendekati bentuk ideal. c. Ukuran fisik dan biaya dari rangkaian dapat ditekan dan murah. d.Tidak ada sinyal yang hilang. Hal ini disebabkan karena penguat

operasional mampu menyediakan penguatan atau gain sehingga sinyal masukan tidak akan hilang.

Kekurangannya :

a.Membutuhkan catudaya tersendiri.

b.Batasan praktis frekuensi 100 Khz (bekerja dengan sangat baik dibawah

100 Khz).

2. Tapis Pasif.

Yaitu tapis yang terdiri atas kombinasi resistor, kapasitor dan induktor.

Kelebihannya :

a. Memiliki karakteristik yang bagus pada frekuensi tinggi.

Kekurangannya :

a.Adanya masalah pada sisi rendah.

b.Biaya untuk pengadaan induktor relatif besar.

c.Ukuran fisik induktor semakin besar bila nilai induktansinya besar.

Namun berdasarkan tanggapan frekuensinya maka tapis terdiri atas :

a.Tapis pelewat rendah (low Pass Filter ) ialah tapis yang memiliki jalur

pelewat dari ω= 0 sampai ω =ωo, dengan ωo disebut sebagai frekuensi

pancung (cut off frekuensi ).

1

a t e n n u a s i

0 ωo

Gambar 2.1.a.karakteristik tapis pelewat rendah ideal

Pita lewat (Pass Band)

-20 dB/decade( 0rde 1)

-40 dB/decade( 0rde 2)

-60 dB/decade( 0rde 3) 0 dB 1

A dB

3dB 0,707

(stop Band)

0 ωo

Gambar 2.1.b. Karakteristik tapis pelewat rendah butterworth

2. Tapis Pelewat tinggi ( High Pass Filter ) merupakan komplemen dari

tapis pelewat rendah, dengan frekuensi dari 0 sampai ωo merupakan jalur

henti (stop band ), sedangkan jalur pelewat adalah dari frekuensi ωo

Karakteristiknya sebagai berikut:

1

A t e n u a s i

0 ωo

Gambar 2.2.a. Karakteristik tapis pelewat tinggi ideal

Pita lewat (Pass Band) 0,707

A dB

stop band 1

-20 dB/decade(0rde 1)

-40dB/decade(orde 2)

-60dB/decade(orde 3) 3dB

0dB

0 ωo

3. Tapis Pelewat jalur ( Band Pass Filter ) ialah tapis yang melewatkan

frekuensi antara ω1 sampai ω2, selain frekuensi ini tidak dilewatkan.

Karakteristiknya sebagai berikut:

atennuasi

1

0 ω1 ω2

gambar 2.3.a.Karakteristik tapis pelewat jalur ideal

dB

3 dB 0.707

0 ωl ωo ωh

Gambar 2.3.b. Karakteristik tapis pelewat jalur

4. Tapis jalur henti ( Band Elimination Filter ) merupakan komplemen dari

lainnya dilewatkan. Tapis ini sering dinamakan ‘notch filter’.

Karakteristiknya sebagai berikut :

atennuasi

1

0 ω1 ω2

Gambar 2.4.a.Karakteristik tapis jalur henti ideal

dB

3dB 0.707

0 ωl ωo ωh

Gambar 2.4.b. karakteristik tapis jalur henti butterworth.

2.3.Tapis pelewat rendah

Merupakan suatu penapis yang berfungsi untuk melewatkan semua frekuensi dari

ωo Hz sampai dengan frekuensi cut off, serta menahan semua frekuensi yang berada di

atas cut off. Frekuensi cut off adalah suatu frekuensi pada saat penguatan tegangan

turun ( drop )menjadi 0.707 atau –3 dB dari penguatan passbandnya.

Dalam analisis dan perancangan suatu penapis low pass filter merupakan suatu

prototipe yaitu suatu rangkaian dasar penapis yang dapat dimodifikasi untuk

mendapatkan rangkaian penapis lain. Untuk merealisasikan tapis dengan watak ideal

tidaklah mungkin. Hal ini disebabkan karena keterbatasan komponen. Karena itu

dalam perancangan suatu penapis aktif dikenal adanya istilah respons taksiran. Adapun

salah satu dari respons taksiran itu adalah Butterworth. Dari istilah respons taksiran itu

akhirnya lebih dikenal dengan nama penapis butterworth.

2.4. Penapis Butterworth.

Penapis butterworth adalah suatu penapis yang dirancang untuk menghasilkan

tanggapan datar (rata ) yang maksimal pada pass band sampai dengan frekuensi cut

off. Dengan kata lain tegangan keluaran tetap konstan pada hampir semua jalan ke

frekuensi cut off kemudian tegangan ini akan turun (roll-off ) pada 20n dB tiap decade

di mana n adalah jumlah orde penapis.

2.4.1. Pendekatan Butterworth.

dan imajiner. Bagian real dan imajiner dirumuskan sebagai berikut:

T (ω)= Re Tjω) +j im T(jω )... ( 2 –1 )

Bagian real dari persamaan ini merupakan fungsi genap sedangkan bagian imajiner

berfungsi ganjil. Ini berarti bahwa penggantian jω dengan –jω akan mengubah

tanda dari bagian imajiner tetapi tidak mengubah bagian real. Fungsi T (-jω)

disebut konyugat dari T (jω) yang dapat ditulis T (-jω) = T* ( jω). Dan diperoleh

hubungan:

⏐T (j ω)⏐2= T(jω) T(-jω)...( 2 – 2 ) Fungsi kuadrat dari magnitudo merupakan fungsi genap yakni ⏐T (j ω)⏐2 =⏐T (-j

ω)⏐2. Bila fungsi kuadrat magnitudo dituliskan sebagai suatu polinomial maka pembilang dan penyebut polinomial harus genap. Maka didapatkan :

2

yang besar yang dapat dicapai dengan membuat perbedaan derajad A dan B

sebesar mungkin . Pilihan ini akan memberikan ⏐T (jω)⏐ dengan n buah kutub

‘roll off dan T n(s) yang akan dikenal sebagai fungsi semua kutub.

roll-off= 6n dB/oktaf.Roll-off adalah kemiringan atau gradien garis pada stop band.

Dalam hal khusus, semua koefisien B kecuali Bo dan B2n, mempunyai nilai nol,

Ao = Bo sehingga :

= yang memberikan bentuk sederhana dari

persamaan 2 - 4 sebagai berikut :

Tanggapan ini dikenal sebagai tanggapan butterworth. Bila ωo dalam keadaan

ternormalisasi yaitu bernilai 1 maka :

2.4.2. Lokasi kutub Tapis Butterworth.

Untuk menentukan lokasi kutub-kutub dari tanggapan watak alih

butterworth, dapat menggunakan persamaan 2 – 2 dan persamaan 2 – 4 dengan ω=

1 dan ω= s/j, didapatkan :

Kutub-kutub dari persamaan 2 – 2 adalah akar-akar dari persamaan :

maka :

1 – s2 = ( 1 + s ) ( 1 – s ) = 0 ... ( 2 – 9 ) Sehingga lokasi kutub adalah s = ± 1. Kutub sebelah kanan berhubungan dengan

sistem yang tidak stabil sehingga dipilih kutub yang berada di bidang sebelah

sebelah kiri maka :

B1 = s + 1 dan

1 s

1 1 T

+

= ...( 2 – 10 )

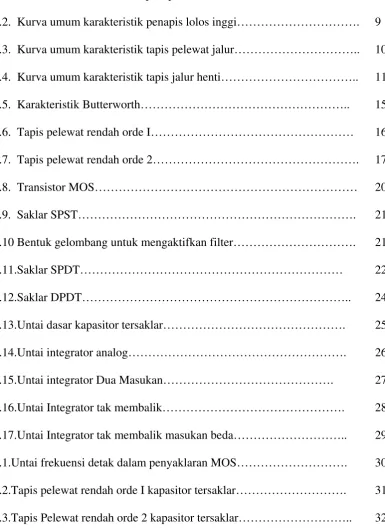

Sebagai contoh dari karakteristik Buterworth dapat dilihat pada gambar 2.5 berikut

yang berupa respons frekuensi butterworth low pass filter untuk orde 1 sampai

orde 6.

Gambar 2.5. Karakteristik Butterworth

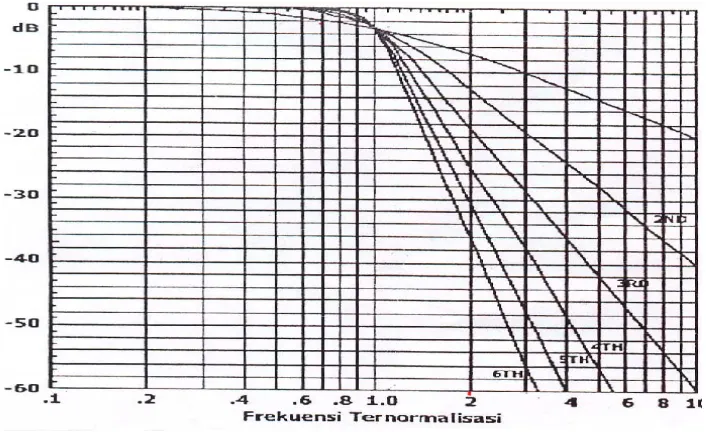

2.4.5.Untai tapis pelewat rendah orde 1.

yang terdiri atas satu resistor dan sebuah kapasitor ditambahkan sebuah penguat pada

tahap keluarannya, untuk mengurangi efek pembebanan. Untai ini ditunjukan pada

gambar 2.6 berikut ini :

Vout

Vi

C

+

-R Vi'

Gambar 2.6.Tapis pelewat rendah orde 1

Masukan isyarat pada penguat operasi diambil pada sisi masukan tak membalik

sedangkan pada masukan membalik mendapatkan umpan balik langsung dari keluaran

penguat operasi yang menghasilkan susunan penguat dengan faktor penguatan satu.

Sehingga tegangan Vi’ akan sama dengan tegangan Vo. Perbandingan tegangan

keluaran dan tegangan masukan dapat dicari dengan menggunakan superposisi

tegangan masukan dan ground pada titik Vi’. Bila watak alih dinyatakan dalam fungsi

jw (= s), dan dituliskan dengan persamaan T(s) maka akan didapatkan persamaan :

RC 1 s

RC 1 )

s ( T

+

= ...( 2 – 11 )

Sedangkan watak alih standar untuk orde satu yang ternormalisasi adalah :

o s

o )

s ( T

ω +

ω

Sehingga dengan membandingkan watak alih untai RC dengan watak alih standar

didapatkan frekuensi setengah daya untuk pelewat rendah sebesar

RC 1 o=

ω ...( 2 –1 3)

Dengan melihat watak alih tapis pelewat rendah ini dapat diketahui cara kerja dari

tapis ini. Bila frekuensi sama dengan nol maka besar tanggapan T (j 0 ) = 1, sedangkan

untuk frekuensi menuju besar tak hingga besar tanggapan akan menuju nol. Frekuensi

setengah daya besarnya berbanding terbalik dengan perbandingan R dan C. Nilai

ternormalisasi yakni ωo = 1, akan menghasilkan nilai R = 1 / C ,atau C = 1/ R dan

diambil nilai R = 1 dan C = 1.

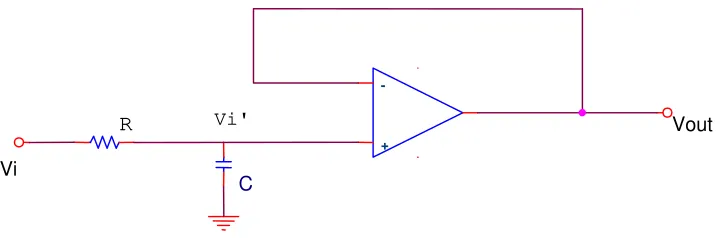

2.4.6. Tapis pelewat rendah orde 2.

Untai tapis pelewat rendah orde 2 dapat direalisasikan dengan untai sallen and key

yang dapat dilihat pada gambar 2.7.berikut :

Vin

Vout +

-R1

R2

C1 C2

Gambar 2.7. Tapis pelewat rendah orde 2

Untuk mencari frekuensi pusat dan faktor kualitas tapis Q, bisa dibandingkan dengan

watak alih tapis orde 2 standar. Watak alih tapis pelewat rendah standar adalah

Apabila diambil harga ωo =1, serta R1=R2=1, akan didapatkan nilai C1 dan C2

sebagai berikut:

Oleh karena tanggapan tapis yang dikehendaki berupa tanggapan Butterworth maka

nilai Q dari pelewat rendah orde 2 sama dengan 0,707. Sehingga untuk nilai-nilai

ternormalisasi didapatkan :

ωo = 1

C2 = 0,5 , dan

C1 = 2 ... ... ... ( 2 - 18 )

2.4.7. Untai tapis pelewat rendah orde lebih dari 2.

Untuk mendapatkan untai tapis pelewat rendah yang memiliki orde lebih dari 2

dilakukan dengan mengkaskade tapis pelewat rendah yang berorde 1 dengan orde 2

atau berorde 2 semua. Untuk tapis dengan orde ganjil salah satu untainya berupa untai

tapis orde 1, sedangkan untuk orde genap semua tersusun dari untai berorde 2.

Di dalam pembentukan tapis pelewat rendah berorde lebih dari dua perlu

diperhatikan bahwa faktor Q dari masing-masing bagian dari kaskade memiliki harga

yang tidak sama. Hal ini disebabkan karena untuk tanggapan Butterworth nilai Q

sudah tertentu sesuai dengan orde penapis. Misalkan untuk orde 4, memiliki dua

macam nilai Q yakni Q1= 1,3065 dan Q2 = 0,5412. Dari sini dapat dinyatakan bahwa

pembentukan tapis pelewat rendah Butterworth orde 4 tidak sama dengan

mengkaskade dua buah tapis pelewat rendah orde 2 yang nilai Q nya hanya satu

macam.

Tanggapan yang dikehendaki adalah Butterworth sehingga perhitungan nilai Q

harus disesuaikan dengan orde tapis yang akan dibangun . Watak alih tapis pelewat

rendah orde lebih dari dua besarnya merupakan perkalian dari watak alih tiap-tiap

pembangun kaskade. Frekuensi setengah daya dari masing-masing tapis pembangun

kaskade memiliki nilai yang sama yang juga merupakan frekuensi 3 dB dari

2.5.Kapasitor Tersaklar

Banyak fungsi penapis analog dibentuk oleh tapis aktif dengan Op-Amp dapat

ditiru dengan penggunaan untai kapasitor tersaklar. Untai kapasitor tersaklar dibangun

oleh op-Amp , saklar MOS dan kapasitor. Bila op-Amp terbuat dari MOSFET seluruh

jaringan kapasitor tersaklar tidak mengandung resistor yang dapat dibangun pada untai

integrasi tunggal.

2.5.1. Saklar MOS.

s G D

dielectriC

n n

P substrat

C

S D

VGS

a. b.

Pada gambar 2.8. Transistor MOS

Pada gambar 2.8. menunjukan penampang melintang dari suatu untai terpadu dari

transistor MOS. Salah satu penggunaannya adalah sebagai saklar bila tegangan kerja

antar sumber ( source ) dan gerbang ( gate ) adalah nol dan tegangan yang berharga

lebih besar dari tegangan ambang Vth.

2.5.2. Konfigurasi saklar MOS.

2.5.2.1. Saklar SPST

Dari gambar 2.8.b menunjukan suatu lambang transistor MOS. Tegangan yang

mempunyai resistansi sebesar RGS. Ketika transistor dalam mode ‘off’ yaitu bila

VGS sama dengan nol maka RGS mempunyai nilai yang sangat besar sekitar 100

Mohm-1000 Mohm. Sedangkan bila transistor pada keadaan ‘on’ yaitu bila VGS

melebihi tegangan ambangnya, maka RGS nya kecil nilainya yakni sekitar 10

Kohm-100 ohm, tergantung pada ukuran transistor dalam suatu keping. Gambar 2.9

berikut ini menunjukan saat saklar membuka atau menutup tergantung pada harga

dari VGS. Saklar demikian ini dikenal sebagai saklar SPST ( Single Pole Single

Throw).

S D

Gambar 2.9. Saklar SPST

Bentuk gelombang tegangan yang dipakai untuk mengaktifkan saklar MOS

diperlihatkan pada gambar 2 10.

φ

t Tc

Gambar 2.10. Bentuk gelombang untuk mengaktifkan saklar

Gelombang ini di hasilkan oleh sumber detak (Clock ) yang memiliki deretan pulsa

yang periodis dengan periode T.

Besaran ⎟

⎠ ⎞ ⎜ ⎝ ⎛ =

Tc 1

hal ini clock digunakan untuk mengaktifkan dan mematikan saklar MOS.

2.5.2.2. Saklar SPDT.

Merupakan saklar dimana dua buah MOS dikendalikan oleh dua bentuk

gelombang φ1 dan φ2 yang memiliki fase yang berbeda dengan frekuensi yang

sama. Keduanya tidak saling tumpang tindih (non-overlap). Bila φ1 on maka φ2

off.Dan sebaliknya bilaφ2 on maka φ1 off. Oleh karena itu antara titik 1dan titik 2

tidak terjadi hubungan langsung. Saat saklar pertama terhubung maka saklar kedua

terbuka dan sebaliknya. Sehingga saklar ini dinamakan single pole double throw.

Aksi penyaklaran dapat dilihat pada gambar 2.11. Saklar ini kemudian

diimplementasikan dengan dua buah saklar SPST yang dioperasikan dengan clock

dua fasa.

C C

φ1 φ2

a.

1 2

=C

1’ . 2’

1

2

1

C

’ 2

c.

Gambar 2.11. saklar SPDT

2.5.2.3.Saklar DPDT

Saklar ini dikembangkan dengan menggunakan saklar MOS SPST seperti

pada gambar 2.12.Dengan dua tegangan Clk φ1 dan φ2 yang dihubungi seperti

pada gambar a maka didapatkan saklar dua kutub dua posisi ( DPDT = Dual Pole

Dual Throw).

Untuk penerapan saklar seperti ini ditunjukan dengan gambar c dan d . Pada gambar

c , saat saklar menutup pada posisi a, kemudian capasitor dipindahkan pada posisi b,

maka V2 = via – vib. Jika vib = 0 dan via = V1 seperti pada gambar 2.12.d, maka V2

= vi , atau sebuah pembalik telah dibentuk yaitu keluaran adalah negatif

masukannya.

φ1 φ2

=

c1

2

3

4 C

Via

Vib

V2 C

B c

Via

Vib

V2 C

d.

Gambar 2.12. Saklar DPDT dan penerapannya.

2.5.3.Dasar Kapasitor tersaklar.

Kapasitor tersaklar ini berfungsi sebagai pengganti resistor. Untai kapasitor

tersaklar dibangun oleh op-Amp, saklar MOS dan kapasitor yang nilai kapasitansnya

kecil. Frekuensi kutub dan frekuensi nol dari untai kapasitor tersaklar dapat

dikendalikan dari luar melalui frekuensi clock.

Untuk kapasitor tersaklar dapat dilihat pada gambar 2.13 berikut ini:

ts

S 1

S 2 S 1

S 2

t

C

a b.

Saklar sinkronisasi s1 dan s2 membuka dan menutup setiap setengah siklus dari

interval clock Tc dan secara periodik memuati dan melucuti muatan pada kapasitor.

Untuk susunan ini akan berfungsi sebagai resistor, maka anggapan berikut ini harus

dipenuhi :

1. Pada suatu saat tertentu hanya ada satu saklar yang tertutup,

kedua saklar tak pernah tertutup secara serentak.

2. Selang waktu selama kedua saklar tidak tertutup sangat singkat

dibandingkan dengan periode detak Tc.

3. Apabila s1 tertutup, kapasitor memuati secara cepat tegangan

isyarat masukan Vs.

4. Apabila s2 tertutup, kapasitor segera melucuti muatan ke

ground.

Selama interval s1 tertutup,muatan kapasitor mencapai nilai

q = C Vs...( 2 – 19 )

Muatan ini secara lengkap dilucuti ke ground ketika s2 tertutup. Dalam satu

interval clock Tc muatan keseluruhan akibat tegangan Vs adalah :

Tc CVs t

q

= Δ Δ

... ...( 2 – 20 )

Muatan ini harus secara terus menerus disuplay ke kapasitor dengan sumber

muatan yang kontinyu dari Vs arus tunak (steady ) yang memiliki rerata

sama dengan:

tc CVs t

q ts 1 ) 1 ( i

tc

o = Δ Δ

=

∫

...( 2 – 21 )2.5.4. Operasi analog dari kapasitor tersaklar.

Operasi analog yang dipakai untuk penerapan kapasitor tersaklar

ada empat operasi analog tegangan meliputi penjumlahan, pengurangan ,

perkalian dan pengintegralan.

Berikut ini untai analog yang memakai komponen resistor kapasitor,

dan penguat operasi beserta dengan operasi kapasitor tersaklar dari

masing-masing untai :

a. Untai integrator pembalik.

Untai integrator pembalik ditunjukan pada gambar 2.14 berikut ini :

Vi

V2

-R1

C2

V 1

V 2

+

-CR

C 2

a. b.

Gambar 2.14. Untai integrator analog dan dengan kapasitor tersaklar.

s)

Untai integrator dengan kapasitor tersaklar didapatkan dengan

menggantikan R1 =RC1 di mana RC1= 1 / ( Fclk CR ) sehingga

didapatkan fungsi alih :

s)

Kedua rangkaian pada gambar 2.14 di atas merupakan untai pembalik

dan keduanya menunjukan suatu integrator. Hal yang penting dari

persamaan terakhir ialah terdapatnya perbandingan CR / C2. Dalam

teknologi M0S, bentuk kapasitor dapat dikendalikan dengan akurat.Oleh

karenanya perbandingan kapasitansi dapat direalisasikan secara akurat.

b. Integrator pembalik untuk dua masukan.

Jika diinginkan penjumlahan dua tegangan yang diintegralkan secara

bersama-sama maka dapat digunakan untai seperti pada gambar 2.15

yakni dengan pemasangan dua buah kapasitor tersaklar untuk masing-

masing resistor.

Dari gambar 2.15. didapatkan hubungan :

Sedangkan untuk untai dengan kapasitor tersaklar didapatkan hubungan

sebagai berikut :

s

Sehingga menghasilkan untai pembalik yang menjumlahkan dua

masukan dan mengalikannya dengan suatu konstanta.

c. Integrator tak membalik.

Untai integrator tak membalik ditunjukan pada gambar 2.16 berikut

ini.

Fungsi alih dari gambar 2.16 adalah :

Untai kapasitor tersaklar yang bersesuaian ditunjukan pada gambar b,

yang merupakan kombinasi dari integrator pembalik dan susunan

penyaklaran pembalik. Fungsi alihnya :

s

d. Integrator tak membalik untuk masukan beda.

Dengan adanya dua masukan Vo dan V1 pada gambar 2.18. berikut:

V0

Gambar 2.18. Integrator tak membalik dua masukan beda

maka dapat dituliskan hubungannya sebagai berikut :

s

Semua untai di atas dapat dipakai untuk operasi realisasi tapis dengan kapasitor

Dalam perancangan tapis pelewat rendah dengan kapasitor tersaklar ini membutuhkan frekuensi detak yang berfungsi mengaktifkan saklar- saklar MOS yang diperlukan. Frekuensi detak ini menentukan watak tapis dengan kapasitor tersaklar.

3.1. Pembangkit detak dua fase non overlap.

Untai frekuensi detak dalam penyaklaran MOS berupa pembangkit detak dua fase yang tidak saling tumpang tindih ( non-overlap ). Untuk mendapatkan detak yang non overlap digunakan rangkaian seperti yang ditunjukan pada gambar 3.1. di bawah ini :

- +

30 Φ1

Q 1

s 1

φ2 D 2

R 1

C

R

s 2 R 2

+

Q

1 Q

fin

φ1

Φ2

D 1 Q 2

Nn

φφφ1111

+

G

Gam

bGar

ww1 φ

+++ ++====Gambar 3.1.a. Untai pembangkit detak dua fase non-overlap

3.1.

f in

φ1 φ2

Keluaran rangkaian ini berupa fase φ1 dan φ2, yang tidak saling tumpang tindih.

Frekuensi isyarat keluaran besarnya adalah setengah dari ferekuensi masukan . Lebar

sela φ1 dan φ2 ditentukan oleh konstanta waktu RC yang terdapat pada flip-flop

pertama dari gambar 3.1.b.

Untuk mengaktifkan saklar-saklar MOS ada batas-batas frekuensi penyaklaran.

Dalam realisasi tapis pelewat rendah dengan kapasitor tersaklar dipakai saklar CMOS

4016 yang memiliki RON sekitar 200Ωdan penguat operasi yang dipergunakan adalah

LF 353N. Frekuensi penyaklaran maksimum ditentukan sebesar 500Khz.

Untuk batas bawahnya diambil frekuensi penyaklaran minimum sebesar 10 Khz

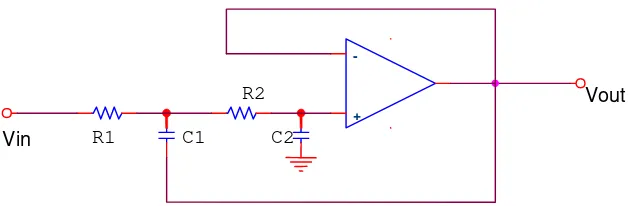

3.2.Untai Tapis pelewat rendah dengan kapasitor tersaklar.

Untai tapis pelewat rendah yang akan dimplementasikan adalah untai tapis dengan

orde tiga dimana nilai resistornya akan diganti dengan kapasitor tersaklar.

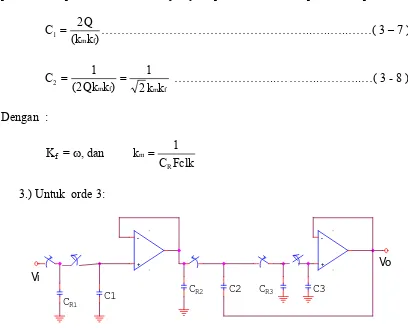

Rangkaian yang membentuk orde 3 terdiri dari bagian orde 1 dan diikuti orde 2.

Watak alih untai tapis ini merupakan perkalian dari masing-masing kaskade

pembentuk tapis.

1. Bagian Orde 1 :

V in

V o u t

CR C

+

gambar 3.3. Tapis pelewat rendah orde 1 dengan kapasitor tersaklar.

Dengan nilai frekuensi pusat sebesar :

Gambar 3.3. Tapis pelewat rendah orde 2 dengan kapasitor tersaklar

Dari gambar 3.3. maka watak alih orde 2 adalah :

Frekuensi pusatnya adalah :

Resistornya R1 = R2 akan didapatkan hubungan seperti berikut ini :

Dengan mengetahui pusat ωo dari perancangan serta nilai Q ( untuk n= 2 = 0,7071 ),

serta nilai kapasitansi pengganti R1 dan R2 yaitu CR1 = CR2 = CR, maka nilai-nilai

pada untai kapasitor tersaklar selanjutnya dapat ditentukan dari persamaan-persamaan

Watak alih orde 3 adalah perkalian dari masing-masing pembentuk kaskade:

3.3.Nilai dari untai tapis kapasitor tersaklar.

Sesuai dengan batasan masalah yang telah disebutkan bahwa untai yang digunakan

adalah untai tapis pelewat rendah orde 3 dimana nilai resistornya diganti dengan nilai

kapasitor tersaklar maka nilai yang dicari adalah untuk orde 3.dengan menggunakan

persamaan pada orde 3 maka kita mendapatkan nilainya sebagai berikut : Dengan

nilai Frekuensi pusat ( Fc) = 5 Khz dan Frekuensi penyaklaran ( Fclk ) = 150 Khz dan nilai

CR yang telah ditentukan sebesar 47 pF maka :

o

Qω

2 Fclk C

C R

3= ………..…….( 3 – 12 )

112pF

Khz) 5 π (2)(1)(2

Khz) pF)(150 (47

C3 = =

Setelah mendapatkan nilai-nilai nya maka rangkaian orde 3 nya adalah sebagai berikut :

Vi

Vo

+

-+

-47Pf 224Pf

47Pf 449Pf 47Pf

BAB IV

DATA PENGAMATAN DAN PEMBAHASAN

Salah satu watak tapis yang akan diamati adalah tanggapan frekuensi tapis. Tanggapan frekuensi tapis dinyatakan dalam besaran yang merupakan perbandingan tegangan isyarat keluaran tapis dengan tegangan isyarat masukan tapis sebagai fungsi frekuensi isyarat.

Isyarat keluaran dengan isyarat masukan dilakukan dengan memberikan isyarat masukan yang telah diketahui. Untuk mengetahui watak tapis yang lebih baik jangkauan frekuensi pengamatan 50 Kz atau lebih. Dari nilai yang diperoleh dilakukan perbandingan antara nilai-nilai amplitudo keluaran dengan masukan . Tanggapan akan bernilai positif bila amplitudo keluaran lebih besar dari amplitudo masukan, bernilai nol bila masukan sama dengan keluaran, dan bernilai negatif bila keluaran lebih kecil dari masukan. Setelah mendapatkan besarnya tanggapan untuk tiap frekuensi, maka agar dapat mengetahui kurva tanggapan tapis maka perlu diberikan grfafik hubungan antara besar peroleh dengan frekuensi.

Untuk mengetahui tanggapan tapis secara langsung dapat dilakukan dengan menguji untai yang telah dibuat dengan menggunakan analisa spektrum, yang dapat menampilkan tanggapan frekuensi dari tapis yang diuji.

Dalam pengamatan untuk tanggapan frekuensi tapis pelewat rendah tercantum dalam tabel 4.1

Untuk membandingkan tanggapan yang telah direalisasi dengan tapis analog maka perlu diketahui watak tapis teoritis, dengan menghitung nilai tanggapan teoritis untuk frekuensi isyarat yang sesuai dengan frekuensi pengamatan dengan menggunakan persamaan sebagai berikut :

⎥

Atn (f ) adalah tanggapan dalam dB, f adalah frekuensi isyarat dalam Hz, Fc adalah frekuensi cuttoff dan n adalah orde penapis, sehingga untuk tapis pelewat rendah, persamaanya adalah :

⎥

Dari pengamatan pada alat dengan fclk sebesar 150Khz sebesar 150 Khz dan Vi=8 vp didapatkan hasil keluaran ( Vo ) yang terdapat pada tabel 4.1. Dengan diketahui Vo maka didapatkan penguatan : ( ) 20log( )

Vi Vo f

A =

TABEL 4-1.

LPF = 3 Fclk = 150 Khz, Vi = 8Vp

Frekuensi(Hz) Vo(V) A(dB) At(dB)

10 8,000 0,000 0,000

20 8,000 0,000 0,000

100 8,000 0,000 0,000 500 8,000 0,000 0,003

1000 7,8000 -2,2199 -0,008

1500 7,8000 -2,2199 -0,0032

2000 7,800 -2,2199 -0,0673

2500 7,700 -0,5605 -0,1980

3000 7,600 -0,3329 -0,4831

3500 7,3000 -0.7950 -1,0111

4000 5,6000 -3,0980 -3,0103

5000 4,800 -4,4360 -6,0054

6000 3,650 -6,8150 -9,3093

7000 3,070 -8,3190 -10,9309

8000 2,650 --9,5960 -12,4986

9000 1,116 -17,1085 -15,4422

10000 0,870 -19,2714 -18,1291

12000 0,593 -22,600 -22,8385

15000 0,380 -26,4600 -28,6332,

20000 0,173 -33,300 -36,1274

3000 O,o70 -41,1590 -46,6892

4.2.Pembahasan

Dari data yang diperoleh adanya perbedaan tanggapan tapis yang terealisasi dengan tanggapan tapis teoritis. Hal ini disebabkan karena adanya hambatan ON pada saklar yang dipakai dalam realisasi tapis, akan menyebabkan penambahan nilai hambatan eqivalen kapasitor tersaklar. Bila Ron sama dengan nol, kapasitor akan termuati dengan cepat setelah kapasitor terhubung dengan sumber tegangan masukan , sehingga tegangan pafda kapasitor akan sama dengan tegangan masukan . Tetapi adanya hambatan Ron menyebabkan kenaikan hambatan eqivalen dari kapasitor tersaklar, akibatnya dapat menggeser frekuensi pancung yang telah dirancang.

Nilai hambatan eqivalen dari kapasitor tersaklar ditentukan oleh besarnya

frekuensi penyaklaran, dengan hubungan

R

fclkC

q 1

Re = . Adanya pengandaian bahwa

isyarat yang diproses dalam tapis merupakan isyarat analog, yang pada kenyataaannya terjadi proses pencuplikan isyarat, dapat menyebabkan suatu kesalaan antara teoritis dengan hasil tapis praktis.

Tapis dalam pengolahan isyarat listrik memiliki arti mengambil

suatukomponenfrekuensi tertentu dari isyarat dan menolak komponen frekuensi lain. TapisButterworth adalah tapis yang memiliki tanggapan datarsecara maksimal pada jalur lewat. Sebuah hambatan dapat diganti dengan menggunakan kapasitor tersaklar dengan

R

fclkC

q 1

Re = dengan fclk adalahfrekuensi clock dan Cr adalah

kapasitor tersaklar dan Req adalah resistansi.

Perancangan tapis Butterworth dengan menggunakan kapasitor tersaklar bisa dilakukan dengan terlebih dahulu merancang untai analognya dan kemudian

merealisasikan ke dalam untai kapasitor tersaklar dengan menggantikan resistor dengan kapasitor tersaklar.

Beberapa hal yang dapat menyebabkan kesalahan watak tapis hasil perancangan jika dibandingkan dengan hasil perhitungan antara lain: adanya nilai pendekatan yang ditetapkan pada saat perhitungan.

Eko Putranto, Afgianto, Penapis Aktif Elektronika: Teori dan Praktek, C.V.Gava Media Yogyakarta, 2002

Franco, S., Design with Operational Amplifier and Analog Integrated Circuit, Mc Graw Hill Book Co., Singapore, 1998

Parker, S P., Mc Graw Hill Concise Encyclopedia of science and Technology, Mc Graw Hill, Inc., New York, 1984

Http://www.google.com

LF353

Wide Bandwidth Dual JFET Input Operational Amplifier

General DescriptionThese devices are low cost, high speed, dual JFET input operational amplifiers with an internally trimmed input offset voltage (BI-FET II™ technology). They require low supply current yet maintain a large gain bandwidth product and fast slew rate. In addition, well matched high voltage JFET input devices provide very low input bias and offset currents. The LF353 is pin compatible with the standard LM1558 allowing designers to immediately upgrade the overall performance of existing LM1558 and LM358 designs.

These amplifiers may be used in applications such as high speed integrators, fast D/A converters, sample and hold circuits and many other circuits requiring low input offset voltage, low input bias current, high input impedance, high slew rate and wide bandwidth. The devices also exhibit low noise and offset voltage drift.

Features

n Internally trimmed offset voltage: 10 mV n Low input bias current: 50pA n Low input noise voltage: 25 nV/√Hz

n Low input noise current: 0.01 pA/√Hz

n Wide gain bandwidth: 4 MHz

n High slew rate: 13 V/µs

n Low supply current: 3.6 mA

n High input impedance: 1012Ω

n Low total harmonic distortion : ≤0.02% n Low 1/f noise corner: 50 Hz n Fast settling time to 0.01%: 2 µs

Typical Connection

Order Number LF353M, LF353MX or LF353N See NS Package Number M08A or N08E

BI-FET II™is a trademark of National Semiconductor Corporation.

W

Supply Voltage ±18V

Power Dissipation (Note 2)

Operating Temperature Range 0˚C to +70˚C

Tj(MAX) 150˚C

Differential Input Voltage ±30V Input Voltage Range (Note 3) ±15V Output Short Circuit Duration Continuous Storage Temperature Range −65˚C to +150˚C Lead Temp. (Soldering, 10 sec.) 260˚C Soldering Information

Dual-In-Line Package

Soldering (10 sec.) 260˚C

See AN-450 “Surface Mounting Methods and Their Effect on Product Reliability” for other methods of soldering surface mount devices.

ESD Tolerance (Note 8) 1000V

θJAM Package TBD

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. Elec-trical Characteristics state DC and AC elecElec-trical specifications under particu-lar test conditions which guarantee specific performance limits. This assumes that the device is within the Operating Ratings. Specifications are not guar-anteed for parameters where no limit is given, however, the typical value is a good indication of device performance.

DC Electrical Characteristics (Note 5)

Symbol Parameter Conditions LF353 Units

MIn Typ Max

VOS Input Offset Voltage RS=10kΩ, TA=25˚C 5 10 mV

Over Temperature 13 mV

∆VOS/∆T Average TC of Input Offset Voltage RS=10 kΩ 10 µV/˚C

Over Temperature 15 V/mV

VO Output Voltage Swing VS=±15V, RL=10kΩ ±12 ±13.5 V

VCM Input Common-Mode Voltage VS=±15V ±11 +15 V

Range −12 V

CMRR Common-Mode Rejection Ratio RS≤10kΩ 70 100 dB

PSRR Supply Voltage Rejection Ratio (Note 7) 70 100 dB

IS Supply Current 3.6 6.5 mA

AC Electrical Characteristics (Note 5)

Symbol Parameter Conditions LF353 Units

Min Typ Max

Amplifier to Amplifier Coupling TA=25˚C, f=1 Hz−20 kHz −120 dB (Input Referred)

SR Slew Rate VS=±15V, TA=25˚C 8.0 13 V/µs

GBW Gain Bandwidth Product VS=±15V, TA=25˚C 2.7 4 MHz

en Equivalent Input Noise Voltage TA=25˚C, RS=100Ω, 16 f=1000 Hz

in Equivalent Input Noise Current Tj=25˚C, f=1000 Hz 0.01

Symbol Parameter Conditions LF353 Units Min Typ Max

THD Total Harmonic Distortion AV=+10, RL=10k, VO=20Vp−p, BW=20 Hz-20 kHz

<0.02 %

Note 2: For operating at elevated temperatures, the device must be derated based on a thermal resistance of 115˚C/W typ junction to ambient for the N package, and 158˚C/W typ junction to ambient for the H package.

Note 3: Unless otherwise specified the absolute maximum negative input voltage is equal to the negative power supply voltage.

Note 4: The power dissipation limit, however, cannot be exceeded.

Note 5: These specifications apply for VS=±15V and 0˚C≤TA≤+70˚C. VOS, IBand IOSare measured at VCM=0.

Note 6: The input bias currents are junction leakage currents which approximately double for every 10˚C increase in the junction temperature, Tj. Due to the limited production test time, the input bias currents measured are correlated to junction temperature. In normal operation the junction temperature rises above the ambient temperature as a result of internal power dissipation, PD. Tj=TA+θjAPDwhereθjAis the thermal resistance from junction to ambient. Use of a heat sink is recommended if input bias current is to be kept to a minimum.

Note 7: Supply voltage rejection ratio is measured for both supply magnitudes increasing or decreasing simultaneously in accordance with common practice. VS =±6V to±15V.

Note 8: Human body model, 1.5 kΩin series with 100 pF.

Typical Performance Characteristics

Input Bias Current Input Bias Current

00564918

00564919

Supply Current Positive Common-Mode Input Voltage Limit

00564920

00564921

00564922 00564923

Negative Current Limit Voltage Swing

00564924 00564925

Output Voltage Swing Gain Bandwidth

00564926 00564927

Bode Plot Slew Rate

00564928 00564929

Distortion vs. Frequency Undistorted Output Voltage Swing

00564930 00564931

Open Loop Frequency Response Common-Mode Rejection Ratio

00564932 00564933

00564934 00564935

Open Loop Voltage Gain (V/V) Output Impedance

00564936 00564937

Inverter Settling Time

00564938

Small Signaling Inverting

00564904

Large Signal Inverting

00564906

00564905

Large Signal Non-Inverting

00564907

Current Limit (RL= 100Ω)

00564908

Application Hints

These devices are op amps with an internally trimmed input offset voltage and JFET input devices (BI-FET II). These JFETs have large reverse breakdown voltages from gate to source and drain eliminating the need for clamps across the inputs. Therefore, large differential input voltages can easily be accommodated without a large increase in input current. The maximum differential input voltage is independent of the

supply voltages. However, neither of the input voltages should be allowed to exceed the negative supply as this will cause large currents to flow which can result in a destroyed unit.

Exceeding the negative common-mode limit on either input will force the output to a high state, potentially causing a reversal of phase to the output. Exceeding the negative common-mode limit on both inputs will force the amplifier output to a high state. In neither case does a latch occur

operating mode.

Exceeding the positive common-mode limit on a single input will not change the phase of the output; however, if both inputs exceed the limit, the output of the amplifier will be forced to a high state.

The amplifiers will operate with a common-mode input volt-age equal to the positive supply; however, the gain band-width and slew rate may be decreased in this condition. When the negative common-mode voltage swings to within 3V of the negative supply, an increase in input offset voltage may occur.

Each amplifier is individually biased by a zener reference which allows normal circuit operation on ±6V power sup-plies. Supply voltages less than these may result in lower gain bandwidth and slew rate.

The amplifiers will drive a 2 kΩload resistance to±10V over the full temperature range of 0˚C to +70˚C. If the amplifier is forced to drive heavier load currents, however, an increase in input offset voltage may occur on the negative voltage swing and finally reach an active current limit on both posi-tive and negaposi-tive swings.

Precautions should be taken to ensure that the power supply for the integrated circuit never becomes reversed in polarity

As with most amplifiers, care should be taken with lead dress, component placement and supply decoupling in order to ensure stability. For example, resistors from the output to an input should be placed with the body close to the input to minimize “pick-up” and maximize the frequency of the feed-back pole by minimizing the capacitance from the input to ground.

A feedback pole is created when the feedback around any amplifier is resistive. The parallel resistance and capacitance from the input of the device (usually the inverting input) to AC ground set the frequency of the pole. In many instances the frequency of this pole is much greater than the expected 3 dB frequency of the closed loop gain and consequently there is negligible effect on stability margin. However, if the feed-back pole is less than approximately 6 times the expected 3 dB frequency a lead capacitor should be placed from the output to the input of the op amp. The value of the added capacitor should be such that the RC time constant of this capacitor and the resistance it parallels is greater than or equal to the original feedback pole time constant.

Detailed Schematic

00564909

Three-Band Active Tone Control

00564939

00564940

Note 1:All controls flat.

Note 2:Bass and treble boost, mid flat.

Note 3:Bass and treble cut, mid flat.

Note 4:Mid boost, bass and treble flat.

Note 5:Mid cut, bass and treble flat.

• All potentiometers are linear taper • Use the LF347 Quad for stereo applications

00564941

Fourth Order Low Pass Butterworth Filter

00564942

Fourth Order High Pass Butterworth Filter

00564943

00564944

Order Number LF353M or LF353MX NS Package Number M08A

Molded Dual-In-Line Package Order Number LF353N

NS Package N08E

LIFE SUPPORT POLICY

NATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

BANNED SUBSTANCE COMPLIANCE

National Semiconductor certifies that the products and packing materials meet the provisions of the Customer Products Stewardship Specification (CSP-9-111C2) and the Banned Substances and Materials of Interest Specification (CSP-9-111S2) and contain no ‘‘Banned Substances’’ as defined in CSP-9-111S2.

National Semiconductor Europe Customer Support Center

Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171 Japan Customer Support Center

Fax: 81-3-5639-7507

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper I.C. Handling Procedures. Copyright © Harris Corporation 1992

7-62

CMOS Dual ‘D’-Type Flip-Flop

Pinout

• High-Voltage Type (20V Rating)

• Set-Reset Capability

• Static Flip-Flop Operation - Retains State Indefinitely With Clock Level Either “High” Or “Low”

• Medium-Speed Operation - 16 MHz (typ.) Clock Toggle Rate at 10V

• Standardized Symmetrical Output Characteristics

• 100% Tested for Quiescent Current at 20V

• Maximum Input Current of 1µA at 18V Over Full

Pack-age Temperature Range; 100nA at 18V and +25oC

• Noise Margin (Over Full Package Temperature Range): - 1V at VDD = 5V

- 2V at VDD = 10V - 2.5V at VDD = 15V

• 5V, 10V and 15V Parametric Ratings

• Meets All Requirements of JEDEC Tentative Standard No. 13B, “Standard Specifications for Description of ‘B’ Series CMOS Devices”

Applications

• Registers

• Counters

• Control Circuits

Description

CD4013BMS consists of two identical, independent data type flip-flops. Each flip-flop has independent data, set, reset, and clock inputs and Q and Q outputs. These devices can be used for shift register applications, and, by connecting Q output to the data input, for counter and toggle applications. The logic level present at the D input is transferred to the Q output during the positive going transition of the clock pulse. Setting or resetting is independent of the clock and is accomplished by a high level on the set or reset line, respectively.

The CD4013BMS is supplied in these 14 lead outline pack-ages:

Braze Seal DIP H4Q Frit Seal DIP H1B Ceramic Flatpack H3W November 1994

7-63

(Voltage Referenced to VSS Terminals)

Input Voltage Range, All Inputs . . . .-0.5V to VDD +0.5V Maximum Package Power Dissipation (PD) at +125oC

For TA = -55oC to +100oC (Package Type D, F, K) . . . 500mW For TA = +100oC to +125oC (Package Type D, F, K) . . . . .Derate Linearity at 12mW/oC to 200mW Device Dissipation per Output Transistor . . . 100mW For TA = Full Package Temperature Range (All Package Types) Junction Temperature . . . +175oC

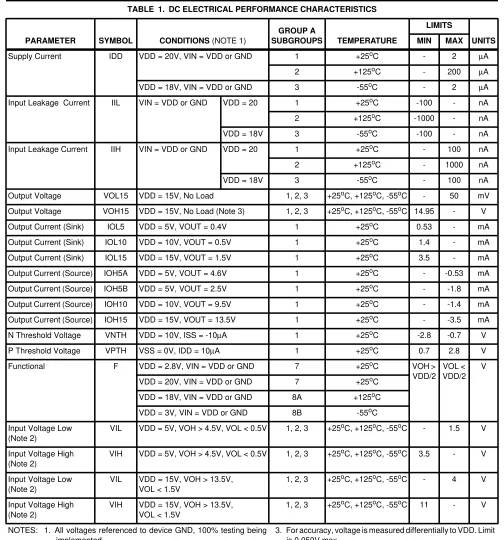

TABLE 1. DC ELECTRICAL PERFORMANCE CHARACTERISTICS

PARAMETER SYMBOL CONDITIONS(NOTE 1)

GROUP A

NOTES: 1. All voltages referenced to device GND, 100% testing being implemented.

2. Go/No Go test with limits applied to inputs

7-64

PARAMETER SYMBOL CONDITIONS(NOTE 1, 2)

GROUP A

2. -55oC and +125oC limits guaranteed, 100% testing being implemented.

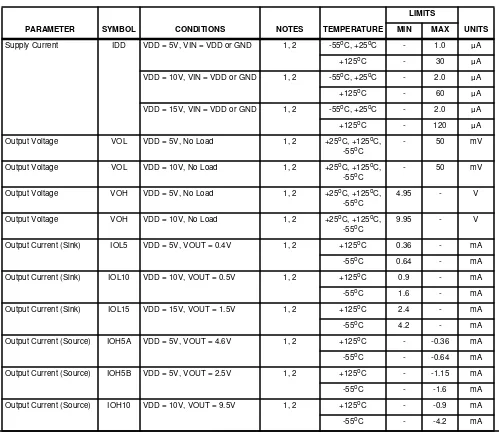

TABLE 3. ELECTRICAL PERFORMANCE CHARACTERISTICS

PARAMETER SYMBOL CONDITIONS NOTES TEMPERATURE

7-65

Minimum Set or Reset Pulse Width

1. All voltages referenced to device GND.

2. The parameters listed on Table 3 are controlled via design or process and are not directly tested. These parameters are characterized on initial design release and upon design changes which would affect these characteristics.

3. CL = 50pF, RL = 200K, Input TR, TF < 20ns.

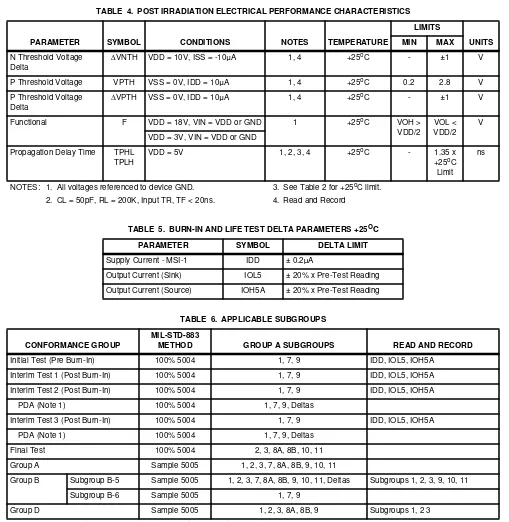

TABLE 4. POST IRRADIATION ELECTRICAL PERFORMANCE CHARACTERISTICS

PARAMETER SYMBOL CONDITIONS NOTES TEMPERATURE

LIMITS

UNITS

MIN MAX

Supply Current IDD VDD = 20V, VIN = VDD or GND 1, 4 +25oC - 7.5 µA

N Threshold Voltage VNTH VDD = 10V, ISS = -10µA 1, 4 +25oC -2.8 -0.2 V

PARAMETER SYMBOL CONDITIONS NOTES TEMPERATURE

LIMITS

UNITS

7-66

Propagation Delay Time TPHL TPLH

VDD = 5V 1, 2, 3, 4 +25oC - 1.35 x

+25oC

Limit ns

NOTES: 1. All voltages referenced to device GND. 2. CL = 50pF, RL = 200K, Input TR, TF < 20ns.

3. See Table 2 for +25oC limit. 4. Read and Record

TABLE 5. BURN-IN AND LIFE TEST DELTA PARAMETERS +25OC

PARAMETER SYMBOL DELTA LIMIT

Supply Current - MSI-1 IDD ± 0.2µA

Output Current (Sink) IOL5 ± 20% x Pre-Test Reading Output Current (Source) IOH5A ± 20% x Pre-Test Reading

TABLE 6. APPLICABLE SUBGROUPS

CONFORMANCE GROUP

MIL-STD-883

METHOD GROUP A SUBGROUPS READ AND RECORD

Initial Test (Pre Burn-In) 100% 5004 1, 7, 9 IDD, IOL5, IOH5A Interim Test 1 (Post Burn-In) 100% 5004 1, 7, 9 IDD, IOL5, IOH5A Interim Test 2 (Post Burn-In) 100% 5004 1, 7, 9 IDD, IOL5, IOH5A

PDA (Note 1) 100% 5004 1, 7, 9, Deltas

Interim Test 3 (Post Burn-In) 100% 5004 1, 7, 9 IDD, IOL5, IOH5A PDA (Note 1) 100% 5004 1, 7, 9, Deltas

Final Test 100% 5004 2, 3, 8A, 8B, 10, 11 Group A Sample 5005 1, 2, 3, 7, 8A, 8B, 9, 10, 11

Group B Subgroup B-5 Sample 5005 1, 2, 3, 7, 8A, 8B, 9, 10, 11, Deltas Subgroups 1, 2, 3, 9, 10, 11 Subgroup B-6 Sample 5005 1, 7, 9

Group D Sample 5005 1, 2, 3, 8A, 8B, 9 Subgroups 1, 2 3 NOTE: 1. 5% Parameteric, 3% Functional; Cumulative for Static 1 and 2.

TABLE 7. TOTAL DOSE IRRADIATION

CONFORMANCE GROUPS

MIL-STD-883 METHOD

TEST READ AND RECORD

PRE-IRRAD POST-IRRAD PRE-IRRAD POST-IRRAD

Group E Subgroup 2 5005 1, 7, 9 Table 4 1, 9 Table 4

PARAMETER SYMBOL CONDITIONS NOTES TEMPERATURE

LIMITS

UNITS

7-67

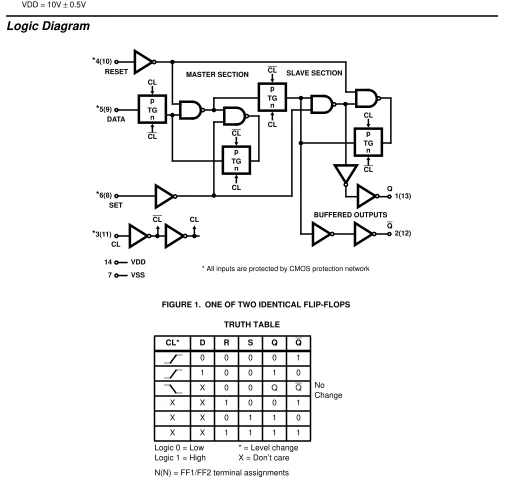

Logic Diagram

FIGURE 1. ONE OF TWO IDENTICAL FLIP-FLOPS

FUNCTION OPEN GROUND VDD 9V± -0.5V

OSCILLATOR

2. Each pin except VDD and GND will have a series resistor of 47K±5%; Group E, Subgroup 2, sample size is 4 dice/wafer, 0 failures, VDD = 10V± 0.5V N(N) = FF1/FF2 terminal assignments p

* All inputs are protected by CMOS protection network *4(10)

MASTER SECTION SLAVE SECTION

BUFFERED OUTPUTS

2(12) Q

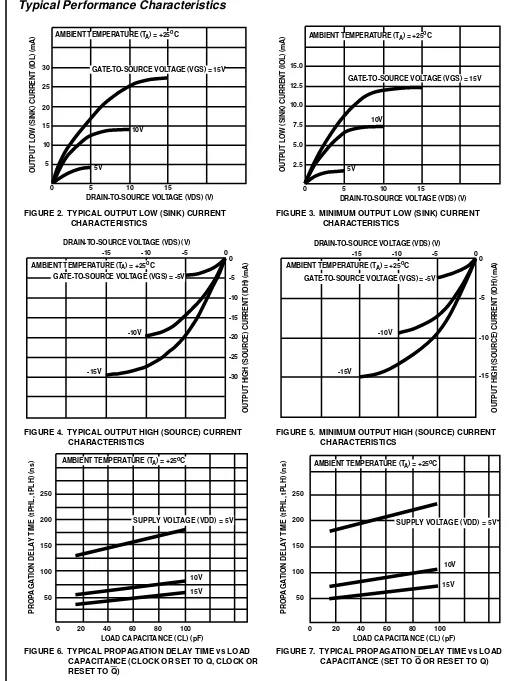

7-68 FIGURE 2. TYPICAL OUTPUT LOW (SINK) CURRENT

CHARACTERISTICS

FIGURE 3. MINIMUM OUTPUT LOW (SINK) CURRENT CHARACTERISTICS

FIGURE 4. TYPICAL OUTPUT HIGH (SOURCE) CURRENT CHARACTERISTICS

FIGURE 5. MINIMUM OUTPUT HIGH (SOURCE) CURRENT CHARACTERISTICS

FIGURE 6. TYPICAL PROPAGATION DELAY TIME vs LOAD CAPACITANCE (CLOCK OR SET TO Q, CLOCK OR RESET TO Q)

FIGURE 7. TYPICAL PROPAGATION DELAY TIME vs LOAD CAPACITANCE (SET TO Q OR RESET TO Q)

10V

5V

AMBIENT TEMPERATURE (TA) = +25oC

GATE-TO-SOURCE VOLTAGE (VGS) = 15V

0 5 10 15

DRAIN-TO-SOURCE VOLTAGE (VDS) (V)

OUTPUT LOW (SINK) CURRENT (IOL) (mA)

10V

5V

AMBIENT TEMPERATURE (TA) = +25oC

GATE-TO-SOURCE VOLTAGE (VGS) = 15V

0 5 10 15

DRAIN-TO-SOURCE VOLTAGE (VDS) (V)

OUTPUT LOW (SINK) CURRENT (IOL) (mA)

-10V

-15V

AMBIENT TEMPERATURE (TA) = +25oC

GATE-TO-SOURCE VOLTAGE (VGS) = -5V

0

-5

-10

-15 DRAIN-TO-SOURCE VOLTAGE (VDS) (V)

-20

OUTPUT HIGH (SOURCE) CURRENT (IOH) (mA)

-10V DRAIN-TO-SOURCE VOLTAGE (VDS) (V)

0 -5

-10 -15

OUTPUT HIGH (SOURCE) CURRENT (IOH) (mA)

GATE-TO-SOURCE VOLTAGE (VGS) = -5V

AMBIENT TEMPERATURE (TA) = +25oC

SUPPLY VOLTAGE (VDD) = 5V

PROP

AGA

TION DELA

Y TIME (tPHL, tPLH) (ns)

0 20 40 60 80 100 LOAD CAPACITANCE (CL) (pF)

AMBIENT TEMPERATURE (TA) = +25oC

SUPPLY VOLTAGE (VDD) = 5V

PROP

AGA

TION DELA

Y TIME (tPHL, tPLH) (ns)

0 20 40 60 80 100 LOAD CAPACITANCE (CL) (pF)

7-69

Chip Dimensions and Pad Layout

Dimension in parenthesis are in millimeters and are derived from the basic inch dimensions as indicated. Grid graduations are in mils (10-3 inch).

FIGURE 8. TYPICAL MAXIMUM CLOCK FREQUENCY vs SUPPLY VOLTAGE

FIGURE 9. TYPICAL POWER DISSIPATION vs FREQUENCY

AMBIENT TEMPERATURE (TA) = +25oC

CLOCK FREQUENCY (fCL) (MHz)

tr, tf = 5ns

SUPPLY VOLTAGE (VDD) (V)

SUPPLY VOLTAGE

TION PER DEVICE (PD) (

µ

INPUT FREQUENCY (ft) (HZ) CL = 50pF CL = 15pF

METALLIZATION: Thickness: 11kÅ−14kÅ, AL.

PASSIVATION: 10.4kÅ - 15.6kÅ, Silane

BOND PADS: 0.004 inches X 0.004 inches MIN

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper I.C. Handling Procedures. Copyright © Harris Corporation 1992

7-733

CMOS Quad Bilateral Switch

Applications

• Analog Signal Switching/Multiplexing

• Signal Gating

• Digital Signal Switching/Multiplexing

• CMOS Logic Implementation

• Analog to Digital & Digital to Analog Conversion

• Digital Control of Frequency, Impedance, Phase, and Analog Signal Gain

Description

CD4016BMS Series types are quad bilateral switches intended for the transmission or multiplexing of analog or digital signals. Each of the four independent bilateral switches has a single con-trol signal input which simultaneously biases both the p and n device in a given switch on or off.

The CD4016BMS is supplied in these 14 lead outline packages:

Braze Seal DIP H4Q Frit Seal DIP H1B Ceramic Flatpack H3W

Features

• Transmission or Multiplexing of Analog or Digital Signals

• High Voltage Type (20V Rating)

• 20V Digital or±10V Peak-to-Peak Switching

• 280Ω Typical On-State Resistance for 15V Operation

• Switch On-State Resistance Matched to Within 10Ω

Typ. Over 15V Signal Input Range

• High On/Off Output Voltage Ratio: 65dB Typ. at FIS =

10kHz, RL = 10kΩ

• High Degree of Linearity: <0.5% Distortion Typ. at FIS

= 1kHz, VIS = 5Vp-p, VDD-VSS ≥10V, RL = 10kΩ

• Extremely Low Off State Switch Leakage Resulting in Very Low Offset Current and High Effective Off State

Resistance: 100pA Typ. at VDD-VSS = 18V, TA = 25oC

• Extremely High Control Input Impedance (Control cir-cuit Isolated from Signal Circir-cuit: 1012Ω Typ.

• Low Crosstalk Between Switches: -50dB Typ. at FIS =

0.9MHz, RL = 1kΩ

• Matched Control Input to Signal Output Capacitance: Reduces Output Signal Transients

• Frequency Response, Switch On = 40MHz (Typ.)

• 100% Tested for Quiescent Current at 20V

• Maximum Control Input Current of 1µA at 18V Over Full

Package Temperature Range; 100nA at 18V at +25oC

7-734

(Voltage Referenced to VSS Terminals)

Input Voltage Range, All Inputs . . . .-0.5V to VDD +0.5V Maximum Package Power Dissipation (PD) at +125oC

For TA = -55oC to +100oC (Package Type D, F, K) . . . 500mW For TA = +100oC to +125oC (Package Type D, F, K) . . . . .Derate Linearity at 12mW/oC to 200mW Device Dissipation per Output Transistor . . . 100mW For TA = Full Package Temperature Range (All Package Types) Junction Temperature . . . +175oC

TABLE 1. DC ELECTRICAL PERFORMANCE CHARACTERISTICS

PARAMETER SYMBOL CONDITIONS(NOTE 1)