2.1. Field-Effect Transistor

Field-effect transistor (FET) atau transistor efek-medan merupakan transistor generasi lanjutan setelah bipolar junction transistor (BJT). FET adalah devais semikonduktor yang mempunyai tiga terminal, yang dapat digunakan untuk berbagai macam aplikasi elektronik maupun digital. Istilah field efect (efek medan listrik) sendiri berasal dari prinsip kerja transistor ini yang berkenaan dengan lapisan deplesi (depletion layer). Lapisan ini terbentuk antara semikonduktor tipe-n dan tipe-p, karena bergabungnya elektron dan lubang (hole) di sekitar daerah perbatasan. Sama seperti medan listrik, lapisan deplesi ini bisa membesar atau mengecil tergantung dari tegangan antara gate dengan source.

Gambar 2.1. memperlihatkan beberapa jenis FET yang terdapat di pasaran untuk berbagai macam aplikasi elektronik.

Gambar 2.1. Beberapa jenis FET yang ada di pasaran

Sumber: Oxner, Edwin S. Power FETs and Their Applications. New Jersey: Prentice-Hall, Inc. 1982. p.15.

2.1.1. Perbedaan FET dengan Transistor Bipolar

Transistor bipolar dibentuk berdasarkan dua tipe muatan, yaitu elektron bebas sebagai pembawa muatan negatif dan lubang (hole) sebagai pembawa muatan positif. Hal inilah yang menjadi sebab mengapa disebut bipolar, karena awalan “bi” menunjukkan arti “dua”. Sedangkan jenis lain dari transistor bipolar adalah transistor efek-medan atau field-effect transistor (FET). Sama seperti transistor bipolar, FET juga mempunyai tiga terminal, tetapi mempunyai prinsip kerja yang berbeda dengan transistor bipolar, piranti ini bersifat unipolar (satu jenis pembawa) karena beroperasi hanya berdasar pada sebuah tipe muatan, baik elektron bebas maupun lubang. Dengan kata lain, sebuah FET dalam operasinya bergantung pada aliran pembawa mayoritas (majority carriers) dan bukan pembawa minoritas (minority carriers). Karena beroperasi hanya pada satu tipe muatan, FET mempunyai noise yang lebih rendah dibandingkan transistor bipolar.

Secara umum, dibandingkan transistor bipolar, FET lebih mudah dibuat dan mengambil ruang yang lebih kecil di dalam suatu rangkaian terpadu, serta mempunyai konstruksi yang lebih sederhana dan bentuk ukuran yang lebih kecil, hal ini baik digunakan untuk rangkaian digital. FET juga mempunyai kestabilan yang baik terhadap variasi suhu dibandingkan dengan transistor bipolar. Dalam hal penguatan tegangan (voltage gain), FET lebih kecil dibandingkan dengan transistor bipolar. Untuk kebanyakan aplikasi linear, transistor bipolar adalah piranti yang banyak digunakan. Tetapi terdapat beberapa aplikasi linear yang lebih baik menggunakan FET karena impedansi masukan (input impedance) yang sangat tinggi, biasanya dalam ukuran megaohm (MΩ), dan terutama jika digunakan sebagai switch, FET lebih baik karena disipasi dayanya yang kecil. FET juga merupakan devais terkendali tegangan, seperti yang terlihat pada gambar 2.2.(b), yang berarti karakteristik keluaran dikendalikan oleh tegangan masukan. Adapun transistor bipolar adalah devais terkendali arus, yang berarti karakteristik keluaran dikendalikan oleh arus masukan, seperti yang ditunjukkan pada gambar 2.2.(a).

Gambar 2.2. (a) BJT sebagai devais terkendali arus (b) FET sebagai devais terkendali tegangan

Sumber: Boylestad, Robert, and Louis Nashelky. Electronic Devices And Circuit Theory. 9th ed. New Jersey: Pearson Prentice-Hall, Inc. 2006. p.361.

2.1.2. Klasifikasi Field-Effect Transistor

Terdapat tiga jenis dari field-effect transistor (FET), yaitu junction FET atau JFET, metal-oxide semiconductor FET atau MOSFET dan metal semiconductor FET atau MESFET. Ketiga jenis FET tersebut dibedakan berdasarkan struktur, karakteristik dan jenis isolasinya. Dalam JFET terdapat isolasi oleh sambungan pn (junction), dalam MOSFET terdapat isolasi oleh oksida logam, sedangkan dalam MESFET terdapat isolasi oleh sambungan semikonduktor logam. JFET, MOSFET, dan MESFET dibuat dari beberapa unsur-unsur dasar semikonduktor, yang mempunyai hubungan dalam daftar susunan unsur kimia. Unsur-unsur dasar yang membentuk JFET dan MOSFET adalah silicon (Si) dan germanium (Ge), sedangkan unsur-unsur dasar yang membentuk MESFET adalah gallium arsenide (GaAs).

JFET dibagi menjadi dua tipe yang dibedakan berdasarkan arah arus yang melewati kanal antara terminal drain dan source yaitu kanal-n (n-channel) dan kanal-p (p-channel). Pada MOSFET dan MESFET terdapat dua jenis mode yang dibedakan berdasarkan cara kerjanya, yaitu mode depletion dan mode enhancement. Dari kedua mode tersebut, pada MOSFET dibagi lagi menjadi masing-masing dua tipe yaitu kanal-n (n-channel) dan kanal-p (p-channel).

Sedangkan pada MESFET dari kedua mode tersebut, masing-masing hanya terdiri dari satu tipe saja, yaitu kanal-n (n-channel). Gambar 2.3. menunjukkan klasifikasi pembagian field-effect transistor secara umum.

Gambar 2.3. Klasifikasi field-effect transistor

JFET, MOSFET dan MESFET mempunyai perbedaan mendasar dalam hal bahan penyusunan serta analisa sistem kerjanyanya. Diketahui bahwa JFET mempunyai gate electrode yang tersebar dan tertanam di dalam suatu bahan semikonduktor. MOSFET mempunyai gate yang dipisahkan oleh suatu lapisan pembatas, yaitu oksida. Sedangkan MESFET mempunyai terminal gate yang yang terhubung dengan kanal-n melalui suatu konduktor metal. Dari situ dapat kita lihat dengan jelas perbedaan utama antara ketiga jenis FET tersebut.

2.2. Junction Field-Effect Transistor (JFET)

2.2.1. Konstruksi dan Karakteristik JFET

Konstruksi JFET berbeda dengan transistor bipolar. Pada transistor bipolar terdapat tiga bahan terpisah (dua bahan tipe-p, satu bahan tipe-n atau dua

Field-Effect Transistor J-FET p-channel n-channel MOSFET n-channel p-channel depletion enhancement n-channel p-channel MESFET enhancement depletion n-channel n-channel

bahan tipe-n, satu bahan tipe-p), sedangkan pada JFET hanya mempunyai dua bahan yaitu satu bahan tipe-n dan satu bahan tipe-p.

Pada gambar 2.4.(a) untuk konstruksi JFET kanal-n, dapat dilihat bahwa bagian terbesar dari struktur adalah bahan tipe-n yang membentuk saluran (kanal) antara lapisan dari bahan tipe-p. Bagian ujung atas dari kanal tipe-n terhubung pada terminal drain (D) melalui suatu ohmic contact, sedangkan ujung bawahnya terhubung pada terminal source (S) juga melalui suatu ohmic contact. Dua bahan tipe-p itu menyambung satu sama lain dan terhubung pada terminal gate (G). Terminal drain dan source terhubung melalui kanal tipe-n dan gate terhubung pada dua lapisan dari bahan tipe-p. Daerah deplesi (depletion region) merupakan dareah kosong yang menghubungkan antara bahan tipe-n dan bahan tipe-p pada saat JFET tidak mendapatkan aliran tegangan. Demikian juga sebaliknya untuk konstruksi JFET kanal-p pada gambar 2.4.(b).

Gambar 2.4. Konstruksi JFET, (a) kanal-n dan (b) kanal-p

Sumber: Boylestad, Robert, and Louis Nashelky. Electronic Devices And Circuit Theory. 9th ed. New Jersey: Pearson Prentice-Hall, Inc. 2006. p.362.

Mekanisme kerja JFET dapat dianalogikan seperti keran air. Air mengalir dari sumber air (source) menuju penampung (drain). Besar kecilnya air yang mengalir dari sumber dikendalikan oleh putaran keran (gate). Bila putaran keran semakin menutup, maka aliran air akan semakin kecil bahkan tidak ada aliran air. Demikian juga bila putaran keran semakin membuka, maka aliran air akan semakin membesar. Sumber dari tekanan air dapat dipersamakan pada

penggunaan tegangan dari drain ke source (VDS), dimana aliran air mengalir dari keran. Terminal drain dan source bekerja secara berkebalikan, seperti yang sudah dijelaskan sebelumnya. Pada JFET, aliran air yang dimaksud adalah arus elektron. Analogi keran air pada mekanisme kerja JFET ditunjukkan pada gambar 2.5.

Gambar 2.5. Analogi keran air pada mekanisme kerja JFET

Sumber: Boylestad, Robert, and Louis Nashelky. Electronic Devices And Circuit Theory. 9th ed. New Jersey: Pearson Prentice-Hall, Inc. 2006. p.362.

JFET mempunyai tiga terminal yaitu source (S), drain (D), dan gate (G). Ketiga terminal ini dapat dipandang ekuivalen dengan emmiter, collector dan base pada transistor BJT. Bahan yang menghubungkan source dan drain adalah kanal (channel). Jika bahan ini tipe-p, maka devais disebut JFET kanal-p, demikian juga bila bahan tipe-n, maka disebut JFET kanal-n.

Simbol dan bentuk struktur untuk JFET kanal-n dan kanal-p ditunjukkan pada gambar 2.6. dan gambar 2.7. Arah panah pada simbol JFET selalu dari bahan tipe-p ke bahan tipe-n. Pada kanal-n, arah panah menunjukkan arah arus gate (IG) yang mengalir dari bahan tipe-p menuju bahan tipe-n dimana kondisinya adalah bias maju (forward bias). Sebaliknya untuk kanal-p, kondisi yang terjadi adalah bias balik (reverse bias).

Gambar 2.6. Simbol dan konstruksi JFET kanal-n

Sumber: Kuphaldt, Tony R. Lessons In Electric Circuits. September, 13. 2005. <http://www.faqs.org/docs/electric/semi/semi_5.html>

Gambar 2.7. Simbol dan Konstruksi JFET kanal-p

Sumber: Kuphaldt, Tony R. Lessons In Electric Circuits. September, 13. 2005. <http://www.faqs.org/docs/electric/semi/semi_5.html>

2.2.2. Operasi Dasar JFET

Gambar 2.8. menunjukkan tegangan bias normal untuk JFET kanal-n. Tegangan catu drain adalah positif dan tegangan catu gate adalah negatif. Lapisan deplesi di seluruh tiap daerah p disebut dengan efek bidang. Gate tipe-p dan source tipe-n berasal dari dioda source-gate. JFET bekerja dengan membias-balikkan dioda source-gate. Karena bias pembalik, arus gate (IG) adalah kira-kira nol, yang ekuivalen dengan pernyataan bahwa JFET memiliki resistansi masukan yang hampir tak terbatas.

Gambar 2.8. Pembiasan Normal JFET kanal-n

Sumber: Malvino, Albert Paul. Prinsip-Prinsip Elektronika. (Alb. Joko Santoso). Jakarta: Salemba Teknika. 2003. p.427.

Pada gambar 2.8. dapat dilihat bahwa elektron mengalir dari source ke drain pasti melalui saluran sempit di antara lapisan deplesi. Ketika tegangan gate menjadi lebih negatif, lapisan deplesi meluas dan saluran yang berkaitan menjadi semakin sempit. Semakin negatif tegangan gate, semakin kecil arus antara source dan drain.

JFET adalah piranti yang dikendalikan oleh tegangan karena tegangan masukan mengendalikan arus keluaran. Dalam suatu JFET, tegangan gate ke sourceVGS menentukan seberapa besar aliran arus antara source dan drain. Ketika VGS menjadi nol, aliran arus drain maksimum menuju JFET. Di sisi lain, jika VGS menjadi cukup negatif, sentuhan lapisan deplesi dan arus drain akan mati.

Operasi JFET berdasarkan pada pengubahan lebar kanal untuk mengendalikan arus drain pada saat tegangan VDS diberikan pada drain dan source. Jika lebar kanal mengecil, maka resistansi kanal bertambah dan arus drain mengecil. Dengan memberikan bias balik ke sambungan gate-source maka daerah deplesi pada kanal bertambah, sehingga mengakibatkan lebar kanal mengecil.

Ada dua cara mengendalikan lebar kanal, yaitu:

1. Mengubah nilai tegangan gate-source (VGS) pada tegangan drain-source (VDS) yang konstan.

2. Mengubah nilai tegangan drain-source (VDS)pada tegangan gate-source (VGS) yang konstan.

Pengaruh VGS terhadap ID pada VDS konstan terlihat pada gambar 2.9. Jika VGS bertambah negatif, maka daerah deplesi bertambah dan lebar kanal menjadi berkurang (sempit), dengan demikian arus drain menjadi berkurang. Pengaruh VDS terhadap ID terlihat pada gambar 2.10. Bertambahnya VDS pada VGS konstan, mengakibatkan ID bertambah. Hal ini mengakibatkan daerah deplesi bertambah dan kanal menjadi sempit. Karena itu sampai pada nilai VDS tertentu, pertambahan VDS tidak menambah nilai ID. Pada VGS = 0, nilai VDS yang menyebabkan ID maksimum disebut tegangan pinch-off (tegangan jepit) VP.

Gambar 2.9. Pengaruh VGS terhadap lebar kanal pada VDS konstan

Sumber: Widodo, Thomas Sri. Elektronika Dasar. Jakarta: Salemba Teknika. 2002. p.74.

Gambar 2.10. Pengaruh VDS terhadap lebar kanal pada VGS konstan

Sumber: Widodo, Thomas Sri. Elektronika Dasar. Jakarta: Salemba Teknika. 2002. p.74.

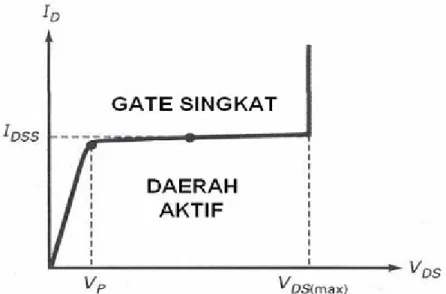

Daerah aktif sebuah JFET adalah antara VP dan VDS(max), seperti terlihat pada gambar 2.11. yang menunjukkan grafik arus drain ID terhadap sumber tegangan drainVDS untuk kondisi drain terhubung singkat.

Gambar 2.11. Grafik arus gate-drain dihubung singkat

Sumber: Malvino, Albert Paul. Prinsip-Prinsip Elektronika. (Alb. Joko Santoso). Jakarta: Salemba Teknika. 2003. p.428.

Dari grafik terlihat bagaimana arus drain naik secara cepat dan kemudian hampir menjadi horisontal ketika VDS lebih besar daripada VP. Tegangan minimum VP (tegangan minimum pada daerah aktif) juga disebut tegangan pinch-off, dan tegangan maksimum VDS(max) (tegangan maksimum pada daerah aktif) disebut dengan tegangan breakdown. Di antara tegangan pinch-off dan breakdown, JFET seperti sebuah sumber arus yang besarnya mendekati IDSS ketika VGS = 0.

Arus drain menjadi hampir konstan karena ketika VDS naik, lapisan deplesi akan mengembang. Ketika VDS = VP, lapisan deplesi hampir menyentuhnya. Kanal penghubung yang sempit akan memutuskan atau mencegah kenaikan arus. Inilah sebabnya mengapa arus memiliki batas atas IDSS. IDSS menunjukkan drain arus ke sumber dengan gate yang dihubungsingkatkan. Ini adalah arus drain maksimum yang dapat dihasilkan sebuah JFET.

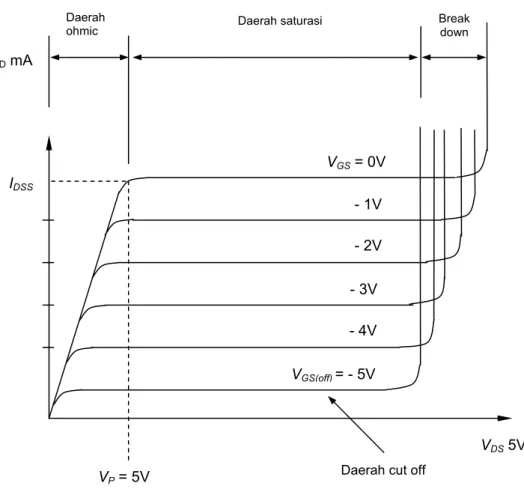

2.2.3. Daerah Operasi

Tegangan pinch-off (VP) memisahkan dua daerah operasi utama JFET. Seperti yang terlihat pada kurva karakteristik drain pada gambar 2.12. Setelah VP tercapai VDS dan resistansi kanal bertambah dengan laju yang sama. Karena ID mendekati konstan dengan bertambahnya VDS. Daerah operasi antara VP dan VBR (tegangan breakdown) atau daerah yang hampir horizontal adalah daerah saturasi

atau daerah aktif atau daerah arus konstan atau daerah linear amplification. Sedangkan bagian yang hampir vertikal pada kurva drain di bawah pinch-off dinamakan daerah ohmic atau daerah voltage-controlled resistance.

Ketika beroperasi pada daerah ohmic, sebuah JFET akan ekuivalen dengan sebuah resistor dengan sebuah nilai yang mendekati:

DSS P DS I V R = (2.1)

RDS disebut dengan hambatan ohmic JFET, dimana hambatan ohmic adalah pembagian tegangan dengan arus pada daerah ohmic. Pada daerah ohmic, JFET juga sering digunakan sebagai variabel resistor, yaitu:

2 ) 1 ( GS P o d V V r r − = (2.2)

dimana ro adalah resistansi saat VGS = 0 V

Gambar 2.12. Kurva karakteristik drain dari JFET

Sumber: Widodo, Thomas Sri. Elektronika Dasar. Jakarta: Salemba Teknika. 2002. p.75.

Daerah

ohmic Daerah saturasi Break down

VGS(off)= - 5V - 4V - 3V - 2V - 1V VGS= 0V

VP = 5V Daerah cut off

VDS 5V IDSS

Pada saat gate dan source dihubung singkat (VGS = 0 V) ID mencapai nilai maksimumnya di IDSS (shorted gate drain current). Jika VGS makin negatif, maka ID makin turun. Nilai VGS yang menyebabkan ID mendekati nol disebut VGS(off) (tegangan cut-off gate source). Nilai VGS(off) sama dengan nilai VP mutlak. Misalnya jika VGS(off) = –5V, maka VP = 5V. Hal ini terjadi karena kedua tegangan akan memiliki besar yang sama karena kedua nilai tersebut adalah nilai ketika lapisan deplesi tercapai atau hampir tercapai. Dalam bentuk persamaan:

|VGS(off)| = VP (2.3)

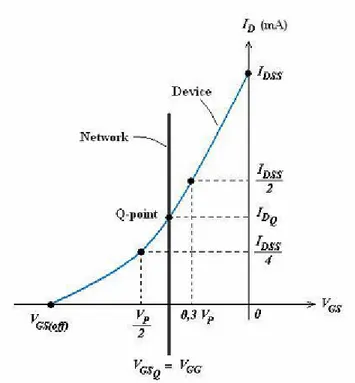

2.2.4. Karakteristik Transfer

Karakteristik transfer sebuah JFET merupakan hubungan antara ID terhadap VGS yang membentuk sebuah kurva karakteristik transfer. Karakteristik transfer JFET dinyatakan dengan persamaan Shockley, sebagai berikut:

2 ) ( 1 − = off GS GS DSS D V V I I (2.4) untuk VGS < VGS(off)

dengan IDSS = arus drain dengan gate terhubung singkat VGS = tegangan gate-source

VGS(off) = tegangan cut-off gate-source

Hubungan antara ID dan VGS untuk suatu JFET dapat digambarkan dengan kurva karakteristik transfer seperti yang terlihat pada gambar 2.13.

Gambar 2.13. Kurva karakteristik transfer JFET

Sumber: Malvino, Albert Paul. Prinsip-Prinsip Elektronika. (Alb. Joko Santoso). Jakarta: Salemba Teknika. 2003. p.431.

Dari persamaan Shockley yang telah disebutkan diatas, karakteristik transfer dapat diturunkan menjadi persamaan:

− = DSS D off GS GS I I V V ( ) 1 (2.5)

Penggunaan persamaan Shockley dan persamaan turunannya, akan lebih memperjelas hubungan antara nilai ID dan VGS.

Dari persamaan (2.4): pada saat VGS = 0 V, maka

(

)

2 2 ) ( 0 1 0 1 = − − = DSS off GS DSS D I V I I DSS D I I = (2.6)pada saat VGS = VGS(off), maka

(

)

2 2 ) ( ) ( 1 1 1 = − − = DSS off GS off GS DSS D V I V I I A ID = 0 (2.7)pada saat VGS = 0.5 VGS(off), maka

2 2 ) ( ) ( 2 1 1 2 1 − = − = DSS off GS off GS DSS D I V V I I

( )

1 2 2 DSS( )

1 4 DSS D I I I = = 4 DSS D I I = (2.8) Dari persamaan (2.5): pada saat ID = ½IDSS, maka(

1 0.5)

(

0.293)

2 1 ( ) ( ) ) ( GSoff GSoff DSS DSS off GS GS V V I I V V = − = − = ) ( 3 . 0 GS off GS V V = (2.9)Hubungan antara nilai ID dan VGS dari persamaan-persamaan yang sudah disebutkan diatas, dapat mempermudah dalam perhitungan, terutama bila menggunakan pendekatan grafik.

2.2.5. Pembiasan JFET

Persamaan Shockley, seperti yang sudah dijelaskan sebelumnya, masih tetap digunakan dalam perhitungan bias. Sedangkan rumus dasar yang digunakan pada analisa DC dalam semua rangkaian bias dan rangkaian penguat JFET adalah sebagai berikut:

IG = 0 A (2.10)

ID = IS (2.11)

JFET dapat dibiaskan pada daerah ohmic maupun pada daerah aktif. Ketika dibiaskan pada daerah ohmic, JFET akan ekuivalen dengan hambatan. Sedangkan ketika dibiaskan pada daerah aktif, JFET akan ekuivalen dengan sumber arus. Pembiasan pada daerah ohmic adalah bias tetap (fixed bias), sedangkan pembiasan pada daerah aktif adalah bias sendiri (self bias), bias pembagi-tegangan (voltage-divider bias), dan bias source dua-catu (two-supply source bias).

2.2.5.1. Bias tetap (fixed bias)

Bias tetap (fixed bias) adalah terjadinya tegangan gate negatif yang diberikan ke gate melalui resistor pembias. Pada rangkaian bias tetap diperlukan dua supply dc agar transistor bisa bekerja. Gambar 2.14. menunjukkan konfigurasi rangkaian bias tetap.

Gambar 2.14. Rangkaian bias tetap (fixed bias)

Sumber: Boylestad, Robert, and Louis Nashelky. Electronic Devices And Circuit Theory. 9th ed. New Jersey: Pearson Prentice-Hall, Inc. 2006. p.405.

Dengan menggunakan analisa DC, maka kapasitor C1 dan C2 dianggap sebagai “open circuit”. Rangkaian pengganti bias tetap untuk analisa DC ditunjukkan pada gambar 2.15.

Gambar 2.15. Rangkaian pengganti DC bias tetap

Tegangan gate negatif -VGG diberikan ke gate melalui resistor pembias RG. Karena tidak ada arus gate (IG = 0 A), maka tidak ada penurunan tegangan pada RG. Nilai VGS adalah sama dengan VGG

VGS = VGG (2.12)

Tegangan gate mengatur arus drain sehingga lebih kecil daripada IDSS. Ketika arus drain melalui RD, akan mengatur tegangan drain sebesar:

VDS = VDD - ID RD (2.13)

Dari gambar 2.15. diatas diketahui juga bahwa tidak ada tegangan pada terminal source (VS = 0 V). Tegangan drain dan source didefinisikan sebagai:

VDS = VD – VS = VD – 0

VD = VDS (2.14)

Sedangkan tegangan gate dan source didefinisikan sebagai: VGS = VG – VS = VG – 0

VG = VGS (2.15)

Analisa bias tetap, selain dari berbagai persamaan yang sudah disebutkan diatas (pendekatan analisa rangkaian) juga dapat dilakukan dengan menggunakan pendekatan grafis, seperti yang ditunjukkan pada gambar 2.16.

Gambar 2.16. Pendekatan grafis dari bias tetap

Sumber: Boylestad, Robert, and Louis Nashelky. Electronic Devices And Circuit Theory. 9th ed. New Jersey: Pearson Prentice-Hall, Inc. 2006. p.406.

Dari gambar 2.16. diatas dapat dilihat bahwa nilai VGSQ sama dengan nilai VGG, yang sesuai dengan persamaan (2.12), dan membentuk garis kerja (network line) secara vertikal. Titik kerja (Q-point) diperoleh dari perpotongan antara garis kerja dengan kurva karakteristik (device cueve). Setelah titik kerja diketahui, maka nilai IDQ juga dapat diketahui dengan menarik garis lurus secara horisontal ke kanan.

Karena VGS(off) dan IDSS mempunyai suatu rentang nilai, maka bias gate ini tidak memberikan titik kerja Q yang stabil. Karena ketidakstabilan inilah maka bias gate jarang sekali digunakan. Meskipun tidak sesuai untuk pembiasan pada daerah aktif, bias gate sangat baik untuk pembiasan pada daerah ohmic karena kestabilan titik Q tidak menjadi masalah.

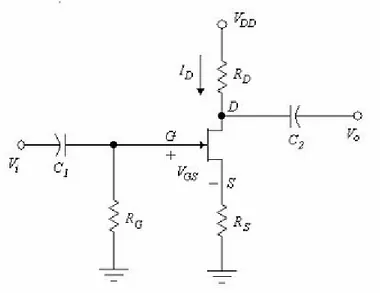

2.2.5.2. Bias sendiri (self bias)

Berbeda dengan rangkaian bias tetap (fixed-bias) yang membutuhkan dua supply tegangan DC, bias sendiri (self bias) hanya menggunakan satu supply tegangan DC. Rangkaian bias sendiri ditunjukkan pada gambar 2.17.

Gambar 2.17. Rangkaian bias sendiri (self bias)

Sumber: Boylestad, Robert, and Louis Nashelky. Electronic Devices And Circuit Theory. 9th ed. New Jersey: Pearson Prentice-Hall, Inc. 2006. p.409.

Dengan menggunakan analisa DC, maka kapasitor C1 dan C2 dianggap sebagai “open circuit”. Rangkaian pengganti bias sendiri untuk analisa DC ditunjukkan pada gambar 2.18.

Gambar 2.18. Rangkaian pengganti DC bias sendiri

Karena tidak ada arus gate (IG = 0 A), maka arus source sama dengan arus drain (IS = ID) dan tidak ada penurunan tegangan pada RG.

VG = 0 V (2.16)

Arus drain mengalir melalui resistor source RS, tegangan yang muncul antara source dan ground dirumuskan dengan:

VRS = IS RS = ID RS (2.17) Dengan menggunakan Hukum Tegangan Kirchoff sesuai loop tertutup pada gambar 2.18. didapatkan: VG = VGS + VRS = VGS + IDRS = 0 VGS = VG – IDRS = 0 – IDRS = – IDRS maka: VGS = – IDRS (2.18) S GS D R V I = − (2.19)

Hal tersebut menyatakan bahwa tegangan gate-source sama dengan negatif dari tegangan yang melalui resistor source. Pada dasarnya rangkaian akan membuat bias sendiri dengan menggunakan tegangan yang melalui RS ke gate bias balik (reverse bias).

Nilai VDS dapat ditentukan dengan menggunakan Hukum Tegangan Kirchoff sesuai loop terbuka pada gambar 2.18. didapatkan:

VRS + VDS + VRD – VDD = 0

VDS = VDD – VRS – VRD = VDD – ISRS – IDRD karena ID = IS,

maka:

VDS = VDD – ID (RD + RS) (2.20) Nilai dari VS dan VD ditentukan sebagai berikut:

VS = IDRS (2.21)

VD = VDS + VS= VDD – VRD = VDD - IDRD (2.22) Perhitungan secara matematis dapat dilakukan pada penyelesaian bias sendiri. Dengan melakukan substitusi antara persamaan (2.19) dengan persamaan Shockley (2.4), dan didapatkan:

2 ) ( 1 − = − off GS GS DSS S GS V V I R V

karena |VGS(off)| = VP, maka:

2 1 + = − P GS DSS S GS V V I R V

+ + = − 1 2 22 P GS P GS DSS S GS V V V V I R V

kedua sisi dari persamaan diatas dikalikan dengan RS, maka:

2 2 2 GS P S DSS GS P S DSS S DSS GS V V R I V V R I R I V = + + − 0 1 2 2 2 + = + + GS DSS S P S DSS GS P S DSS V I R V R I V V R I (2.23) Persamaan diatas identik dengan persamaan kuadrat ax2 + bx + c = 0, dimana: 2 P S DSS V R I a = = 2 +1 P S DSS V R I b c = IDSS RS (2.24)

dengan penyelesaiannya adalah dengan rumus abc, sebagai berikut: a ac b b VGS n channel 2 4 2 − + − = − (2.25) a ac b b VGS p channel 2 4 2 − − + = − (2.26)

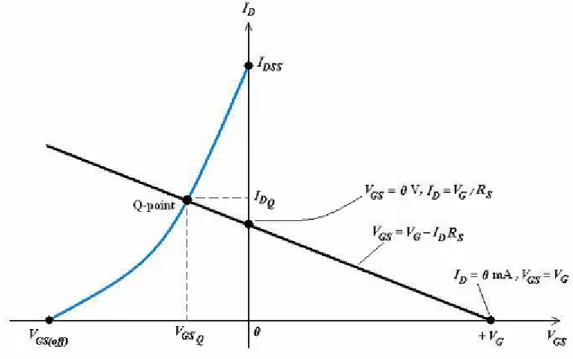

Analisa bias sendiri, selain dari berbagai persamaan yang sudah disebutkan diatas (pendekatan matematis), juga dapat dilakukan dengan menggunakan pendekatan grafis, seperti yang ditunjukkan pada gambar 2.19

Gambar 2.19. Pendekatan grafis dari bias sendiri

Sumber: Boylestad, Robert, and Louis Nashelky. Electronic Devices And Circuit Theory. 9th ed. New Jersey: Pearson Prentice-Hall, Inc. 2006. p.411.

Pada gambar 2.19. diatas, garis kerja (network line) dibuat dengan menetapkan dua buah titik. Titik pertama didapat pada saat nilai ID = 0 A. Sedangkan titik kedua didapat dengan menetapkan nilai tertentu pada VGS atau ID. Diambil yang paling mudah, yaitu pada saat ID = IDSS /2. Nilai VGS pada saat ID = IDSS /2 adalah substitusi dari persamaan VGS = – IDRS yaitu VGS = – IDSSRS /2. Titik kerja (Q-point) diperoleh dari perpotongan antara garis kerja dengan kurva karakteristik (device cueve). Setelah titik kerja diketahui, maka nilai VGSQ dan IDQ juga dapat diketahui.

Titik Q dari bias sendiri (self bias) tidak sestabil daripada bias pembagi-tegangan maupun bias source dua-catu. Oleh sebab itu, bias sendiri (self bias) biasanya digunakan hanya pada penguat sinyal kecil.

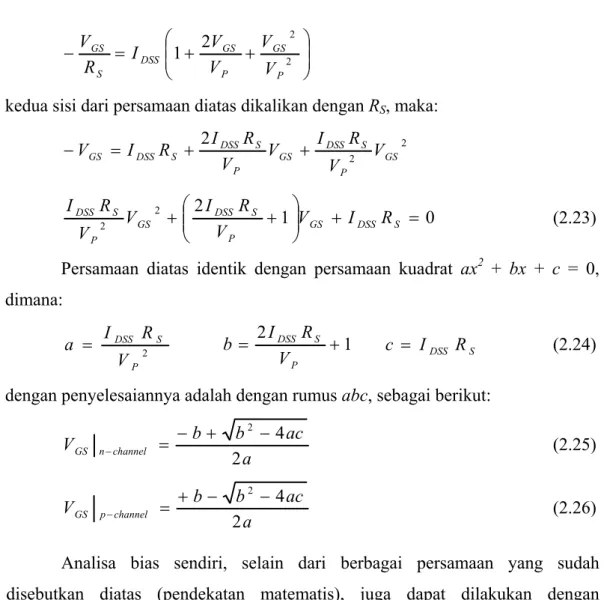

2.2.5.3. Bias pembagi-tegangan (voltage-divider bias)

Bias pembagi tegangan (voltage-divider bias) adalah terjadinya tegangan gate yang merupakan hasil pembagian tegangan melalui resistor source. Gambar 2.20. menunjukkan rangkaian bias pembagi-tegangan.

Gambar 2.20. Rangkaian bias pembagi-tegangan (voltage-divider bias) Sumber: Boylestad, Robert, and Louis Nashelky. Electronic Devices And Circuit Theory. 9th ed. New Jersey: Pearson Prentice-Hall, Inc. 2006. p.415.

Dengan menggunakan analisa DC, maka kapasitor C1, C2 dan CS dianggap sebagai “open circuit”. Rangkaian pengganti bias pembagi-tegangan untuk analisa DC ditunjukkan pada gambar 2.21.

Gambar 2.21. Rangkaian pengganti DC bias pembagi-tegangan

Perhitungan dari rangkaian bias pembagi-tegangan hampir sama dengan rangkaian bias sendiri. Yang membedakan hanyalah bila pada bias sendiri tidak ada penurunan tegangan pada RG (VG = 0 V), maka pada bias pembagi-tegangan terdapat nilai tegangan VG (VG > 0 V).

Analisa pada bias pembagi-tegangan dimulai dengan menentukan terlebih dahulu nilai VG, menggunakan rumus pembagi-tegangan, sebagai berikut:

2 1 2 R R R V VG DD + = (2.27)

Pembagi tegangan menghasilkan tegangan gate yang merupakan bagian dari tegangan catu. Dengan mengurangi tegangan gate-source, kita memperoleh tegangan yang melalui resistor source:

VRS = VG – VGS VGS = VG – VRS = VG – ISRS = VG – IDRS S GS G D R V V I = − (2.28)

Nilai VDS dapat ditentukan dengan menggunakan Hukum Tegangan Kirchoff sesuai loop terbuka pada gambar 2.21. didapatkan:

VRS + VDS + VRD – VDD = 0

karena ID = IS, maka:

VDS = VDD – ID (RD + RS) (2.29) Nilai dari VS dan VD ditentukan sebagai berikut:

VS = IDRS (2.30)

VD = VDS + VS= VDD – VRD = VDD - IDRD (2.31) Perhitungan secara matematis dapat dilakukan pada penyelesaian bias pembagi tegangan. Dengan melakukan substitusi antara persamaan (2.28) dengan persamaan Shockley (2.4), dan didapatkan:

2 ) ( 1 − = − off GS GS DSS S GS G V V I R V V

karena |VGS(off)| = VP, maka:

2 1 + = − P GS DSS S GS G V V I R V V + + = − 2 2 2 1 P GS P GS DSS S GS G V V V V I R V V

kedua sisi dari persamaan diatas dikalikan dengan RS, maka:

2 2 2 GS P S DSS GS P S DSS S DSS GS G V V R I V V R I R I V V − = + + 0 1 2 2 2 + − = + + GS DSS S G P S DSS GS P S DSS V I R V V R I V V R I (2.32) Persamaan diatas identik dengan persamaan kuadrat ax2 + bx + c = 0, dimana: 2 P S DSS V R I a = = 2 +1 P S DSS V R I b c = IDSS RS − VG (2.33) dengan penyelesaiannya adalah dengan rumus abc, sebagai berikut:

a ac b b VGS n channel 2 4 2 − + − = − (2.34) a ac b b VGS p channel 2 4 2 − − + = − (2.35)

Analisa bias pembagi-tegangan, selain dari berbagai persamaan yang sudah disebutkan diatas (pendekatan matematis), juga dapat dilakukan dengan menggunakan pendekatan grafis, seperti yang ditunjukkan pada gambar 2.22.

Gambar 2.22. Pendekatan grafis dari bias pembagi tegangan

Sumber: Boylestad, Robert, and Louis Nashelky. Electronic Devices And Circuit Theory. 9th ed. New Jersey: Pearson Prentice-Hall, Inc. 2006. p.416.

Pada gambar 2.22. diatas, garis kerja (network line) dibuat dengan menetapkan dua buah titik. Penetapan dua buah titik ini berdasarkan persamaan VGS = VG – IDRS. Titik pertama didapat pada saat nilai ID = 0 A, maka VGS = VG. Sedangkan titik kedua didapat pada saat VGS = 0 V, maka ID = VG /RS. Titik kerja (Q-point) diperoleh dari perpotongan antara garis kerja dengan kurva karakteristik (device curve). Setelah titik kerja diketahui, maka nilai VGSQ dan IDQ juga dapat diketahui.

Ketika tegangan gate besar, tegangan gate itu dapat memberikan variasi VGS dari satu JFET terhadap lainnya. Idealnya arus drain sama dengan tegangan gate dibagi dengan hambatan source. Sebagai hasilnya, arus drain hampir konstan untuk JFET apapun. Untuk sebuah penguat, titik Q harus berada pada daerah aktif. Hal ini berarti bahwa VDS harus lebih besar daripada IDRDS (daerah ohmic) dan lebih kecil dari VDD (cutoff). Ketika tegangan catu yang besar tersedia, bias pembagi-tegangan dapat mengatur titik Q yang stabil.

2.2.5.4. Bias source dua-catu (two-supply source bias)

Bias source dua-catu (two-supply source bias) merupakan modifikasi dari rangkaian bias tetap dan rangkaian bias sendiri. Secara konfigurasi rangkaian, bias source dua-catu hampir sama dengan bias sendiri, perbedaannya adalah adanya dua supply tegangan dc yang digunakan pada rangkaian bias ini. Sedangkan perbedaan dengan rangkaian bias tetap yaitu bila pada rangkaian bias tetap menggunakan dua supply tegangan dc yaitu VDD dan VGG, maka pada rangkaian bias source dua-catu, supply tegangan dc yang digunakan adalah VDD dan VSS. Rangkaian bias source dua-catu ditunjukkan oleh gambar 2.23.

Gambar 2.23. Rangkaian bias source dua-catu (two-supply source bias) Sumber: Malvino, Albert Paul. Prinsip-Prinsip Elektronika. (Alb. Joko Santoso). Jakarta: Salemba Teknika. 2003. p.436.

Dari rangkaian diatas, dapat dibuat rangkaian pengganti untuk analisa DC, seperti yang ditunjukkan pada gambar 2.24.

Dengan menggunakan Hukum Tegangan Kirchoff sesuai loop tertutup pada gambar 2.24. didapatkan:

– VGS – VRS + VSS = 0 – VGS – ISRS + VSS = 0 VGS = VSS – ISRS karena IS = ID, maka: VGS = VSS – IDRS (2.36) S GS SS D R V V I = − (2.37)

Nilai VDS dapat ditentukan dengan menggunakan Hukum Tegangan Kirchoff sesuai loop terbuka pada gambar 2.24. didapatkan:

– VSS + VRS + VDS + VRD – VDD = 0 – VSS + ISRS + VDS + IDRD – VDD = 0 karena IS = ID, maka:

VDS = VDD + VSS – ID (RD + RS) (2.38) Analisa bias source dua-catu, selain dari berbagai persamaan yang sudah disebutkan diatas (pendekatan matematis), juga dapat dilakukan dengan menggunakan pendekatan grafis, seperti yang ditunjukkan pada gambar 2.25

.

Pendekatan grafis dari bias source dua-catu hampir sama dengan pendekatan grafis dari bias pembagi-tegangan, bedanya hanyalah tidak terdapatnya nilai VG, dan adanya tegangan supply source (VSS). Pada gambar 2.25. diatas, garis kerja (network line) dibuat dengan menetapkan dua buah titik. Penetapan dua buah titik ini berdasarkan persamaan VGS = VSS – IDRS. Titik pertama didapat pada saat nilai ID = 0 A, maka VGS = VSS. Sedangkan titik kedua didapat pada saat VGS = 0 V, maka ID = VSS /RS. Titik kerja (Q-point) diperoleh dari perpotongan antara garis kerja dengan kurva karakteristik (device curve). Setelah titik kerja diketahui, maka nilai VGSQ dan IDQ juga dapat diketahui.

Bias source dua-catu ini digunakan untuk menghasilkan variasi VGS dengan membuat VSS jauh lebih besar daripada VGS. Idealnya, arus drain sama dengan tegangan catu source dibagi dengan hambatan source. Dalam kasus ini, arus drain hampir konstan dalam penggantian JFET dan perubahan suhu.

2.2.5.5. Perbandingan Kestabilan Bias JFET

Umumnya pada lembar spesifikasi data JFET, terdapat nilai IDSS dan VGS(off) maksimum serta IDSSdan VGS(off) minimum. Antara satu komponen dengan komponen yang lain dari satu tipe JFET yang sama, bisa mempunyai nilai IDSSdan VGS(off) yang berbeda. Hal ini disebabkan karena tidak ada suatu komponen yang benar-benar identik antara satu dengan yang lain. Oleh karena itulah maka dalam lembar spesifikasi data terdapat nilai maksimum dan nilai minimum. Hal itu berarti bahwa perbedaan antara satu komponen dengan komponen lain dalam satu tipe JFET, berada dalam range dari nilai minimum hingga nilai maksimum.

Pembiasan JFET, seperti yang sudah dijelaskan sebelumnya, dapat diperbandingkan tingkat kestabilannya dilihat dari titik kerjanya (Q-point) pada grafik kurva karakteristik transfer. Pembiasan JFET disini yang akan dibandingkan adalah bias tetap, bias sendiri dan bias pembagi tegangan. Bias source dua-catu tidak dibandingkan karena mempunyai grafik penentuan titik kerja yang sama dengan bias pembagi tegangan.

Dalam perbandingan ini digunakan spesifikasi dari JFET yang sama, dan diasumsikan mempunyai nilai IDSS dan VGS(off) yang sama. Ditentukan juga titik kerja (Q-point) yang sama dalam kurva karakteristik transfer. Kemudian dibuat

kurva karakteristik transfer lain yang akan menghasilkan titik kerja alternatif ( Q’-point) yang berfungsi untuk melihat perubahan besaran titik kerja dalam nilai ∆ID. Gambar 2.26. menunjukkan perbandingan kestabilan bias JFET.

Gambar 2.26. Grafik perbandingan kestabilan bias JFET

Sumber: Floyd, Thomas L. Electronic Devices. 4th ed. New Jersey: Prentice Hall International, Inc. 1996. p.245.

Dari gambar 2.26. diatas dapat dilihat bahwa perubahan besaran titik kerja dalam nilai ∆ID terkecil adalah dari konfigurasi bias pembagi tegangan. Sedangkan perubahan besaran titik kerja dalam nilai ∆ID yang terbesar adalah konfigurasi bias tetap. Hal ini menunjukkan bahwa konfigurasi bias pembagi tegangan mempunyai tingkat kestabilan titik kerja yang paling baik diantara ketiga konfigurasi bias yang lainnya karena mempunyai perubahan besaran titik kerja yang paling kecil.

2.3. Model FET Sinyal-Kecil (Small-Signal FET)

Konsep dari analisa sinyal-kecil FET adalah untuk membuat rangkaian penguat sinyal-kecil yang menghasilkan penguatan tegangan (voltage gain) dengan impedansi masukan yang tinggi. Transistor bipolar bekerja dengan mengendalikan arus keluaran yang besar (collector) dari arus masukan yang lebih

kecil (base), sedangkan FET bekerja dengan mengendalikan arus keluaran (drain) dari tegangan masukan yang kecil (gate-source).

Rangkaian pengganti AC FET pada dasarnya lebih sederhana dibandingkan dengan pada transistor bipolar. Bila pada transistor bipolar mempunyai penguatan arus (current gain = β), maka FET mempunyai transkonduktansi (gm). Pada saat digunakan sebagai rangkaian penguat, sebenarnya transistor bipolar dan FET mempunyai fungsi yang sama. Tetapi karena mempunyai resistansi masukan yang tinggi, FET lebih baik digunakan untuk beberapa aplikasi tertentu.

FET dapat digunakan untuk aplikasi linear pada rangkaian penguat atau aplikasi digital pada rangkaian logika. FET juga dapat digunakan pada banyak aplikasi frekuensi tinggi serta untuk aplikasi rangkaian penyangga (buffer).

2.3.1. Transkonduktansi (gm)

Untuk melakukan analisa AC dari rangkaian FET, perlu ditentukan terlebih dahulu rangkaian pengganti AC dari rangkaian FET tersebut. Rangkaian pengganti AC yang digunakan ini sama untuk berbagai jenis FET yang ada. Hal yang utama dalam analisa AC rangkaian FET adalah bahwa tegangan AC digunakan pada terminal gate-source untuk mengendalikan arus antara terminal drain-source.

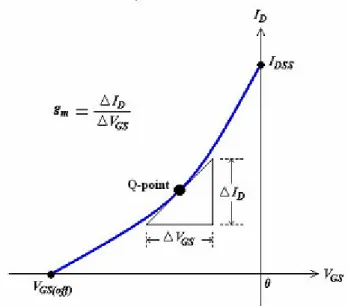

Parameter penting yang terdapat pada FET adalah transkonduktansi (gm), dimana merupakan lekukan dari kurva karakteristik transfer pada titik kerja ( Q-point). Transkonduktansi didefinisikan sebagai arus drain-source AC dibagi dengan tegangan gate-source AC. Transkonduktansi dapat mengindikasikan efektif atau tidaknya tegangan gate-source dalam mengendalikan arus drain. Untuk menganalisis penguat JFET, diperlukan transkonduktansi yang didefinisikan sebagai: gs d m V i g = (2.39)

sedangkan definisi dasar transkonduktansi, pada saat VDS konstan adalah:

GS D m V I x y m g ∆ ∆ = ∆ ∆ = = (2.40)

Persamaan 2.40. diatas digunakan untuk mendefinisikan nilai transkonduktansi (gm) dengan menggunakan pendekatan grafik pada kurva karakteristik transfer, seperti yang ditunjukkan pada gambar 2.27.

Gambar 2.27. Definisi gm menggunakan kurva karakteristik transfer

Sumber: Boylestad, Robert, and Louis Nashelky. Electronic Devices And Circuit Theory. 9th ed. New Jersey: Pearson Prentice-Hall, Inc. 2006. p.466.

Definisi gm dengan menggunakan pendekatan grafik, seperti yang telah dijelaskan diatas, membutuhkan tingkat akurasi yang tinggi karena perubahan dari tiap penempatan titik akan merubah nilai gm. Semakin besar grafik yang digunakan, maka tingkat akurasi akan semakin baik, tetapi hal itu merupakan masalah tersendiri bila harus mendefinisikan gm dalam jumlah yang banyak. Karena keterbatasan tersebut, maka dapat digunakan pendekatan matematis, dimana dalam mendefinisikan gm tidak perlu lagi menggambar grafik terlebih dulu, tetapi hanya menggunakan persamaan-persamaan matematis yang relatif lebih sederhana dibandingkan dengan pendekatan grafik.

Nilai ID seperti yang sudah dijelaskan sebelumnya pada persamaan Sockley, disubstitusikan dalam persamaan (2.40) dan kemudian diturunkan terhadap VGS, dan didapatkan:

− = = 2 ) ( 1 off GS GS DSS GS GS D m V V I dV d dV dI g

− − = − − = ) ( ) ( ) ( ) ( 1 2 1 1 2 off GS GS off GS DSS off GS off GS GS DSS m V V V I V V V I g

karena VGS(off) bernilai negatif untuk n-channel JFET, maka akan dihilangkan tanda negatif yang ada dengan memberikan tanda nilai mutlak pada persamaan diatas, didapatkan: − = ) ( ) ( 1 2 off GS GS off GS DSS m V V V I g (2.41)

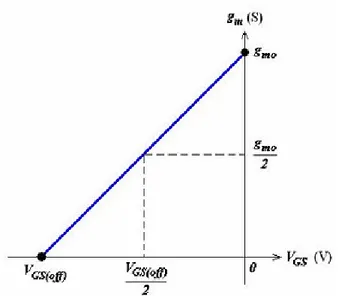

Nilai maksimum transkonduktansi yang terjadi pada saat VGS = 0 V disebut dengan gmo, dan ditentukan dengan persamaan:

) ( 2 off GS DSS mo V I g = (2.42)

dengan mensubstitusikan persamaan (2.42) ke persamaan (2.41) maka: − = ) ( 1 off GS GS mo m V V g g (2.43)

Dari persamaan diatas dapat diketahui hubungan antara gm dengan VGS, dimana pada saat nilai gm = 0, nilai VGS akan sama dengan VGS(off) (VGS maksimum), dan pada saat nilai VGS = 0 V, nilai gm akan sama dengan gm0 (gm maksimum). Maka dapat diketahui pula pada saat gm = ½ gm0, nilai VGS akan sama dengan ½ VGS(off), demikian juga sebaliknya. Gambar 2.28 menunjukkan grafik hubungan antara gm dengan VGS pada saat gm = ½ gm0, VGS = ½ VGS(off).

Gambar 2.28. Grafik hubungan antara gm dengan VGS

Sumber: Boylestad, Robert, and Louis Nashelky. Electronic Devices And Circuit Theory. 9th ed. New Jersey: Pearson Prentice-Hall, Inc. 2006. p.468.

Hubungan antara gm dengan ID, seperti ditunjukkan pada gambar 2.29., dapat ditentukan menggunakan persamaan Shockley, sebagai berikut:

2 ) ( 1 − = off GS GS DSS D V V I I DSS D off GS GS I I V V = − ) ( 1 (2.44)

persamaan (2.44) di atas disubstitusikan ke dalam persamaan (2.43), didapatkan:

DSS D m off GS GS m m I I g V V g g 0 ) ( 0 1 = − = (2.45)

Penggunaan persamaan (2.45) diatas, dapat digunakan untuk lebih memperjelas hubungan antara nilai gm dan ID:

Pada saat ID = IDSS, maka:

0 0 m DSS DSS m m g I I g g = = (2.46)

Pada saat ID = IDSS/2, maka:

0 0 0,707 2 / m DSS DSS m m g I I g g = = (2.47)

0 0 0 0 0,5 2 4 / m m DSS DSS m m g g I I g g = = = (2.48)

Gambar 2.29. Grafik hubungan antara gm dengan ID

Unit mho adalah rasio arus terhadap tegangan. Unit yang ekuivalen dan lebih modern untuk mho disebut siemen (S). Jadi besaran dari gm adalah mho atau siemen (S). Kedua besaran (mho dan siemen) dapat digunakan. Pada lembar spesifikasi data (data sheet), nilai gm disebut sebagai yfs atau gfs, dimana f menunjukkan parameter transfer maju, sedangkan s menunjukkan bahwa transkonduktansi ini terhubung dengan terminal source.

2.3.2. Impedansi FET

FET mempunyai impedansi masukan (Zi) maupun impedansi keluaran (Zo). Impedansi masukan FET yang ada saat ini mempunyai nilai yang cukup besar, yang diasumsikan bahwa terminal masukan dianggap sebagai “open circuit”. Dituliskan dalam persamaan sebagai:

Zi (FET) = ∞Ω (2.49)

Untuk JFET biasanya mempunyai nilai impedansi masukan sebesar 109Ω

(1000 MΩ), sedangkan untuk MOSFET dan MESFET mempunyai nilai impedansi masukan antara 1012Ω sampai 1015Ω.

Pada data sheet, impedansi keluaran FET biasanya disebut sebagai yos atau gos, dengan satuannya adalah µS, dimana o menunjukkan parameter kerja keluaran

dan s menunjukkan bahwa impedansi keluaran terhubung dengan terminal source. Persamaan impedansi keluaran adalah:

os os d o g y r Z (FET)= = 1 = 1 (2.50)

2.3.3. Rangkaian Pengganti AC FET

Setelah membahas tentang perameter-paremeter penting di dalam model sinyal-kecil FET, maka rangkaian pengganti AC FET dapat lebih mudah dibentuk dan dipahami. Rangkaian pengganti AC FET ditunjukkan pada gambar 2.30.

Gambar 2.30. Rangkaian pengganti AC FET

Sumber: Boylestad, Robert, and Louis Nashelky. Electronic Devices And Circuit Theory. 9th ed. New Jersey: Pearson Prentice-Hall, Inc. 2006. p.471.

Dalam rangkaian pengganti AC FET pada gambar 2.30., arus Id yang dikendalikan oleh Vgs termasuk didalam sumber arus gmVgs yang terhubung dari drain ke source. Sumber arus gmVgs mempunyai arah panah yang menunjuk dari drain ke source untuk menentukan perubahan fasa 180° antara tegangan keluaran dan tegangan masukan. Impedansi masukan ditunjukkan oleh rangkaian terbuka (open circuit) pada terminal masukan, dan impedansi keluaran ditunjukkan oleh resistor rd dari drain ke source. Tegangan gate-source dalam rangkaian pengganti AC ini menggunakan simbol Vgs, untuk membedakan dengan analisa DC.

Pada kondisi tertentu dimana pada saat nilai rd besar, rangkaian pengganti AC dapat dibuat lebih sederhana, dengan mengabaikan nilai rd (dianggap sebagai open circuit), yaitu hanya terdiri dari sebuah sumber arus gmVgs yang berfungsi untuk mengendalikan tegangan Vgs dan parameter gm.

2.4. Penguat JFET Tanpa Beban

Operasi penguat JFET menyerupai penguat pada BJT. Perbedaan antara keduanya adalah bila BJT adalah komponen devais terkendali arus, sedangkan FET adalah devais terkendali tegangan. Adapun impedansi masukan penguat FET jauh lebih tinggi dibandingkan penguat BJT. Parameter-parameter penting yang digunakan di dalam rangkaian penguat JFET ini juga hampir sama dengan penguat BJT, yaitu impedansi masukan (Zi), imepdansi keluaran (Zo) serta penguatan tegangan (AV) untuk masing-masing konfigurasi penguat.

Seperti pada penguat BJT yang dibedakan dalam tiga konfigurasi, yaitu common emmiter (CE), common collector (CC), dan common base (CB). Penguat FET juga dibedakan dalam tiga konfigurasi, yaitu penguat common source (CS), penguat common drain (CD), dan penguat common gate (CG).

2.4.1. Penguat Common Source (CS)

Rangkaian penguat common source merupakan konfigurasi rangkaian penguat JFET yang paling banyak digunakan untuk berbagai aplikasi. Penggunaan rangkaian penguat common source ini populer digunakan dan dibedakan berdasarkan konfigurasi rangkaian biasnya, yaitu common source konfigurasi bias tetap, common source konfigurasi bias sendiri, dan common source konfigurasi bias pembagi tegangan.

2.4.1.1. Common Source Konfigurasi Bias Tetap

Rangkaian penguat common source konfigurasi bias tetap menggunakan dua buah supply DC seperti halnya rangkaian bias tetap. Pada rangkaian penguat ini menggunakan dua buah kapasitor penggandeng C1 dan C2 yang berfungsi sebagai pemisah dari sinyal dan beban DC. Pada analisa AC, kedua kapasitor C1 dan C2 bekerja sebagai hubung singkat (short-circuit). Rangkaian penguat common source konfigurasi bias tetap ditunjukkan pada gambar 2.31.

Gambar 2.31. Penguat common source konfigurasi bias tetap

Sumber: Boylestad, Robert, and Louis Nashelky. Electronic Devices And Circuit Theory. 9th ed. New Jersey: Pearson Prentice-Hall, Inc. 2006. p.472.

Seperti yang sudah dijelaskan sebelumnya, parameter gm dan rd dapat ditentukan dari persamaan bias DC, lembar spesifikasi data (data sheet), dan kurva karakteristik transfer. Rangkaian pengganti untuk analisa AC dari rangkaian diatas ditunjukkan pada gambar 2.32.

Gambar 2.32. Rangkaian pengganti AC common source konfigurasi bias tetap Sumber: Boylestad, Robert, and Louis Nashelky. Electronic Devices And Circuit Theory. 9th ed. New Jersey: Pearson Prentice-Hall, Inc. 2006. p.473.

Pada gambar 2.31. di atas, kapasitor C1 dan C2 dalam kondisi hubung singkat (short circuit), karena reaktansi XC = 1/(2πfC) berharga sangat kecil dibandingkan dengan impedansi masukan maupun impedansi keluaran. Sedangkan supply DC VGG dan VDD diset pada nilai 0 V sehingga juga menjadi kondisi hubung singkat. Polaritas Vgs ditentukan berdasarkan arah panah dari sumber arus gmVgs. Jika Vgs berharga negatif, maka arah dari sumber arus adalah

terbalik. Sinyal yang masuk didefinisikan sebagai Vi, dan sinyal keluaran yang melewati RD didefinisikan sebagai Vo.

Karena terminal masukan pada rangkaian pengganti AC dalam kondisi open circuit, maka didapatkan impedansi masukan:

Zi = RG (2.51)

Untuk menentukan Zo, Vi diset pada nilai 0 V dan Vgs ditetapkan nilainya sebesar 0 V. Didapatkan bahwa gmVgs = 0 mA dan sumber arus dapat digantikan menjadi open circuit, seperti ditunjukkan pada gambar 2.33. Didapatkan impedansi keluaran yaitu:

Zo = RD║rd (2.52)

Gambar 2.33. Rangkaian untuk menentukan Zo

Sumber: Boylestad, Robert, and Louis Nashelky. Electronic Devices And Circuit Theory. 9th ed. New Jersey: Pearson Prentice-Hall, Inc. 2006. p.473.

Jika resistansi rd bernilai cukup besar (mencapai 10:1) dibandingkan RD, didapatkan persamaan RD║rd ≈ RD, dengan nilai rd dapat diabaikan. Maka impedansi keluaran (pada kondisi rd ≥ 10RD) adalah:

D o R

Z ≅ (2.53)

Penguatan tegangan (AV) dapat ditentukan dengan terlebih dahulu mendapatkan nilai Vo. Dari gambar 2.32. didapatkan:

Vo = – gmVgs (RD║rd) karena Vgs = Vi maka Vo = – gmVi (RD║rd) dan didapatkan: ) ( D d m i o V g R r V V A = =− (2.54)

D m i o V g R V V A = = − (2.55)

Tanda negatif pada hasil akhir persamaan penguatan tegangan (AV) menunjukkan bahwa terjadi pembalikan fasa sebesar 180° antara tegangan masukan (Vi) dan tegangan keluaran (Vo).

2.4.1.2. Common Source Konfigurasi Bias Sendiri

Seperti sudah dijelaskan pada penjelasan bias JFET. Bila pada rangkaian bias tetap (fixed-bias) membutuhkan dua supply tegangan DC, bias sendiri (self bias) hanya menggunakan satu supply tegangan DC. Rangkaian penguat common source konfigurasi bias sendiri hanya menggunakan satu buah supply DC. Pada rangkaian penguat ini menggunakan dua buah kapasitor penggandeng C1 dan C2 yang berfungsi sebagai pemisah dari sinyal dan beban DC, serta dengan atau tanpa kapasitor CS. Rangkaian penguat common source konfigurasi bias sendiri ditunjukkan pada gambar 2.34.

Gambar 2.34. Penguat common source konfigurasi bias sendiri

Sumber: Boylestad, Robert, and Louis Nashelky. Electronic Devices And Circuit Theory. 9th ed. New Jersey: Pearson Prentice-Hall, Inc. 2006. p.475.

a. Dengan Kapasitor CS

Pada analisa AC dengan menggunakan kapasitor CS, ketiga kapasitor C1, C2 dan CS bekerja sebagai hubung singkat (short-circuit). Karena CS kondisi hubung singkat, maka RS dilewatkan (bypass). Sedangkan supply DC VDD diset

pada nilai 0 V sehingga juga menjadi kondisi hubung singkat. Rangkaian pengganti untuk analisa AC dari rangkaian penguat common source konfigurasi bias sendiri dengan menggunakan kapasitor CS ditunjukkan pada gambar 2.35.

Gambar 2.35. Rangkaian pengganti AC common source konfigurasi bias sendiri dengan menggunakan kapasitor CS

Sumber: Boylestad, Robert, and Louis Nashelky. Electronic Devices And Circuit Theory. 9th ed. New Jersey: Pearson Prentice-Hall, Inc. 2006. p.477.

Karena bentuk dari rangkaian pengganti AC ini sama seperti rangkaian pengganti AC dari penguat common source konfigurasi bias tetap, maka penurunan persamaannya juga sama.

impedansi masukan:

Zi = RG (2.56)

impedansi keluaran yaitu:

Zo = RD║rd (2.57)

impedansi keluaran (pada kondisi rd ≥ 10RD) adalah: D o R Z ≅ (2.58) penguatan tegangan: ) ( D d m i o V g R r V V A = =− (2.59)

penguatan tegangan pada kondisi rd ≥ 10RD, adalah:

D m i o V g R V V A = = − (2.60)

Tanda negatif pada hasil akhir persamaan penguatan tegangan (AV) menunjukkan bahwa terjadi pembalikan fasa sebesar 180° antara tegangan masukan (Vi) dan tegangan keluaran (Vo).

b. Tanpa Kapasitor CS

Bila pada rangkaian penguat sebelumnya dengan menggunakan CS terjadi kondisi dimana CS hubung singkat dan RS dilewatkan (bypass), maka bila rangkaian tanpa menggunakan kapasitor CS, resistor RS menjadi bagian dari rangkaian pengganti AC dan tidak dilewatkan (unbypass). Supply DC VDD diset pada nilai 0 V sehingga menjadi kondisi hubung singkat. Rangkaian pengganti AC common source konfigurasi bias sendiri tanpa menggunakan kapasitor CS ditunjukkan pada gambar 2.36.

Gambar 2.36. Rangkaian pengganti AC common source konfigurasi bias sendiri tanpa menggunakan kapasitor CS

Sumber: Boylestad, Robert, and Louis Nashelky. Electronic Devices And Circuit Theory. 9th ed. New Jersey: Pearson Prentice-Hall, Inc. 2006. p.477.

Karena terminal masukan pada rangkaian pengganti AC dalam kondisi open circuit, maka didapatkan impedansi masukan:

Zi = RG (2.61)

Pada saat Vi = 0 V dan Vo = −IDRD, impedansi keluaran didefinisikan sebagai:

dari gambar 2.36. dengan menggunakan hukum arus Kirchoff, didapatkan Io + ID = gmVgs + Ird Io = gmVgs + Ird – ID D d gs o gs m D d rd gs m o I r V V V g I r V V g I = + − = + + − o D D o o o I R I I V Z = =−

D d o gs d m D d gs d o gs m o I r V V r g I r V r V V g I + − + = − + + = 1 D d D D gs d m o I r R I V r g I − − + = 1 karena Vgs = −(ID + Io)RS maka

(

)

D d D D S o D d m o I r R I R I I r g I + − − + − = 1persamaan diatas dapat diubah menjadi

+ + + − = + + d D d S S m D d S S m o r R r R R g I r R R g I 1 1 d S S m d D d S S m D o r R R g r R r R R g I I + + + + + − = 1 1

maka, impedansi keluaran yaitu:

d S S m d D d S S m D D D o o o r R R g r R r R R g I R I I V Z + + + + + − − = = 1 1 D d D d S S m d S S m o R r R r R R g r R R g Z + + + + + = 1 1 (2.62) pada kondisi rd ≥ 10RD d D d S S m r R r R R g >> + 1 maka + ≅ + + + d S S m d D d S S m r R R g r R r R R g 1 1

impedansi keluaran pada kondisi rd ≥ 10RD, adalah:

Dari gambar 2.36. dengan menggunakan hukum tegangan Kirchoff pada rangkaian masukan, didapatkan:

Vi – Vgs – VRS = 0 Vgs = Vi – IDRS

tegangan pada rddidefinisikan sebagai Vrd = Vo – VRS dan d RS o d rd rd r V V r V I = = −

dengan menggunakan hukum arus Kirchoff, didapatkan: ID = gmVgs + Ird d RS o gs m D r V V V g I = + −

substitusi nilai dari Vgs, Vo, dan VRS, didapatkan:

(

) (

) (

)

d S D D D S D i m D r R I R I R I V g I = − + − − i m d S D S m D g V r R R R g I = + + + 1 d S D S m i m D r R R R g V g I + + + = 1didapatkan tegangan keluaran, yaitu:

d S D S m i D m D D o r R R R g V R g R I V + + + − = − = 1

maka, penguatan tegangan adalah:

d S D S m D m i o V r R R R g R g V V A + + + − = = 1 (2.64)

penguatan tegangan pada kondisi rd ≥ 10RD, adalah:

S m D m i o V R g R g V V A + − = = 1 (2.65)

Tanda negatif pada hasil akhir persamaan penguatan tegangan (AV) menunjukkan bahwa terjadi pembalikan fasa sebesar 180° antara tegangan masukan (Vi) dan tegangan keluaran (Vo).

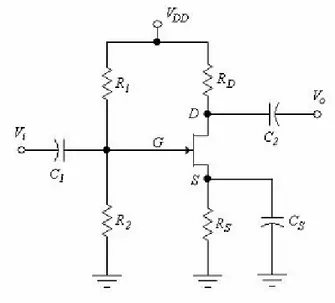

2.4.1.3. Common Source Konfigurasi Bias Pembagi Tegangan

Rangkaian penguat common source konfigurasi bias pembagi tegangan ini identik dengan rangkaian bias pembagi tegangan.. Pada rangkaian penguat ini menggunakan dua buah kapasitor penggandeng C1 dan C2 yang berfungsi sebagai pemisah dari sinyal dan beban DC, serta kapasitor CS yang berfungsi sebagai pelewat (bypass) RS. Rangkaian penguat common source konfigurasi bias pembagi tegangan ditunjukkan pada gambar 2.37.

Gambar 2.37. Penguat common source konfigurasi bias pembagi tegangan Sumber: Boylestad, Robert, and Louis Nashelky. Electronic Devices And Circuit Theory. 9th ed. New Jersey: Pearson Prentice-Hall, Inc. 2006. p.481.

Pada analisa AC, kapasitor penggandeng (coupling) C1, C2 dan kapasitor pelewat (bypass) CS bekerja sebagai hubung singkat (short-circuit). Karena CS kondisi hubung singkat, maka RS dilewatkan (bypass). Sedangkan supply DC VDD diset pada nilai 0 V sehingga juga menjadi kondisi hubung singkat. Oleh karena itu, sinyal digandeng secara langsung ke gate. Jika source dilewatkan langsung ke ground, semua tegangan masukan AC tampak di antara gate dan source. Hal ini akan menghasilkan arus drain AC. Jika arus drain AC mengalir melalui resistor source, akan diperoleh penguatan dan pembalikan tegangan keluaran. Sinyal keluaran ini kemudian digandeng ke resistor beban. Rangkaian pengganti untuk

analisa AC dari rangkaian penguat common source konfigurasi bias pembagi tegangan ditunjukkan pada gambar 2.38.

Gambar 2.38. Rangkaian pengganti AC common source konfigurasi bias pembagi tegangan

Sumber: Boylestad, Robert, and Louis Nashelky. Electronic Devices And Circuit Theory. 9th ed. New Jersey: Pearson Prentice-Hall, Inc. 2006. p.481.

Karena terminal masukan pada rangkaian pengganti AC dalam kondisi open circuit dan R1 dan R2 dalam keadaan paralel, maka didapatkan impedansi masukan:

Zi = R1║ R2 (2.66)

Untuk menentukan Zo, Vi diset pada nilai 0 V dan Vgs serta gmVgs ditetapkan nilainya sebesar 0 V. Didapatkan impedansi keluaran yaitu:

Zo = RD║rd (2.67)

impedansi keluaran pada kondisi rd ≥ 10RD, adalah:

Zo = RD (2.68)

untuk menentukan penguatan tegangan, harus diketahui terlebih dahulu nilai Vi dan Vo, sebagai berikut:

Vi = Vgs

Vo = – gmVgs(RD║rd) penguatan tegangan, yaitu:

(

)

gs d D gs m i o V V r R V g V V A = = − ) ( D d m i o V g R r V V A = = − (2.69)D m i o V g R V V A = = − (2.70)

Tanda negatif pada hasil akhir persamaan penguatan tegangan (AV) menunjukkan bahwa terjadi pembalikan fasa sebesar 180° antara tegangan masukan (Vi) dan tegangan keluaran (Vo).

2.4.2. Penguat Common Drain (CD)

Rangkain penguat common drain disebut juga sebagai konfigurasi rangkaian pengikut source (source follower). Seperti pengikut emmiter pada transistor BJT, pengikut source memiliki penguatan tegangan lebih rendah dari 1. Keuntungan utama dari pengikut source adalah impedansi masukan yang tinggi. Rangkain penguat common drain ditunjukkan pada gambar 2.39.

Gambar 2.39. Penguat common drain (source follower)

Sumber: Boylestad, Robert, and Louis Nashelky. Electronic Devices And Circuit Theory. 9th ed. New Jersey: Pearson Prentice-Hall, Inc. 2006. p.482.

Dari gambar 2.39. dapat dilihat bahwa keluaran terletak pada terminal source. Hal ini yang membedakan dengan rangkaian penguat common source. Pada analisa AC, supply DC VDD pada kondisi hubung singkat (short circuit), dan terminal drain terhubung dengan ground. Gambar 2.40. menunjukkan rangkaian pengganti AC dari penguat common drain.

Gambar 2.40. Rangkaian pengganti AC common drain

Sumber: Boylestad, Robert, and Louis Nashelky. Electronic Devices And Circuit Theory. 9th ed. New Jersey: Pearson Prentice-Hall, Inc. 2006. p.483.

Dari gambar 2.40. diatas dapat dilihat bahwa sumber arus bekerja dengan arah yang berlawanan (reversed), sedangkan Vgs tetap ditentukan pada terminal gate dan source. Impedansi masukan didefinisikan sebagai:

Zi = RG (2.71)

Untuk menentukan Zo, Vi diset pada nilai 0 V dan didapatkan bahwa terminal gate terhubung langsung dengan ground. Karena sumber arus bekerja dengan arah yang berlawanan, maka Vo = –Vgs, seperti ditunjukkan pada gambar 2.41.

Gambar 2.41. Rangkaian untuk menentukan Zo

Sumber: Boylestad, Robert, and Louis Nashelky. Electronic Devices And Circuit Theory. 9th ed. New Jersey: Pearson Prentice-Hall, Inc. 2006. p.483.

Menggunakan hukum arus Kirchoff pada node S dari gambar 2.41. diatas, didapatkan: Io + gmVgs = Ird + IRS S o d o gs m o R V r V V g I + = +