Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital

Pengantar Kuliah

TKC305 - Sistem Digital Lanjut

Eko Didik Widianto

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital

Review Kuliah

I

Pembahasan tentang deskripsi, tujuan, sasaran dan

materi kuliah TKC305 Sistem Digital Lanjut. Selain

itu, juga dibahas tentang tata tertib kuliah dan sistem

evaluasi

I

Sebelumnya berkode TSK-505

I

Penjelasan GBPP/SAP TKC305 Sistem Digital Lanjut

IMahasiswa akan belajar tentang desain dan

implementasi rangkaian kombinasional dan

sekuensial yang lebih kompleks menggunakan chip

standar TTL (dan CMOS) dan teknologi device

terprogram (CPLD/FPGA) berbasis Xilinx

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital

Bahasan

Pengantar Perkuliahan

Deskripsi Kuliah

Standar Kompetensi dan Kompetensi Dasar

Buku Acuan

Rencana Perkuliahan

Tata Tertib Kuliah

Sistem Evaluasi

Teknologi CMOS

Pendahuluan

Saklar Transistor

Rangkaian CMOS

Gerbang Logika CMOS

Rangkuman

Teknologi Implementasi Rangkaian Digital

Pendahuluan

Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Pengantar Kuliah

@2011,Eko Didik Widianto Pengantar Kuliah

Deskripsi Kuliah

Standar Kompetensi dan Kompetensi Dasar Buku Acuan Rencana Perkuliahan Tata Tertib Kuliah Sistem Evaluasi Teknologi CMOS Teknologi Implementasi Rangkaian Digital

Bahasan

Pengantar Perkuliahan

Deskripsi Kuliah

Standar Kompetensi dan Kompetensi Dasar

Buku Acuan

Rencana Perkuliahan

Tata Tertib Kuliah

Sistem Evaluasi

Teknologi CMOS

Pendahuluan

Saklar Transistor

Rangkaian CMOS

Gerbang Logika CMOS

Rangkuman

Teknologi Implementasi Rangkaian Digital

Pendahuluan

Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Pengantar Kuliah

@2011,Eko Didik Widianto Pengantar Kuliah

Deskripsi Kuliah

Standar Kompetensi dan Kompetensi Dasar Buku Acuan Rencana Perkuliahan Tata Tertib Kuliah Sistem Evaluasi Teknologi CMOS Teknologi Implementasi Rangkaian Digital

Deskripsi Kuliah

Kredit: 2 SKS Kuliah, 1 SKS Praktikum

Metode pengajaran: tatap muka (2 x 50 menit), presentasi materi dan diskusi,

UTS, UAS, Tugas

Waktu: ±14 Minggu (termasuk UTS dan UAS)

Prasyarat: TSK205 (Sistem Digital)

I

Teknologi implementasi sistem digital: gerbang logika

CMOS, IC standar seri 7400, PLD, FPGA, ASIC dan CAD untuk

mengimplementasikan sistem

I

Desain rangkaian kombinasional: multiplekser, dekoder,

enkoder, kode konverter, komparator dan deskripsi HDLnya

I

Elemen rangkaian sekuensial: latch (SR, D), flip-flop (D, T,

JK), register, shift register, counter/pencacah up/down sinkron

dan asinkron, pencacah lainnya dan deskripsi HDLnya

I

Rangkaian sekuensial sinkron: FSM meliputi diagram, tabel

dan assignment state serta pemilihan flip-flop untuk

implementasi, model Moore, model Mealy, desain FSM dengan

HDL, minimisasi state, contoh implementasi (serial adder,

counter) dan analisisnya

I

Rangkaian sekuensial asinkron: analisis, sintesis, reduksi dan

assignment state serta contoh desainnya

Kuliah TKC305 ini berkomplemen dengan TSK305 (Teknik Mikroprosesor),

TSK307 (Organisasi Komputer) dan TSK507 (Sistem Embedded).

Pengantar Kuliah

@2011,Eko Didik Widianto Pengantar Kuliah

Deskripsi Kuliah

Standar Kompetensi dan Kompetensi Dasar

Buku Acuan Rencana Perkuliahan Tata Tertib Kuliah Sistem Evaluasi Teknologi CMOS Teknologi Implementasi Rangkaian Digital

Bahasan

Pengantar Perkuliahan

Deskripsi Kuliah

Standar Kompetensi dan Kompetensi Dasar

Buku Acuan

Rencana Perkuliahan

Tata Tertib Kuliah

Sistem Evaluasi

Teknologi CMOS

Pendahuluan

Saklar Transistor

Rangkaian CMOS

Gerbang Logika CMOS

Rangkuman

Teknologi Implementasi Rangkaian Digital

Pendahuluan

Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Pengantar Kuliah

@2011,Eko Didik Widianto Pengantar Kuliah

Deskripsi Kuliah

Standar Kompetensi dan Kompetensi Dasar

Buku Acuan Rencana Perkuliahan Tata Tertib Kuliah Sistem Evaluasi Teknologi CMOS Teknologi Implementasi Rangkaian Digital

Standar Kompetensi

Setelah lulus mata kuliah ini, dengan pemahaman konsep

sistem digital yang diperoleh mahasiswa akan mampu:

1.

merancang, mengimplementasikan dan

menganalisis rangkaian digital menggunakan chip

standar TTL/CMOS (seri 74xx);

2.

merancang, mengimplementasikan dan

menganalisis rangkaian digital menggunakan HDL

Verilog/VHDL di atas FPGA Xilinx Spartan-3E;

Pengantar Kuliah

@2011,Eko Didik Widianto Pengantar Kuliah

Deskripsi Kuliah

Standar Kompetensi dan Kompetensi Dasar

Buku Acuan Rencana Perkuliahan Tata Tertib Kuliah Sistem Evaluasi Teknologi CMOS Teknologi Implementasi Rangkaian Digital

Kompetensi Dasar

I

Lihat GBPP dan SAP untuk daftar lebih lengkap

I

Atau

http://didik.blog.undip.ac.id/2012/09/

Pengantar Kuliah

@2011,Eko Didik Widianto Pengantar Kuliah

Deskripsi Kuliah Standar Kompetensi dan Kompetensi Dasar

Buku Acuan

Rencana Perkuliahan Tata Tertib Kuliah Sistem Evaluasi Teknologi CMOS Teknologi Implementasi Rangkaian Digital

Bahasan

Pengantar Perkuliahan

Deskripsi Kuliah

Standar Kompetensi dan Kompetensi Dasar

Buku Acuan

Rencana Perkuliahan

Tata Tertib Kuliah

Sistem Evaluasi

Teknologi CMOS

Pendahuluan

Saklar Transistor

Rangkaian CMOS

Gerbang Logika CMOS

Rangkuman

Teknologi Implementasi Rangkaian Digital

Pendahuluan

Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Pengantar Kuliah

@2011,Eko Didik Widianto Pengantar Kuliah

Deskripsi Kuliah Standar Kompetensi dan Kompetensi Dasar

Buku Acuan

Rencana Perkuliahan Tata Tertib Kuliah Sistem Evaluasi Teknologi CMOS Teknologi Implementasi Rangkaian Digital

Buku Acuan/Referensi

1.

Stephen Brown and Zvonko Vranesic, Fundamentals

of Digital Logic with Verilog/VHDL, 2nd Edition,

McGraw-Hill, 2005

2.

Peter J. Ashenden, Digital Design: An Embedded

Systems Approach Using Verilog/VHDL, Morgan

Kaufmann, 2008

3.

Ian Grout, “Digital Systems Design with FPGAs and

CPLDs”, Newness, 2008

4.

Verilog Tutorial (online):

http://www.asic-world.com/verilog/veritut.html

5.

UG230: Spartan-3E FPGA Starter Kit Board User

Guide, Xilinx, June 2008

6.

Xilinx ISE Design Suite 11 Software Manual, Xilinx,

Pengantar Kuliah

@2011,Eko Didik Widianto Pengantar Kuliah

Deskripsi Kuliah Standar Kompetensi dan Kompetensi Dasar Buku Acuan

Rencana Perkuliahan

Tata Tertib Kuliah Sistem Evaluasi Teknologi CMOS Teknologi Implementasi Rangkaian Digital

Bahasan

Pengantar Perkuliahan

Deskripsi Kuliah

Standar Kompetensi dan Kompetensi Dasar

Buku Acuan

Rencana Perkuliahan

Tata Tertib Kuliah

Sistem Evaluasi

Teknologi CMOS

Pendahuluan

Saklar Transistor

Rangkaian CMOS

Gerbang Logika CMOS

Rangkuman

Teknologi Implementasi Rangkaian Digital

Pendahuluan

Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Pengantar Kuliah

@2011,Eko Didik Widianto Pengantar Kuliah

Deskripsi Kuliah Standar Kompetensi dan Kompetensi Dasar Buku Acuan

Rencana Perkuliahan

Tata Tertib Kuliah Sistem Evaluasi Teknologi CMOS Teknologi Implementasi Rangkaian Digital

Rencana Acara Perkuliahan

Tentative 14 minggu (tatap muka)

Detail:

http://didik.blog.undip.ac.id/2012/09/02/

tkc-305-sistem-digital-lanjut-2012/

I

Rencana perkuliahan

I

Kompetensi dasar

Pengantar Kuliah

@2011,Eko Didik Widianto Pengantar Kuliah

Deskripsi Kuliah Standar Kompetensi dan Kompetensi Dasar Buku Acuan Rencana Perkuliahan

Tata Tertib Kuliah

Sistem Evaluasi Teknologi CMOS Teknologi Implementasi Rangkaian Digital

Bahasan

Pengantar Perkuliahan

Deskripsi Kuliah

Standar Kompetensi dan Kompetensi Dasar

Buku Acuan

Rencana Perkuliahan

Tata Tertib Kuliah

Sistem Evaluasi

Teknologi CMOS

Pendahuluan

Saklar Transistor

Rangkaian CMOS

Gerbang Logika CMOS

Rangkuman

Teknologi Implementasi Rangkaian Digital

Pendahuluan

Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Pengantar Kuliah

@2011,Eko Didik Widianto Pengantar Kuliah

Deskripsi Kuliah Standar Kompetensi dan Kompetensi Dasar Buku Acuan Rencana Perkuliahan

Tata Tertib Kuliah

Sistem Evaluasi Teknologi CMOS Teknologi Implementasi Rangkaian Digital

Tata Tertib Kuliah

Berlaku bagi Dosen dan Mahasiswa

I

Dosen dan mahasiswa diharapkan hadir pada

waktunya

I

Batas wajar 15 menit dari jadwal yang telah

ditentukan

I

Mahasiswa yang terlambat lebih dari 15 menit tidak

diperkenankan untuk mengikuti kuliah

I

Kehadiran minimal 75% (9 / 12 pertemuan) sebagai

syarat minimal mengikuti UTS dan/atau UAS

ISesuai keputusan jurusan Teknik Sistem Komputer

I

Kuliah yang batal diadakan karena hari libur,

kegiatan insidental jurusan ataupun dosen

berhalangan, akan digantikan di hari lain sesuai

kesepakatan dosen-mahasiswa

Pengantar Kuliah

@2011,Eko Didik Widianto Pengantar Kuliah

Deskripsi Kuliah Standar Kompetensi dan Kompetensi Dasar Buku Acuan Rencana Perkuliahan Tata Tertib Kuliah

Sistem Evaluasi Teknologi CMOS Teknologi Implementasi Rangkaian Digital

Bahasan

Pengantar Perkuliahan

Deskripsi Kuliah

Standar Kompetensi dan Kompetensi Dasar

Buku Acuan

Rencana Perkuliahan

Tata Tertib Kuliah

Sistem Evaluasi

Teknologi CMOS

Pendahuluan

Saklar Transistor

Rangkaian CMOS

Gerbang Logika CMOS

Rangkuman

Teknologi Implementasi Rangkaian Digital

Pendahuluan

Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Pengantar Kuliah

@2011,Eko Didik Widianto Pengantar Kuliah

Deskripsi Kuliah Standar Kompetensi dan Kompetensi Dasar Buku Acuan Rencana Perkuliahan Tata Tertib Kuliah

Sistem Evaluasi Teknologi CMOS Teknologi Implementasi Rangkaian Digital

Sistem Evaluasi

Evaluasi:

No

Evaluasi

Bobot

1

Tugas Mandiri/Kelompok

30%

3

Ujian Tengah Semester

30%

4

Ujian Akhir Semester

40%

Penilaian Akhir:

AA ≥ 80

A

4.0

67 ≤ AA < 80

B

3.0

55 ≤ AA < 67

C

2.0

41 ≤ AA < 55

D

1.0

AA < 41

E

0.0 (Tidak Lulus)

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Pendahuluan Saklar Transistor Rangkaian CMOS Gerbang Logika CMOS Rangkuman Teknologi Implementasi Rangkaian Digital

Bahasan

Pengantar Perkuliahan

Deskripsi Kuliah

Standar Kompetensi dan Kompetensi Dasar

Buku Acuan

Rencana Perkuliahan

Tata Tertib Kuliah

Sistem Evaluasi

Teknologi CMOS

Pendahuluan

Saklar Transistor

Rangkaian CMOS

Gerbang Logika CMOS

Rangkuman

Teknologi Implementasi Rangkaian Digital

Pendahuluan

Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Pendahuluan Saklar Transistor Rangkaian CMOS Gerbang Logika CMOS Rangkuman Teknologi Implementasi Rangkaian Digital

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Pendahuluan Saklar Transistor Rangkaian CMOS Gerbang Logika CMOS Rangkuman Teknologi Implementasi Rangkaian Digital

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Pendahuluan Saklar Transistor Rangkaian CMOS Gerbang Logika CMOS Rangkuman Teknologi Implementasi Rangkaian Digital

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Pendahuluan Saklar Transistor Rangkaian CMOS Gerbang Logika CMOS Rangkuman Teknologi Implementasi Rangkaian Digital

Bahasan

Pengantar Perkuliahan

Deskripsi Kuliah

Standar Kompetensi dan Kompetensi Dasar

Buku Acuan

Rencana Perkuliahan

Tata Tertib Kuliah

Sistem Evaluasi

Teknologi CMOS

Pendahuluan

Saklar Transistor

Rangkaian CMOS

Gerbang Logika CMOS

Rangkuman

Teknologi Implementasi Rangkaian Digital

Pendahuluan

Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Pendahuluan Saklar Transistor Rangkaian CMOS Gerbang Logika CMOS Rangkuman Teknologi Implementasi Rangkaian Digital

Saklar Transistor

I

Rangkaian logika dibangun dengan transistor

I

Asumsi sebuah transistor beroperasi seperti saklar

sederhana yang dikontrol oleh sinyal logika x

I

TIpe transistor untuk mengimplementasikan saklar

sederhana yang sering digunakan adalah MOSFET

(Metal Oxide Semiconductor Field Effect Transistor)

I

2 tipe MOSFET:

I

N-channel (NMOS)

IP-channel (PMOS)

I

Sebelumnya, rangkaian hanya menggunakan salah

satu transistor NMOS atau PMOS saja, bukan

keduanya

I

Rangkaian sekarang menggunakan CMOS

(Complementary MOS) yang tersusun atas NMOS

dan PMOS

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Pendahuluan Saklar Transistor Rangkaian CMOS Gerbang Logika CMOS Rangkuman Teknologi Implementasi Rangkaian Digital

Transistor NMOS sebagai Switch

Transistor NMOS

Simbol NMOS

Model saklar NMOS:

Fungsi saklar:

I

x low (x = 0) →saklar

terbuka

I

x high (x = 1) →saklar

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Pendahuluan Saklar Transistor Rangkaian CMOS Gerbang Logika CMOS Rangkuman Teknologi Implementasi Rangkaian Digital

Operasi NMOS sebagai Saklar

I

Transistor beroperasi dengan

mengontrol tegangan V

G

di

terminal Gate (G)

I

Jika V

G

low, tidak ada

koneksi antara terminal

Source (S) dan Drain (D).

Transistor

mati (off)

I

Jika V

G

high, transistor

hidup (on). Seolah seperti

saklar tertutup antara terminal

Source (S) dan Drain (D)

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Pendahuluan Saklar Transistor Rangkaian CMOS Gerbang Logika CMOS Rangkuman Teknologi Implementasi Rangkaian Digital

Transistor PMOS sebagai Switch

Transistor PMOS

Simbol PMOS

Model saklar NMOS:

Fungsi saklar:

I

x low (x = 0) →saklar

tersambung

I

x high (x = 1) →saklar

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Pendahuluan Saklar Transistor Rangkaian CMOS Gerbang Logika CMOS Rangkuman Teknologi Implementasi Rangkaian Digital

Operasi PMOS sebagai Saklar

I

Transistor beroperasi dengan

mengontrol tegangan V

G

di

terminal Gate (G)

I

Jika V

G

low, tidak ada

koneksi antara terminal

Source (S) dan Drain (D).

Transistor

mati (off)

I

Jika V

G

high, transistor

hidup (on). Seolah seperti

saklar tertutup antara terminal

Source (S) dan Drain (D)

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Pendahuluan Saklar Transistor Rangkaian CMOS Gerbang Logika CMOS Rangkuman Teknologi Implementasi Rangkaian Digital

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Pendahuluan Saklar Transistor Rangkaian CMOS

Gerbang Logika CMOS Rangkuman Teknologi Implementasi Rangkaian Digital

Bahasan

Pengantar Perkuliahan

Deskripsi Kuliah

Standar Kompetensi dan Kompetensi Dasar

Buku Acuan

Rencana Perkuliahan

Tata Tertib Kuliah

Sistem Evaluasi

Teknologi CMOS

Pendahuluan

Saklar Transistor

Rangkaian CMOS

Gerbang Logika CMOS

Rangkuman

Teknologi Implementasi Rangkaian Digital

Pendahuluan

Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Pendahuluan Saklar Transistor Rangkaian CMOS

Gerbang Logika CMOS Rangkuman Teknologi Implementasi Rangkaian Digital

NMOS dan PMOS dalam Rangkaian Logika

I

Saat transistor NMOS

on, maka terminal drainnya

pulled-down ke Gnd

I

Saat transistor PMOS

on, maka terminal drainnya

pulled-up ke VDD

I

Disebabkan cara operasi transistor:

I

Transistor NMOS

tidak dapat digunakan untuk

mendorong terminal drainnya secara penuh ke VDD

I

Transistor PMOS

tidak dapat digunakan untuk

mendorong terminal drainnya secara penuh ke GND

I

Sehingga Dibentuk CMOS, transistor NMOS dan PMOS

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Pendahuluan Saklar Transistor Rangkaian CMOS

Gerbang Logika CMOS Rangkuman Teknologi Implementasi Rangkaian Digital

Gerbang Logika CMOS

I

Gerbang CMOS: pasangan NMOS dan PMOS

I

transistor NMOS membentuk

pull-down network

(PDN)

I

transistor PMOS membentuk

pull-up network (PUN)

I

Fungsi yang direalisasikan dengan PDN dan PUN

adalah saling berkomplemen satu dengan yang lain

I

PDN dan PUN mempunyai jumlah transistor yang

sama

I

Disusun sehingga kedua jaringan adalah

dual satu

sama lain

I

Dimana PDN mempunyai transistor NMOS secara

seri, maka PUN mempunyai PMOS secara paralel

dan sebaliknya

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Pendahuluan Saklar Transistor Rangkaian CMOS

Gerbang Logika CMOS Rangkuman Teknologi Implementasi Rangkaian Digital

Gerbang Logika CMOS

I

Untuk semua valuasi

sinyal masukan:

IPDN menarik V

f

ke

Gnd (

pull-down);

atau

IPUN menarik V

f

ke

VDD

(

pull-up)

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Pendahuluan Saklar Transistor Rangkaian CMOS

Gerbang Logika CMOS

Rangkuman Teknologi Implementasi Rangkaian Digital

Bahasan

Pengantar Perkuliahan

Deskripsi Kuliah

Standar Kompetensi dan Kompetensi Dasar

Buku Acuan

Rencana Perkuliahan

Tata Tertib Kuliah

Sistem Evaluasi

Teknologi CMOS

Pendahuluan

Saklar Transistor

Rangkaian CMOS

Gerbang Logika CMOS

Rangkuman

Teknologi Implementasi Rangkaian Digital

Pendahuluan

Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Pendahuluan Saklar Transistor Rangkaian CMOS

Gerbang Logika CMOS

Rangkuman Teknologi Implementasi Rangkaian Digital

Gerbang NOT CMOS

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Pendahuluan Saklar Transistor Rangkaian CMOS

Gerbang Logika CMOS

Rangkuman Teknologi Implementasi Rangkaian Digital

Gerbang NAND CMOS

I

Diimplementasikan dengan

4 transistor

x

1x

2T1

T2

T3

T4

f

0

0

On

On

Off

Off

1

0

1

On

Off

Off

On

1

1

0

Off

On

On

Off

1

1

1

Off

Off

On

On

0

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Pendahuluan Saklar Transistor Rangkaian CMOS

Gerbang Logika CMOS

Rangkuman Teknologi Implementasi Rangkaian Digital

Gerbang NOR CMOS

I

Diimplementasikan dengan

4 transistor

x

1x

2T1

T2

T3

T4

f

0

0

On

On

Off

Off

1

0

1

On

Off

Off

On

0

1

0

Off

On

On

Off

0

1

1

Off

Off

On

On

0

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Pendahuluan Saklar Transistor Rangkaian CMOS

Gerbang Logika CMOS

Rangkuman Teknologi Implementasi Rangkaian Digital

Gerbang AND CMOS

I

Diimplementasikan dengan

6 transistor

x

1x

2T1 T2 T3 T4

T5 T6

f

0

0

On On Off Off Off On 0

0

1

On Off Off On Off On 0

1

0

Off On On Off Off On 0

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Pendahuluan Saklar Transistor Rangkaian CMOS

Gerbang Logika CMOS

Rangkuman Teknologi Implementasi Rangkaian Digital

Gerbang OR CMOS

I

Diimplementasikan dengan

6 transistor

x

1x

2T1 T2 T3 T4

T5 T6

f

0

0

On On Off Off Off On 0

0

1

On Off Off On On Off 1

1

0

Off On On Off On Off 1

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Pendahuluan Saklar Transistor Rangkaian CMOS Gerbang Logika CMOS

Rangkuman Teknologi Implementasi Rangkaian Digital

Bahasan

Pengantar Perkuliahan

Deskripsi Kuliah

Standar Kompetensi dan Kompetensi Dasar

Buku Acuan

Rencana Perkuliahan

Tata Tertib Kuliah

Sistem Evaluasi

Teknologi CMOS

Pendahuluan

Saklar Transistor

Rangkaian CMOS

Gerbang Logika CMOS

Rangkuman

Teknologi Implementasi Rangkaian Digital

Pendahuluan

Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Pendahuluan Saklar Transistor Rangkaian CMOS Gerbang Logika CMOS

Rangkuman

Teknologi Implementasi Rangkaian Digital

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan

Chip Standar Seri 7400 Programmable Logic Device Rangkuman

Bahasan

Pengantar Perkuliahan

Deskripsi Kuliah

Standar Kompetensi dan Kompetensi Dasar

Buku Acuan

Rencana Perkuliahan

Tata Tertib Kuliah

Sistem Evaluasi

Teknologi CMOS

Pendahuluan

Saklar Transistor

Rangkaian CMOS

Gerbang Logika CMOS

Rangkuman

Teknologi Implementasi Rangkaian Digital

Pendahuluan

Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan

Chip Standar Seri 7400 Programmable Logic Device Rangkuman

Implementasi Sistem Digital

Implementasi sistem digital yang akan dipelajari,

menggunakan:

1.

Chip standar TTL seri 7400

2.

Programmable Logic Device (PLA, PAL, CPLD,

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan

Chip Standar Seri 7400 Programmable Logic Device Rangkuman

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan

Chip Standar Seri 7400 Programmable Logic Device Rangkuman

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan

Chip Standar Seri 7400

Programmable Logic Device Rangkuman

Bahasan

Pengantar Perkuliahan

Deskripsi Kuliah

Standar Kompetensi dan Kompetensi Dasar

Buku Acuan

Rencana Perkuliahan

Tata Tertib Kuliah

Sistem Evaluasi

Teknologi CMOS

Pendahuluan

Saklar Transistor

Rangkaian CMOS

Gerbang Logika CMOS

Rangkuman

Teknologi Implementasi Rangkaian Digital

Pendahuluan

Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan

Chip Standar Seri 7400

Programmable Logic Device Rangkuman

Chip Standar

I

Rangkaian logika sederhana umumnya

menggunakan chip logika standar

ITerdiri dari beberapa gerbang logika

I

Dikenal sebagai device seri 7400 karena nomor

komponen diawali dengan 74

I

Umumnya dipaket dalam

dual-inline package/DIP

IKoneksi eksternal dari chip disebut

pin atau lead

IDua pin menghubungkan V

DD

dan GND ke sumber

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan

Chip Standar Seri 7400

Programmable Logic Device Rangkuman

Keluarga Seri 7400

I

Fungsi: gerbang logika dasar, flip-flop dan counter,

bus transceiver, ALU, dll

ILihat:

http://en.wikipedia.org/wiki/List_of_7400_series_integrated_circuits

I

Konstruksi transistor: bipolar, CMOS, BiCMOS

I

transistor bipolar mempunyai kecepatan lebih tinggi,

tapi butuh daya lebih besar daripada CMOS

I

BiCMOS: trade-off antara kecepatan dengan

kebutuhan daya

I

Level tegangan logika

I

Bipolar/TTL: 5V

ICMOS: 3.3V, 5V

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan

Chip Standar Seri 7400

Programmable Logic Device Rangkuman

Skema Penomoran IC

Pemberian Suffix

I

Teknologi:

I

Bipolar: standar

I

CMOS: identitas ’C’, misalnya A

C, HC, FC, LVC

IBiCMOS: identitas ’B’, misalnya

BCT, ABT

I

Kecepatan: (CMOS)

I

Suffix ’H’ untuk high-speed

I

Suffix ’F’ untuk fast, lebih cepat dari ’H’

I

Level tegangan ’TTL’ dan power: (Bipolar)

I

Suffix ’L’ untuk low power di bipolar

I

Suffix ’L’ untuk level tegangan 3.3V di CMOS

I

Fitur lainnya:

I

Suffix ’X’ untuk level tolerant baik 3.3V maupun 5V

IKemasan: DIP, TSSOP, TSOP, SOIC

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan

Chip Standar Seri 7400

Programmable Logic Device Rangkuman

IC 7404

Hex Inverter

I

6 buah gerbang logika NOT

I

Contoh:

I

74AHCT04PW: NXP Semiconductor, 14-TSSOP, 5V,

CMOS

I

SN74ALVC04: Texas Instruments, 3.3V, CMOS

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan

Chip Standar Seri 7400

Programmable Logic Device Rangkuman

Contoh Implementasi Rangkaian

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Bahasan

Pengantar Perkuliahan

Deskripsi Kuliah

Standar Kompetensi dan Kompetensi Dasar

Buku Acuan

Rencana Perkuliahan

Tata Tertib Kuliah

Sistem Evaluasi

Teknologi CMOS

Pendahuluan

Saklar Transistor

Rangkaian CMOS

Gerbang Logika CMOS

Rangkuman

Teknologi Implementasi Rangkaian Digital

Pendahuluan

Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Programmable Logic Device (PLD)

I

Jika fungsi rangkaian logika diimplementasikan

dengan dengan komponen seri 7400

IFixed dan hardware-based

I

Tiap chip hanya menyediakan gerbang logika

sederhana

I

Tidak efisien untuk membuat rangkaian yang lebih

kompleks

I

Diperlukan untuk membuat rangkaian yang tersusun

atas gerbang logika dengan struktur yang tidak fixed

(fungsi dapat diprogram)

I

Menggunakan

programmable logic devices (PLD)

IDevais dapat diprogram untuk menghasilkan

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Programmable Logic Device

I

PLD adalah chip general-purpose

yang digunakan untuk

mengimplementasikan rangkaian

logika (kombinasional)

I

Berisi koleksi elemen rangkaian

logika yang dapat dikonfigurasi

(diprogram)

I

Dapat dilihat sebagai black-box yang

berisi gerbang logika dan saklar

terprogram yang memungkinkan

koneksi antar elemen logika

I

Dapat mengimplementasikan

sebarang rangkaian logika yang

diinginkan

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

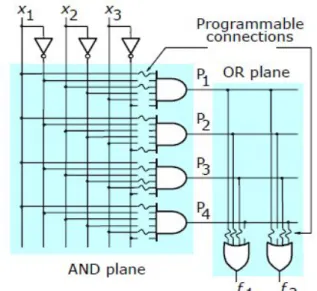

Programmable Logic Array (PLA)

I

PLD yang pertama dikembangkan

adalah

programmable logic array

(PLA)

I

Menggunakan premise bahwa

sebarang fungsi dapat dituliskan

dalam bentuk SOP

I

Struktur PLA:

I

Masukan buffer dan inverter

yang menyediakan nilai true

dan komplemen untuk tiap

variabel masukan

I

Kumpulan gerbang AND yang

inputnya dapat diprogram

I

Kumpulan gerbang OR yang

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Diagram Gate-Level PLA

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Skematik PLA

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Programmable Array Logic (PAL)

I

Di PLA, plane AND dan OR keduanya programmable

I

Programmable Array Logic (PAL), lebih sederhana

I

plane OR

tetap

I

PAL lebih mudah untuk dimanufaktur dan dapat

beroperasi lebih cepat daripada PLA

I

struktur ini paling banyak digunakan di aplikasi yang

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Programmable Array Logic

Contoh PAL

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Programmable Array Logic

Rangkaian Tambahan di PAL (macrocell)

I

Device PAL mempunyai rangkaian tambahan di

keluaran tiap gerbang OR untuk menyediakan

fungsional tambahan

I

Macrocell: gerbang OR dikombinasikan dengan

rangkaian tambahan

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Memprogram PLA dan PAL

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Memprogram PLA dan PAL

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Memprogram PLA dan PAL

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Complex Programmable Logic Device

(CPLD)

I

Untuk desain rangkaian yang lebih besar yang tidak dapat

diimplementasikan dengan PLA atau PAL

I

Digunakan complex programmable logic device /

CPLD

I

CPLD berisi blok-blok rangkaian yang dapat saling

dihubungkan dan disambungkan ke pin chip dengan

penyambungan internal

I

Tiap blok menyerupai sebuah PAL (disebut PAL-like

block)

I

CPLD komersial dapat mempunyai 2 - 100 block PAL-like

I

Tiap blok mempunyai 16 macrocell

I

Tiap macrocell setara dengan 20 gerbang atau

hampir 20K gerbang ekivalen untuk CPLD dengan

1000 macrocell

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Complex Programmable Logic Device

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Field-Programmable Gate Array (FPGA)

I

Untuk mengimplementasikan rangkaian yang lebih

besar lagi, digunakan tipe IC yang dapat mempunyai

kapasitas logika yang lebih besar

I

Field Programmable Gate Array (FPGA)

I

Tidak berisi blok AND dan OR

I

Berisi array blok logika dan jalur interkoneksi antar

blok

I

Jalur interkoneksi disusun sebagai kanal routing

secara horisontal dan vertikal yang berisi

programmable switch

I

Dapat mengimplementasikan fungsi logika dengan

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Field-Programmable Gate Array

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan Chip Standar Seri 7400 Programmable Logic Device

Rangkuman

Bahasan

Pengantar Perkuliahan

Deskripsi Kuliah

Standar Kompetensi dan Kompetensi Dasar

Buku Acuan

Rencana Perkuliahan

Tata Tertib Kuliah

Sistem Evaluasi

Teknologi CMOS

Pendahuluan

Saklar Transistor

Rangkaian CMOS

Gerbang Logika CMOS

Rangkuman

Teknologi Implementasi Rangkaian Digital

Pendahuluan

Chip Standar Seri 7400

Programmable Logic Device

Rangkuman

Pengantar Kuliah @2011,Eko Didik Widianto Pengantar Kuliah Teknologi CMOS Teknologi Implementasi Rangkaian Digital Pendahuluan Chip Standar Seri 7400 Programmable Logic Device

Rangkuman