KATA PENGANTAR

Modul Perancangan Sistem Digital menggunakan Simulator Xilinx Foundation

F2.1i ini ditujukan bagi peserta kursus satu minggu dengan judul yang sama yang

diselenggarakan oleh Universitas Gunadarma. Tujuan dari modul ini adalah agar mahasiswa dapat memahami dan mampu merancang rangkaian digital.

Modul Perancangan Sistem Digital Menggunakan Simulator Xilinx terdiri dari 5 pokok bahasan. Dimulai dari pokok bahasan pertama yang membahas tentang simulator Xilinx secara umum, kedua membahas schematic editor dan functional simulation untuk rangkaian digital yang sederhana, dan ketiga mengenai counter, ke-empat bagaimana menentukan suatu keputusan dengan binary counter, dan yang terakhir mengenai output-forming logic design.

Kami selaku tim penyusun modul ini menyadari masih terdapat banyak kekurangan dan dengan segala kerendahan hati kami menerima masukan serta kritikan yang bersifat membangun dengan hati yang lapang.

DAFTAR ISI

Kata Pengantar ...i

Daftar Isi ...ii

BAB I Pendahuluan ...1

1.1 Perangkat Lunak Xilinx ...1

1.2 Proses Perancangan secara umum ...2

1.3 Tipe Peralatan : FPGA dan CPLD ...3

1.4 Xilinx Project Manager ……...4

BAB II Simulator Xilinx pada Rangkaian Digital Sederhana ...7

2.1 Disain Rangkaian Digital dengan Xilinx ...7

2.2 Schematic Editor ………..8

2.3 Functional Simulation ………11

2.4 Simulasi Gerbang Dasar ………13

2.5 Penyederhanaan Rangkaian ………17

BAB III COUNTER ...25

3.1 Counter secara umum ……….25

3.2 Flip-flop ……….26

3.3 State Machine ……….28

3.4 Perancangan Counter ……….32

BAB IV MENENTUKAN KEPUTUSAN DENGAN BINARY COUNTER ...51

BAB V OUTPUT FORMING LOGIC ...61

5.1 Output Forming Logic ………61

5.2 Komponen-komponen Output Forming Logic ………..62

5.3 Perancangan rangkaian digital mesin jamu pilih ...67

BAB I

PENDAHULUAN

OBYEKTIF :

- Memahami perangkat lunak Xilinx secara umum - Memahami komponen-komponen simulator Xilinx

1.1 Perangkat Lunak Xilinx

Xilink ( Xilink Foundation Series) adalah suatu perangkat lunak yang berguna

untuk merancang dan mensimulasikan suatu rangkaian digital. Dengan menggunakan Xilink proses perancangan suatu alat atau rangkaian digital melalui proses simulasi rangkaian yang telah dirancang untuk melihat apakah rancangan yang telah dibuat sudah benar atau masih mengandung kesalahan.

Gambar 1.1 : Xilinx Foundation Series

Untuk perancangan rangkaian digital, Xilink mempunyai tiga cara, yaitu dengan menggunakan State Diagram, HDL (Hardware Description Language) dan Schematic. Dalam perancangan bisa menggunakan salah satu cara saja atau menggabungkan ketiga cara tersebut. Untuk HDL, Xilink dapat menggunakan dua bahasa pemrograman yaitu ABEL dan VHDL.

1.2 Proses Perancangan Secara Umum

Proses perancangan menggunakan simulator Xilinx secara umum dapat dilihat pada gambar 1.2 dimana proses perancangan dapat dibagi menjadi 3 bagian yaitu pertama perancangan rangkaian, kemudian verifikasi hasil rancangan dan proses yang ketiga implementasi rancangan[1].

Gambar 1.2 : Proses perancangan secara umum

Perancangan rangkaian pada dasarnya terdiri dari 2 mode yaitu schematic dan

Hardware Description Language (HDL). HDL merupakan bahasa pemrograman seperti VHDL, Verilog dan ABEL. Pada Schematic flow mode dimungkinkan untuk merancang rangkaian yang terdiri dari top-level schematic atau file top-level ABEL, yang terdiri dari schematic diagram, state machine macro, macro HDL (ABEL, VHDL atau Verilog), LogiBLOX, Modul generator CORE.

XS95). Kedua peralatan tersebut juga dapat diprogram dalam sistem dengan menghubungkan JTAG atau kabel Xchecker ke peralatan pin yang telah di program.

Verifikasi rancangan termasuk didalamnya functional simulation, testing

rangkaian, dan timing simulation. Functional simulation dapat dilakukan setelah menggambar rancangan pada schematic editor untuk memverifikasi kebenaran rangkaian. Akan tetapi functional simulation tidak menyediakan timing information seperti delay,

race condition, set-up dan hold-time violations. Informasi ini diperoleh dari static timing simulator dan dilakukan setelah rancangan di-compile. Gambar 1.3 menunjukkan proses yang dilakukan pada schematic flow projct.

Gambar 1.3 : Schematic flow project [2] 1.3 Tipe Peralatan : FPGA dan CPLD

XC4000 series) berasitektur array dan volatile (SRAM) yang digunakan untuk lookup tables (disimpan pada memori SRAM) untuk mengimplementasikan fungsi logika. Perlu dipahami mengenai fungsi logika yang kompleks yang terdiri dari rangkaian kombinasional dan sekuensial, dimana kapasitasnya terbatas oleh jumlah pin input/output dan bukan dari segi kompleksitasnya. FPGA dapat di implementasikan pada gerbang logika diatas sekitar 1 juta gerbang dan beroperasi diatas 150 MHz. XC4000XL dan XC9500XL adalah peralatan 3,3V dengan 3,3V Vcc tetapi mempunyai toleransi I/O sekitar 5V.

Peralatan terbentuk dari paket yang bervariasi. Demoboard FPGA atau board XS40 dan XS95 merupakan suatu paket dengan 84 pin PLCC dan terdiri dari : XC4010EPC84, XC4005XLPC84 dan XC95108PC84. Untuk menentukan peralatan mane yang akan digunakan, telitilah board yang tersedia. Informasi lebih detil dari peralatan ini dapat dilihat pada Xilinx Programmable Logic Data book. Pin out dari peralatan XC400 dan XC9500 84-pin dapat dilihat pada website Xilinx.

1.4 Xilinx Project Manager

Program Xilinx dapat dijalankan dengan START/PROGRAM/XILINX FOUNDATION SERIES/XILINX FOUNDATION PROJECT MANAGER atau dengan klik ikon seperti yang terlihat pada gambar 1.4.

Gambar 1.4 : Ikon project manager

Gambar 1.5 : Project manager

Project manager memberikan akses ke semua tools yang dibutuhkan pada proses perancangan, simulasi dan implementasi projek. Dari project manager window juga dapat membuat project baru, membuka project yang telah dibuat serta menghapus project.

Memulai project baru (pada contoh PERC1AND), foundation tool membentuk beberapa file, yaitu ; file konfigurasi project (PDF) yang disebut dengan Project Description File (perc1and.pdf) dan 3 file library

Project manager window diatas dibagi menjadi tiga bagian utama : - hierarcy browser

- project flowchart - message window

Hierarchy Browser

Project Flowchart

Project Flowchart adalah representasi grafik dari proses rancangan yang berguna untuk menunjukkan langkah-langkah yang terjadi dalam suatu operasi. Walaupun kita hanya menjalankan salah satu aplikasi, misalnya State Editor, secara otomatis Project Manager ikut aktif pula. Bila kita sudah

berada didalam Project Manager kita bisa mulai merancang rangkaian digital kita. Alur kerja Project Manager adalah sebagai berikut :

1. Rancangan digital dapat menggunakan salah satu dari HDL Entry, Schematic Editor atau State Editor atau menggunakan ketiga - tiganya.

2. Functional Simulator akan memerikasa apakah rancangan yang dibuat sudah benar atau belum. Bila masih salah kita dapat untuk mengedit kembali rancangan yang telah dibuat sampai kesalahan yang ada diperbaiki semuanya. 3. Setelah itu timing simulation dapat kita jalankan untuk melihat hasil

rancangan rangkaian digital kita.

4. Foundation Implementation tools akan meng-compile rancangan yang telah dibuat menjadi bitstream yang sesuai dengan target device yang dipilih (XC9500 atau XC4005 ).

5. Setelah itu dapat dilihat jalannya program yang telah dibuat pada pada papan simulator XS95 atau XS40 yang dihubungkan melalui kabel pararel ke komputer.

Untuk langkah 5 dan 6 tidak akan dibahas, karena untuk melakukan langkah-langkah tersebut diperlukan alat tambahan ( XS95 atau XS40 ).

Message Window

BAB II

SIMULATOR XILINX PADA

RANGKAIAN DIGITAL SEDERHANA

OBYEKTIF :

- Memahami perangkat lunak Xilinx

- Mampu menggambarkan gerbang digital dasar pada schematic editor - Mampu mensimulasikan gerbang dasar digital

- Mampu menyederhanakan rangkaian digital dan mensimulasikannya

2.1 Disain Rangkaian Digital dengan Xilinx

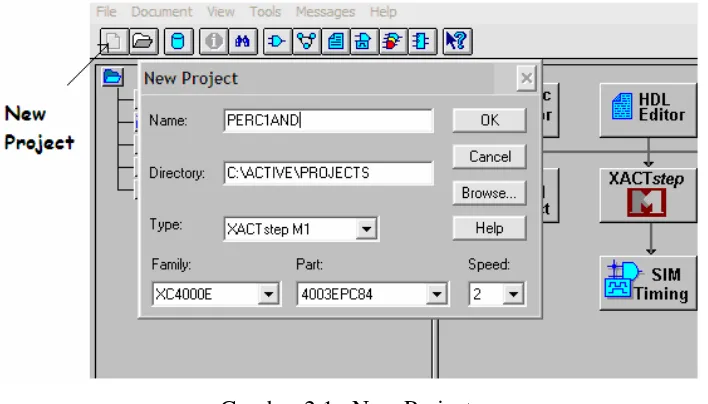

Projek baru dapat dimulai klik File Æ New project. Setelah itu akan muncul window New Project. Kemudian tuliskan nama project dan direktori tempat file project akan disimpan, tipe, chip famili dan chip part number serta device speed. Seperti yang terlihat pada gambar 2.1 dengan nama projek baru PERC1AND dengan direktori C:\active\projects.

Gambar 2.2 : Projek PERC1AND

Pada bagian selanjutnya akan dibahas mengenai schematic editor dan simulasi.

2.2 Schematic Editor

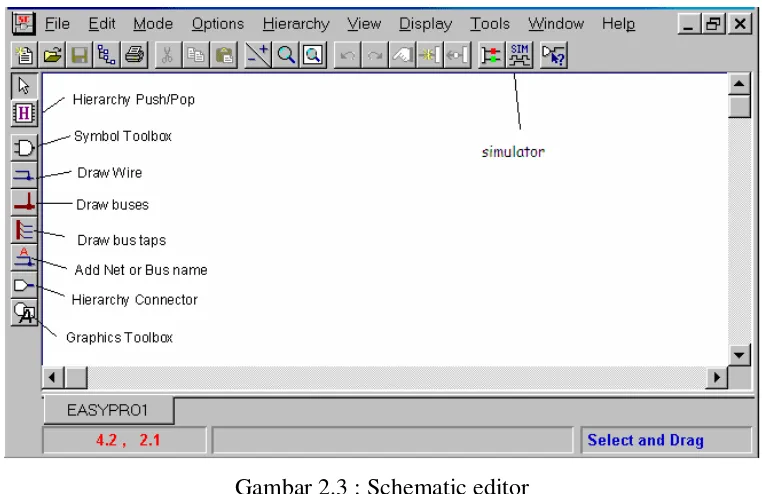

Klik Schematic editor untuk bisa memulai menggambar rangkaian sehingga akan terbuka window seperti gambar 2.3, atau dengan klik ToolsÆ Schematic editor.

Gambar 2.3 : Schematic editor

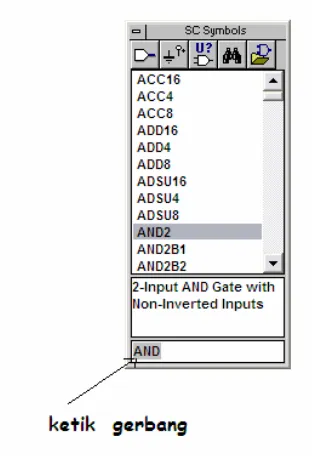

Gambar 2.4 : SC Symbols

Pada percobaan pertama ini gambar gerbang and dengan dua masukan ( A dan B ) dan satu keluaran (Y) seperti yang terlihat pada gambar 2.5.

Gambar 2.5 : Gambar Schematic Editor Gerbang AND

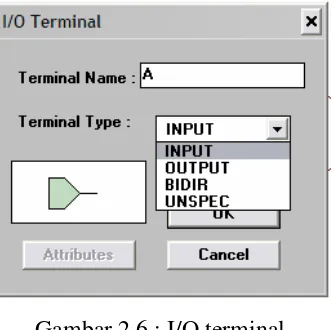

Input dan output (A, B dan Y) digambar dengan klik hierarchy connector atau

I/O Terminal kemudian ketik terminal name dan type terminal, seperti yang terlihat pada

Gambar 2.6 : I/O terminal

Setelah selesai membuat rangkaian periksa apakah rangkaian sudah benar atau belum, caranya dengan memilih Options Æ Create Netlist setelah itu pilih Options Æ Integrity Test. Jika rangkaian masih ada yang salah maka Xilinx akan menampilkan kesalahan tersebut, sehingga rangkaian dapat diperbaiki sampai benar.

Setelah memeriksa kebenaran rangkaian lanjutkan dengan mengirim netlist yang sudah dibuat tadi. Maksud dari pengiriman netlist ini supaya rancangan rangkaian dapat dibaca oleh aplikasi Xilinx yang lain (seperti Simulator). Caranya pilih Options Æ Export Netlist. Export Netlist window akan muncul. Pilih Edit 200 [*.EDN] pada Netlist Format. Setelah itu tekan OK.

Dari gambar rangkaian yang telah digambar dapat diperoleh HDL Program (hanya tersedia VHDL). Caranya adalah pilih Options Æ Export Netlist. Kemudian pilih Vhdl [ *.VHD ] pada Netlist Format setelah itu tekan OK. Sekarang dapat dilihat HDL program dari Gambar rangkaian yang telah digambar. Berikut ini adalah listing programnya (dalam VHDL) :

-- ACTIVE-CAD-2-VHDL, 2.5.4.34, Fri Nov 26 02:34:02 2004

Y : out std_logic ); end X1;

architecture STRUCTURE of X1 is --COMPONENTS

component AND2 port ( I0 : in std_logic; I1 : in std_logic; O : out std_logic ); end component; --SIGNALS

2.3 Functional Simulation

Setelah selesai membuat rancangan Schematic sekarang dapat dilihat simulasi Timing Diagram yang dihasilkan oleh rangkaian yang telah dibuat. Caranya adalah meng-klik simulator pada Project Window. Kemudian akan tampak Logic-Simulator

Foundation window dan Waveform Viewer Window yang masih kosong. Seperti yang

Yang pertama harus lakukan adalah menambahkan input dan output pada

Waveform Viewer supaya dapat melakukan simulasi. Caranya adalah pilih Signal Æ Add Signals. Component Selection for Waveform Viewer window akan muncul seperti yang terlihat pada gambar 2.8. Kemudian pilihlah Input dan Output yang akan disimulasikan. Setelah selesai pilih Close.

Gambar 2.8 : Component selection for waveform viewer

Setelah semua Input dan Output dipilih, tambahkan Stimulator supaya rangkaian dapat disimulasikan. Caranya pilih Signal Æ Add Stimulators. Stimulator Selection window akan muncul seperti yang terlihat gambar 2.9.

Gambar 2.9 : Stimulator selection

Gambar 2.10 : Hasil simulasi gerbang And

Dari Timing Diagram terlihat hasil simulasi gerbang And yaitu 000, 100, 010, 111 dan seterusnya. Dari timing diagram dapat dilihat bahwa herbang And adalah gerbang yang memberikan keluaran hanya bila semua masukan ada. Dengan kata lain gerbang AND merupakan gerbang semua atau tidak ada ; keluaran hanya terjadi bila semua masukan ada.

2.4 Simulasi Gerbang Dasar

Pada bagian ini menggambar semua gerbang logika dasar dan mensimulasikan masing-masing gambar tersebut.

2.4.1 Gerbang OR

Gerbang OR adalah gerbang dimana salah satu atau semua masukan; keluaran terjadi bila salah satu atau semua masukan ada. Gerbang OR memberikan keluaran 1 bila salah satu masukan atau ke dua masukan adalah 1. Lihat gambar 2.11 dan gambar 2.12.

Gambar 2.12 : Simulasi gerbang OR

2.4.2 Gerbang NOT

Gerbang NOT adalah gerbang logika yang memberikan keluaran tidak sama dengan masukannya. Gerbang NOT disebut juga inverter. Gerbang ini mempunyai sebuah masukan dan sebuah keluaran, yang dilakukannya hanyalah membalik sinyal masukan; jika masukan tinggi, keluaran adalah rendah, dan sebaliknya. Lihat gambar 2.13 dan 2.14.

Gambar 2.13 : Schematic editor gerbang NOT

Gambar 2.14 : Simulasi gerbang NOT

2.4.3 Gerbang NAND (NOT-AND)

Gambar 2.15 : Schematic editor gerbang NAND

Gambar 2.16 : Simulasi gerbang NAND

2.4.4 Gerbang NOR

Gerbang NOR adalah gerbang OR yang diikuti gerbang NOT. Lihat gambar 2.17 dan 2.18.

2.4.5 Gerbang XOR

Gerbang ini mempunyai dua masukan dan satu keluaran. XOR adalah nama lain dari Oreksklusif, disebut demikian karena gerbang XOR memberikan keluaran 1 bila

masukan pertama atau masukan kedua adalah 1, namun tidak kedua-duanya. Dengan kata lain, gerbang XOR mempunyai keluaran 1 hanya bila ke dua masukannya berbeda

dan keluarannya 0 apabila ke dua masukannya sama. Lihat gambar 2.19 dan 2.20.

Gambar 2.19 : Schematic editor gerbang XOR

Gambar 2.20 : Simulasi gerbang XOR

2.4.6 Gerbang XNOR

Gambar 2.21 : Schematic editor gerbang XNOR

2.5 Penyederhanaan Rangkaian

Penyederhanaan rangkaian logika dapat dilakukan dengan beberapa metode seperti metode Peta Karnaugh, metode Maksterm/Minterm, metode Aljabar Boolean dan lain sebagainya. Pada sub bagian ini dengan menggunakan simulator Xilinx dapat di ketahui kebenaren hasil penyederhanaan rangkaian dengan mensimulasikan rangkaian sebelum disederhanakan dan yang setelah disederhanakan, dan kemudian membandingkan apakah timing diagram kedua rangkaian tersebut sama atau tidak.

2.5.1 Menyederhanakan rangkaian Y=ABC+ABC+ABC+ABC:

Untuk menyederhanakan rangkaian Y=ABC+ABC+ABC+ABCdapat dilakukan dengan langkah-langkah sebagai berikut :

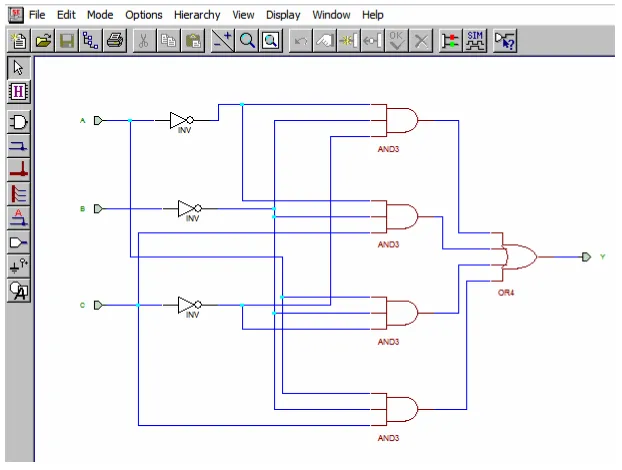

Langkah -1 : gambar rangkaian Y=ABC+ABC+ABC+ABC pada schematic editor, seperti yang terlihat pada gambar 2.23.

Gambar 2.23 : schematic editor Y=ABC+ABC+ABC+ABC

Gambar 2.24 : hasil simulasi Y=ABC+ABC+ABC+ABC

Langkah -3 : sederhanakan rangkaian Y=ABC+ABC+ABC+ABC, pada gambar 2.25 penyederhanaan rangkaian menggunakan peta karnaugh.

AB C

00 01 11 10 0 1 0 0 1 1 1 0 0 1

Gambar 2.25 : Peta Karnaugh rangkaian Y=ABC+ABC+ABC+ABC

Langkah -4 : gambar rangkaian yang telah disederhanakan, seperti yang terlihat pada gambar 2.26.

Gambar 2.26 : Schematic editor Y = B

Langkah -5 : simulasikan rangkaian yang telah disederhanakan, seperti yang terlihat pada gambar 2.27.

Gambar 2.27 : simulasi

Langkah -6 : bandingkan hasil simulasi rangkaian sebelum disederhanakan (langkah-2) dengan hasil simulasi rangkaian yang telah disederhanakan (langkah-5).

Dari timing diagram gambar 2.27 sama dengan timing diagram gambar 2.24 sehingga dapat disimpulkan bahwa penyederhanaan rangkaian yang dilakukan benar.

2.5.2 Simulasikan X=ABCD+ABCD+ABCD+ABCD+ABCD+ABCD+ABCD dan sederhanakan persamaan serta buktikan hasil penyederhanaan yang dilakukan benar dengan mensimulasikan hasil penyederhanaan persamaan yang diperoleh!

Langkah 1 :

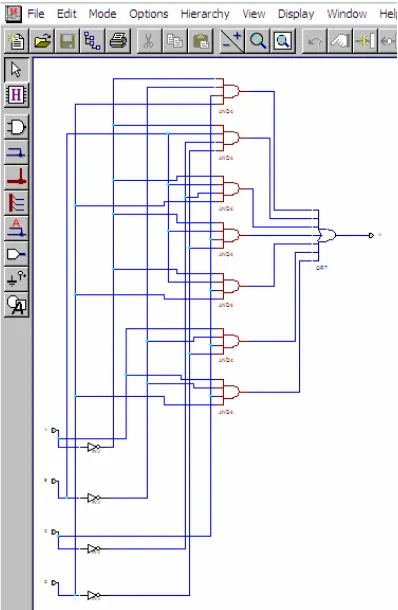

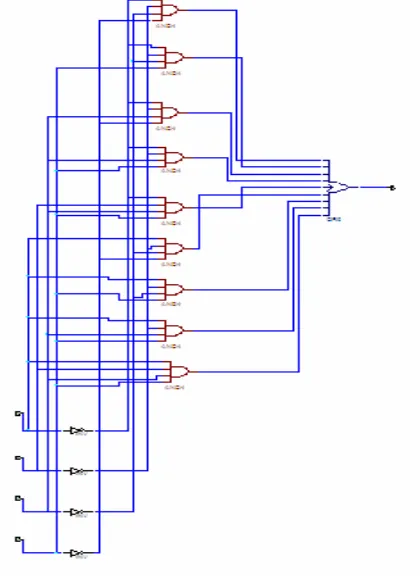

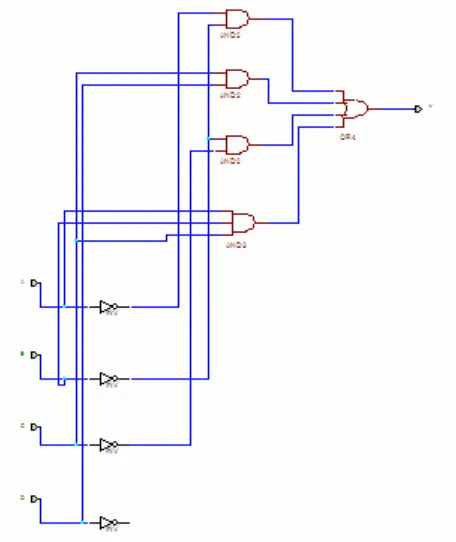

gambar rangkaian X=ABCD+ABCD+ABCD+ABCD+ABCD+ABCD+ABCD pada schematic editor, seperti yang terlihat pada gambar 2.28.

Langkah -2 : simulasikan rangkaianX=ABCD+ABCD+ABCD+ABCD+ABCD+ABCD+ABCD, seperti yang terlihat pada gambar 2.29.

Langkah -3 :

Gambar 2.28 : schematic editor X=ABCD+ABCD+ABCD+ABCD+ABCD+ABCD+ABCD

Gambar 2.29 : hasil simulasi X=ABCD+ABCD+ABCD+ABCD+ABCD+ABCD+ABCD

AB CD

00 01 11 10 00 0 1 0 0 01 0 1 0 0 11 1 1 0 1 10 0 1 0 1

Gambar 2.30 : Peta Karnaugh

Langkah -4 : gambar rangkaian yang telah disederhanakan, seperti yang terlihat pada gambar 2.31.

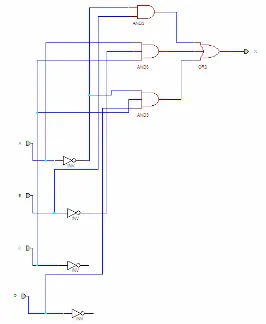

Gambar 2.31 : Schematic editor X= A B + A B C + A C D

Langkah -5 : simulasikan rangkaian yang telah disederhanakan, seperti yang terlihat pada gambar 2.32.

Gambar 2.32 : simulasi X= A B + A B C + A C D

Langkah -6 : bandingkan hasil simulasi rangkaian sebelum disederhanakan (langkah-2) dengan hasil simulasi rangkaian yang telah disederhanakan (langkah-5).

2.5.3 Simulasikan persamaan berikut ini dan sederhanakanlah persamaan tersebut, buktikanlah bahwa hasil penyederhanaan yang dilakukan benar!

ABCD

Lakukan seperti pada bagian 2.51 dan 2.5.2. Langkah 1 : buat Schematic editor rangkaian

ABCD

Gambar 2.33 : Schematic editor

Langkah 2 : simulasikan sehingga diperoleh timing diagramnya (gambar 2.34)

Gambar 2.34 : Hasil simulasi

AB CD

00

01 11 10

00 1 0 0 1 01 1 0 0 1 11 1 1 1 1 10 1 0 1 0 Gambar 2.35 : peta karnaugh

Langkah 4 : gambar hasil rangkaian yang telah disederhanakan (Y = AB+CD+BC+ABC)

Gambar 2.36 : peta karnaugh

Langkah 5 : simulasikan rangkaian yang telah disederhanakan sehingga diperoleh timing diagramnya

Langkah 6 : bandingkan timing diagram sebelum disederhanakan dengan yang setelah disederhanakan.

Dari kedua hasil simulasi rangkaian sebelum disederhanakan (gambar 2.34) dan yang setelah disederhanakan (gambar 2.37) sama, sehingga proses penyederhanaan yang dilakukan benar.

2.5.4 Simulasikan persamaan berikut ini dan sederhanakanlah persamaan tersebut, buktikanlah bahwa hasil penyederhanaan yang dilakukan benar!

ABCD

Langkah 1 : gambar rangkaian diatas pada schematic editor! Langkah 2 : simulasikan sehingga diperoleh timing diagramnya! Langkah 3 : Sederhanakan rangkaian tersebut!

Langkah 4 : gambar hasil rangkaian yang telah disederhanakan !

Langkah 5 : simulasikan rangkaian yang telah disederhanakan sehingga diperoleh timing diagramnya !

Langkah 6 : bandingkan timing diagram sebelum disederhanakan dengan yang setelah disederhanakan!

2.5.5 Simulasikan persamaan berikut ini dan sederhanakanlah persamaan tersebut, buktikanlah bahwa hasil penyederhanaan yang dilakukan benar!

D

Langkah 1 : gambar rangkaian di atas pada schematic editor! Langkah 2 : simulasikan sehingga diperoleh timing diagramnya! Langkah 3 : Sederhanakan rangkaian tersebut !

Langkah 4 : gambar hasil rangkaian yang telah disederhanakan !

Langkah 5 : simulasikan rangkaian yang telah disederhanakan sehingga diperoleh timing diagramnya!

BAB III

COUNTER

OBYEKTIF :

- Memahami jenis-jenis counter

- Mampu merancang rangkaian suatu counter

3.1 Counter secara umum

Counter merupakan rangkaian logika pengurut, karena counter membutuhkan karakteristik memori, dan pewaktu memegang peranan yang penting. Counter digital mempunyai karakteristik penting yaitu sebagai berikut :

1. Jumlah hitungan maksimum (modulus N-counter)

2. Menghitung ke-atas atau ke-bawah (up atau down - counter) 3. Operasi asinkron atau sinkron

4. Bergerak bebas atau berhenti sendiri

Sebagaimana dengan rangkaian sekuensial yang lain, untuk menyusun counter digunakan

flip-flop. Counter dapat digunakan untuk menghitung banyaknya clock-pulsa dalam waktu yang tersedia (pengukuran frekuensi), Counter dapat juga digunakan untuk membagi frekuensi dan menyimpan data.

Ada dua macam counter, yaitu Asinkronous Counter dan Sinkronous Counter. Asinkronous Counter disebut juga Ripple Through Counter atau Counter Serial (Serial Counter), karena output masing-masing flip-flop yang digunakan akan berubah kondisi dari “0” ke “1” dan sebaliknya secara berurutan, hal ini disebabkan karena flip-flop yang paling ujung dikendalikan oleh sinyal clock, sedangkan sinyal clock untuk flip-flop

lainnya berasal dari masing-masing flip-flop sebelumnya.

Counter Asinkron (Serial Counter) dan gambar 3.2 menunjukkan Counter Sinkron (Parallel Counter).

Gambar 3.1 : Counter Asinkron

Gambar 3.2 : Counter Sinkron 3.2 Flip-flop

flip-flop (multivibrator bistabil) mempunyai keluaran tegangan rendah (0) atau tinggi (1). Keluaran ini tetap rendah atau tinggi selama belum ada masukkan yang merubah keadaan tersebut. Rangkaian yang bersangkutan harus di-drive (dikendalikan) oleh satu masukkan yang disebut pemicu (trigger). Keadaan tersebut akan berubah kembali bila ada masukkan pemicu lagi.

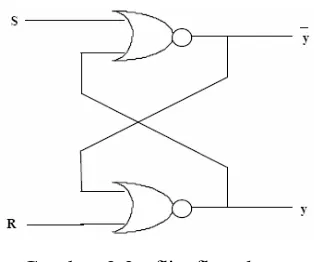

Pada gambar 3.3 dapat dilihat rangkaian dasar memori satu bit yang terdiri dari dua buah gerbang NOT (gerbang NAND masukan tunggal) Nand1 dan Nand2, keluaran dari suatu gerbang diumpan balikkan ke masukan pada gerbang yang lain. Kombinasi umpan balik ini disebut dengan flip-flop.

Gambar 3.3 : flip-flop dasar

Salah satu jenis flip-flop adalah flip-flop RS. Flip-flop ini mempunyai dua masukan dan dua keluaran, di mana salah satu keluarannya (y) berfungsi sebagai komplemen. Sehingga flipflop ini disebut juga rangkaian dasar untuk membangkitkan sebuah variabel beserta komplemennya. Flip-flop RS dapat dibentuk dari kombinasi dua gerbang NAND atau kombinasi dua gerbang NOR.

PERTAMA R S = 0 0

Ini berarti tidak diterapkan pemicu. Dalam hal ini keluaran y mempertahankan nilai terakhir yang dimilikinya.

KEDUA R S = 0 1

Ini berarti bahwa suatu pemicu diterapkan pada masukan S. Hal ini mengeset flip-flop

dan menghasilkan keluaran y bernilai 1.

KETIGA R S = 1 0

Ini menyatakan bahwa suatu pemicu diterapkan pada masukan R. Hal ini mereset

flip-flop dan menghasilkan keluaran y bernilai 0.

KEEMPAT R S = 1 1

merupakan kondisi masukan terlarang. Kondisi ini berarti menerapkan suatu pemicu ada

clock sperti terlihat pada gambar 3.4.

Gambar 3.4 : Diagram logika : (a) flip-flop RS (b) flip-flop RS ber 'clock'

Bila clock rendah (0), ke dua gerbang AND tertutup (disabled). Hal ini menjamin bahwa: R S = 0 0

yang berarti keluaran y tetap pada keadaan terakhir yang dimilikinya. Tetapi bila clock menjadi tinggi (1), ke dua gerbang AND terbuka (enabled). Hal ini memungkinkan sinyal-sinyal S dan R mencapai flip-flop RS. Dengan cara ini, flip-flop akan set atau reset, bergantung pada nilai RS.

Oleh sebab itu, flip-flop RS ber-'clock' tidak dapat berubah keadaan sampai berlangsungnya sinyal clock.

Penerapan clock pada sebuah flip-flop seperti di atas sangat penting dalam sistem digital berskala besar dengan beratus-ratus flip-flop yang dihubungkan satu sama lain. Clock diterapkan pada semua flip-flop secara serentak; hal ini menjamin bahwa semua flip-flop berubah keadaan pada saat yang sama. Penyerempakan ini sangat penting dalam berbagai sistem digital.

3.3 State Machine

State machine merupakan konstruksi logika yang digunakan untuk mendefinisikan sifat sistem yang sederhana. State machine menggunakan kombinasi

latch dan gerbang logika untuk sistem yang mempunyai memori. State machine di gambarkan dengan state diagram yang didefinisikan dari state transition table. Contoh

Gambar 3.5 : state machine

State machine dapat diklasifikasikan menjadi 2 tipe :

a. output nya tergantung pada present state yang dikenal dengan Moore machine

seperti yang terlihat pada gambar 3.6.

b. output yang merupakan kombinasi present state dan input yang lebih dikenal dengan Mealy machine, seperti yang terlihat dari 3.7.

Gambar 3.6 : Moore machine

Gambar 3.7 : Mealy machine

Present state di definisikan pada output memori. Beberapa contoh aplikasi state machine dapat dilihat pada embedded computing system, dimana komputer dirancang untuk menunjukkan beberapa tugas tertentu, seperti lampu merah atau elevator yang bisa dirancang dengan menggunakan pendekatan state machine.

Untuk lebih jelasnya lihat contoh berikut display bilangan prima atau penjumlahan naik atau turun. Pertama yang perlu diperhatikan adalah memahami definisi

state. Diagram dibawah menunjukkan counter mod-6, yang berguna untuk mengitung detik dan menit.

Gambar 3.8 : timing diagram counter mod-6

Misalkan A, B dan C adalah output dari suatu mesin, kemudian masing-masing transisi dari ”clock” di representasikan oleh garis putus-putus yang merupakan transisi dari satu state ke state berikutnya. Contoh diatas merupakan sequential finite state machine yang mempunyai 6 state : (000, 001, 010, 011, 100, 101) dan diulang kembali dari keadaan yang pertama yaitu 000. Langkah pertama yang dilakukan adalah mendefisinikan state dan transisis yang diinginkan seperti pada gambar 3.9.

Gambar 3.9 : State diagram

Dari gambar 3.9 dan contoh soal yang merupakan sederetan angka (atau biner 000, 001, 010, 011, 100, 101) yang terdiri dari 6 transisi, sehingga gambar 3.9 dirubah menjadi seperti gambar 3.10.

Gambar 3.10 : state diagram 000, 001, 010, 011, 100, 101

Gambar 3.11 : komponen diagram

Transisi diagram di representasikan dengan garis panah dari satu state ke state berikutnya. Langkah selanjutnya menentukan state table untuk state diagram seperti yang terlihat pada tabel 3.1.

Tabel 3.1 : state table

Langkah selanjutnya menentukan implementasi atau rancangan dimana keputusan ini tergantung dari masing-masing individu, dan juga terantung pada biaya atau komponen yang tersedia. Pada contoh perancangan ini menggunakan JK flip-flop sehingga sebelumnya dilihat terlebih dahulu tabel kebenaran JK flip-flop seperti yang terlihat pada tabel 3.2.

Tabel 3.2 : tabel kebenaran JK FF

Tabel 3.3 : tabel kebenaran

Langkah selanjutnya dari tabel kebenaran diatas diperoleh semua komponen dan untut

next step pada proses perancangan untuk menentukan input forming logic untuk masing-masing flip flop. Langkah selanjutnya dalam proses perancangan menentukan persamaan rangkaian digital dengan bantuan Peta-K, seperti yang terlihat pada gambar 3.12.

Gambar 3.12 : Peta-K

Dari peta-K dapat diperoleh persamaan rangkaian digital sehingga dapat digambar

schematic editor dan diperoleh simulasi dari rangkaian yang telah dirancang untuk dianalisa apakah hasil rangkaian seperti yang diharapkan. Untuk lebih jelasnya akan dibahas lebih detil pada bagian 3.4.

3.4 Perancangan Counter

Pada bagian ini akan dibahas langkah-langkah perancangan counter yang mengulang sederetan angka.

1. Rancang counter yang mengulang sekuens :

a. D Flip-flop

Langkah 1 : Membuat state diagram :

... ... ... ... ... ... ...

Gambar 3.13 : State diagram

Langkah 2 : menentukan tabel kebenaran berdasarkan state diagram diatas

Present next DA DB DC DD

Langkah 3 : memetakan tabel kebenaran ke dalam peta karnaugh DA :

DB :

AB CD

DC :

AB CD

DD :

AB CD

Langkah 4 : menentukan persamaan rangkaian digital DA = ...

DB = ... DC = ... DD = ...

Gambar 3.14 : Contoh Schematic editor counter dengan D-FF

Langkah 6 : simulasi hasil rangkaian

Gambar 3.15 : hasil simulasi counter dengan D-FF

Langkah 7 : analisa hasil rangkaian

Dari gambar 3.15 dapat dilihat bahwa counter yang telah dirancang dengan benar karena outputnya berupa sekuens :

0, 4, 12, 13, 6, 7, 2, 0, 4, 12, 13, 6, 7, 2, 0

b. JK Flip-flop

Langkah 1 : Membuat state diagram.

... ... ... ... ... ... ...

Gambar 3.16 : State diagram

Present next JA KB JB KB JC KC JD KD

JB :

AB CD

KB :

AB CD

JC :

AB CD

KC :

JD :

AB CD

KD :

AB CD

Langkah 4 : menentukan persamaan rangkaian digital JA = ... KA = ... JB = ... KB = ... JC = ... KC = ... JD = ... KD = ...

Langkah 5 : gambar persamaan rangkaian digital pada schematic editor

Langkah 6 : simulasi hasil rangkaian

Gambar 3.18 : hasil simulasi counter dengan JK-FF

Langkah 7 : analisa hasil rangkaian

Dari gambar 3.18 dapat dilihat bahwa counter yang telah dirancang dengan benar karena outputnya berupa sekuens :

0, 4, 12, 13, 6, 7, 2, 0, 4, 12, 13, 6, 7, 2, 0

2. Rancang counter yang mengulang sekuens : 0, 1, 2, 3, 7, 4, 0, 1, 2, 3, 7, 4, 0 . . . dengan menggunakan :

a. D-flip-flop

Langkah 1 : Membuat state diagram :

... ... ... ... ... ...

Gambar 3.19 : State diagram

Present next DA DB DC 0 0 0

0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1

Langkah 3 : memetakan tabel kebenaran ke dalam peta karnaugh DA :

AB CD

DB :

AB CD

DC :

Langkah 4 : menentukan persamaan rangkaian digital DA = ...

DB = ... DC = ...

Langkah 5 : menggambarkan persamaan rangkaian digital pada schematic editor

Gambar 3.20 : Contoh Schematic editor counter dengan D-FF

Langkah 6 : simulasi hasil rangkaian

Gambar 3.21 : hasil simulasi counter dengan D-FF

Langkah 7 : analisa hasil rangkaian

Dari gambar 3.21 dapat dilihat bahwa counter yang telah dirancang dengan benar karena outputnya berupa sekuens :

0, 1, 2, 3, 7, 4, 0, 1, 2, 3, 7, 4 b. JK-flip-flop

Langkah 2 : menentukan tabel kebenaran berdasarkan state diagram diatas Present next JA KB JB KB JC KC

0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1

Langkah 3 : memetakan tabel kebenaran ke dalam peta karnaugh JA :

AB CD

KA :

AB CD

JB :

KB :

AB CD

JC :

AB CD

KC :

AB CD

Gambar 3.23 : Contoh Schematic editor counter dengan JK-FF

Langkah 6 : simulasi hasil rangkaian

Gambar 3.24 : hasil simulasi counter dengan JK-FF

Langkah 7 : analisa hasil rangkaian

Dari gambar 3.24 dapat dilihat bahwa counter yang telah dirancang dengan benar karena outputnya berupa sekuens :

0, 1, 2, 3, 7, 4, 0, 1, 2, 3, 7, 4

3. Rancang counter yang mengulang sekuens :

0, 2, 3, 5, 7, 11, 13, 0, 2, 3, 5, 7, 11, 13 . . . dengan menggunakan :

a. D-flip-flop b. JK-flip-flop

a. D Flip-flop

Langkah 1 : Membuat state diagram :

... ... ... ... ... ... ...

Langkah 2 : menentukan tabel kebenaran berdasarkan state diagram diatas

Present next DA DB DC DD

Langkah 3 : memetakan tabel kebenaran ke dalam peta karnaugh DA :

DB :

AB CD

DC :

AB CD

DD :

AB CD

Langkah 4 : menentukan persamaan rangkaian digital DA = ...

DB = ... DC = ... DD = ...

Langkah 5 : menggambarkan persamaan rangkaian digital pada schematic editor

b. JK Flip-flop

Langkah 1 : Membuat state diagram.

... ... ... ... ... ... ...

Langkah 2 : menentukan tabel kebenaran berdasarkan state diagram diatas Present next JA KB JB KB JC KC JD KD

Langkah 3 : memetakan tabel kebenaran ke dalam peta karnaugh JA :

KA :

AB CD

JB :

AB CD

KB :

AB CD

JC :

KC :

AB CD

JD :

AB CD

KD :

AB CD

Langkah 5 : gambar persamaan rangkaian digital pada schematic editor

BAB IV

MENENTUKAN KEPUTUSAN

DENGAN BINARY COUNTER

OBYEKTIF :

- memahami bagaimana menentukan keputusan dengan binary counter

- mampu menggunakan state diagram untuk merancang rangkaian yang lebih kompleks

4.1 Menentukan keputusan dengan binary counter

Menentukan keputusan dengan Binary counter (Decision Making with Binary Counters) merupakan komponen state machine yang menggambarkan sifat finite state machine. Tidak semua state machine (state editor) diikuti oleh jalur (path) yang sama dari satu state ke state berikutnya seperti yang telah dibahas pada Bab IV. Keadaan state

memungkinkan untuk berinteraksi dengan mesin seperti vending machine yang mempunyai output yang berbeda-beda atau mempunyai dua kemungkinan berdasarkan tipe koin yang dimasukkan atau lampu merah yang mempunyai kemungkinan keadaan yang lebih dari satu ketika walk button ditekan/dijalankan.

Gambar 4.1 menunjukkan suatu mesin yang digambarkan dengan flowchart simbol state machine dan beberapa variabel, sehingga akan lebih mempermudah perancang untuk mendefinisikan pemecahan permasalahannya dan menuangkannya pada state table. 4.2 Perancangan Rangkaian dengan State Editor

Pada bagian ini akan membahas perancangan rangkaian digital dengan state editor dengan merancang 2 rangkaian yang memenuhi state diagram.

1. Merancang rangkaian digital yang memenuhi state diagram gambar 4.2, dimana rangkaian pertama menggunakan D flip-flop dan rangkaian kedua menggunakan JK flip-flop.

Gambar 4.2 : state diagram

a. perancangan menggunakan D flip-flop langkah 1 : menentukan state table

Present P Next DA DB DC

DA :

AB CD

DB :

AB CD

DC :

AB CD

langkah 3 : menentukan persamaan rangkaian digital berdasarkan K-map DA = ...

DB = ... DC = ...

b. perancangan menggunakan JK flip-flop langkah 1 : menentukan state table

Present P next JA KB JB KB JC KC 0 0 0

0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1

langkah 2 : memetakan state table pada karnaugh map

JA :

AB CD

KA :

JB :

AB CD

KB :

AB CD

JC :

AB CD

KC :

JA = ... langkah 4 : gambar rangkaian digital pada schematic editor

langkah 5 : simulasi rangkaian langkah 6 : analisa hasil rangkaian

2. Merancang rangkaian digital yang memenuhi state diagram gambar 4.3, dimana rangkaian pertama menggunakan D flip-flop dan rangkaian kedua menggunakan JK flip-flop.

Gambar 4.3 : state diagram

Present R S T Next DA DB DC 0 0 0

0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1

langkah 2 : memetakan state table pada karnaugh map DA :

AB CD

DB :

AB CD

DC :

langkah 3 : menentukan persamaan rangkaian digital berdasarkan K-map DA = ...

DB = ... DC = ...

langkah 4 : gambar rangkaian digital pada schematic editor

langkah 5 : simulasi rangkaian langkah 6 : analisa hasil rangkaian d. perancangan menggunakan JK flip-flop

langkah 1 : menentukan state table

Present R S T next JA KB JB KB JC KC

JB :

AB CD

KB :

AB CD

JC :

AB CD

KC :

langkah 3 : menentukan persamaan rangkaian digital berdasarkan K-map JA = ...

KA = ... JB = ... KB = ... JC = ... KC = ... langkah 4 : gambar rangkaian digital pada schematic editor

BAB V

OUTPUT FORMING LOGIC

OBYEKTIF :

- memahami fungsi output forming logic

- mampu menggunakan fungsi output forming logic untuk merancang rangkaian digital yang lebih kompleks

5.1Output Forming Logic

Output forming logic hampir sama dengan translasi pada counter akan tetapi

Output forming logic mempunyai fungsi lebih untuk perancangan yang glitch-free dan di gunakan untuk masukan yang lebih kompleks ke suatu dekoder yang merupakan basis rangkaian digital berdasarkan output.

Sebagai contoh penggunaan 3 bit sebagai kombinasi output dimana 3 bit membangkitkan (generate) single output atau multiple output. Counter mod 6 glitch free dengan keluaran sederetan angka 0, 1, 2, 3, 4 dan 5 dapat dibuat dengan menentukan output forming logic dengan menggunakan karnaugh map. Akan tetapi sebelumnya tentukan terlebih dahulu tabel translasi seperti yang terlihat pada tabel 5.1.

Gambar 5.1 : peta karnaugh

5.2Komponen-komponen Output Forming Logic

Pada bagian ini akan dijelaskan beberapa rangkaian-rangkaian pembangkit pulsa pada output forming logic.

Perhatikan gambar 5.2 dan gambar 5.3. a

Gambar 5.2 : state diagram Clock

Definisi-definisi transisi state : SB : State beginning SE : State End

DSB : Delayed State Beginning DSE : Delayd State End

DDSE : Double Delayed State End

Sebagai contoh dapat dilihat perancangan state diagram pada gambar 5.5 yang kemudian di translasi ke state translasi.

c

Gambar 5.5 : state diagram Tabel 5.2 : State Translasi

Dari tabel translasi dibuat K-map untuk menentukan persamaan rangkaian logikanya.

AB CD

DA = ...

AB CD

DB = ...

AB CD

DC = ...

Persamaan-persamaan yang diperoleh dari K-map digambar pada Schematic editor

D

Gambar 5.6 : Rangkaian digital

5.3Perancangan Rangkaian Digital mesin jamu pilih

Pada bagian ini akan dibahas suatu projek kecil yaitu membuat rangkaian digital suatu mesin jamu pilih, dengan permasalahan sebagai berikut :

Perancangan mesin jamu pilih atau mesin penjual jamu, dimana pembeli dapat memilih 4 jenis jamu, yaitu jamu ”gadis remaja”, ”srikaton”. ”awet ayu”, dan ”galian rapet” yang merupakan jamu-jamu perusahaan Nyonya Meneer. Jamu-jamu ini masing-masing berharga Rp. 1.000,- dan mesin ini dapat menerima uang logam Rp. 500,- ataupun uang logam Rp. 1.000,-. Dan jika pembeli ingin membatalkan transaksi meskipun telah memasukkan uang logamnya masih dapat dilakukan dan pembeli mendapatkan uang logamnya kembali.

forming logic (OFL). Proses selanjutnya menggambarkan hasil persamaan rangkaian digital yang diperoleh dan mensimulasikan rangkaian tersebut. Hasil simulasi dianalisa apakah rangkaian yang telah dibuat sesuai dengan yang diharapkan.

5.3.1 Identifikasi masalah

Permasalahan pada mesin jamu pilih dapat di nyatakan sebagai berikut: Sebagai input dinyatakan dengan :

- tidak ada kegiatan TA

- untuk pengembalian D

- memasukkan uang logam Rp. 500,- E Sebagai output dinyatakan dengan :

- mengeluarkan uang kembali V - mengeluarkan jamu gadis remaja W - mengeluarkan jamu srikaton X - mengeluarkan jamu awet ayu Y - mengeluarkan jamu galian rapet Z

5.3.2 Identifikasi State

Keadaan-keadaan dengan kemungkinan-kemungkian : State a : 1. tidak ada kegiatan, menuju kembali ke state a 2. memasukkan uang Rp. 500,- menuju ke state b

3. memasukkan uang Rp. 1.000,- menuju ke state c State b : 1. tidak ada kegiatan, menuju kembali ke state a

State c : 1. tidak ada kegiatan, menuju kembali ke state c

2. menekan tombol input uang kembali, menuju ke state b

3.menekan tombol pilihan bahan I, mesin mengeluarkan bahan I, kemudian kembali ke state a

4.menekan tombol pilihan bahan II, mesin mengeluarkan bahan II, kemudian kembali ke state a

5.menekan tombol pilihan bahan III, mesin mengeluarkan bahan III, kemudian kembali ke state a

6.menekan tombol pilihan bahan IV, mesin mengeluarkan bahan IV, kemudian kembali ke state a

State d : 1. uang keluar, dan kembali ke state a

5.3.3 State diagram

5.3.4 tabel kebenaran

Dan tabel kebenarannya adalah sebagai berikut :

PRESENT INPUT NEXT

5.3.5 Pembentukan Input Forming Logic (Ifl)

Dengan melakukan penyederhanaan yang dilakukan dengan mempergunakan K-map akan diperoleh persamaan Input Forming Logic,yaitu input pada flip-flop. Selain D-flip-flop. Selain D-flip-flop dapat juga dipergunakan JK-D-flip-flop.

Sehingga di peroleh :

DA = ... DB = ... DC = ...

Langkah selanjutnya menentukan persamaan rangkaian dari output forming logic.

5.3.7 Schematic Editor mesin jamu pilih

Persamaan yang diperoleh dari output forming logic di gambar pada schematic editor.

5.3.8 Simulasi rangkaian mesin jamu pilih Gambar schematic editor di simulasikan.

5.3.9 Analisa hasil rangkaian

DAFTAR PUSTAKA

Anonim, Xilinx Programmable Logic Data book, Xilinx, Inc, San Jose, CA.

Anonim, Foundation Series 2.1i User Guide, http://toolbox.xilinx.com/docsan/2_1i/ 25 January 2004.

Brian Warneke, The CUPL Environment,

http://www.rexfisher.com/Downloads/CUPL%20Tutorial.htm , 9 Januari 2004.

D. Van den Bout, "The Practical Xilinx Designers Lab Book 1.5", Prentice Hall, Upper Saddle River, 1999.