PERCOBAAN DAC TANGGA R-2R

( DAC

–

0808 )

Oleh : Sumarna, Jurdik Fisika, FMIPA, UNY

E-mail : [email protected]

A. TUJUAN

1. Mempelajari cara kerja DAC yang menggunakan metode Tangga R-2R.

2. Merancang rangkaian DAC-0808.

3. Menggunakan DAC-0808.

B. ALAT DAN BAHAN

1. Catu daya ganda (-12 volt, 0 volt, dan +12 volt, serta +5 volt),

2. Voltmeter digital,

3. Rangkaian DAC-0808 (DAC-0808, LM-741)

4. Kabel penghubung.

C. KAJIAN TEORITIK

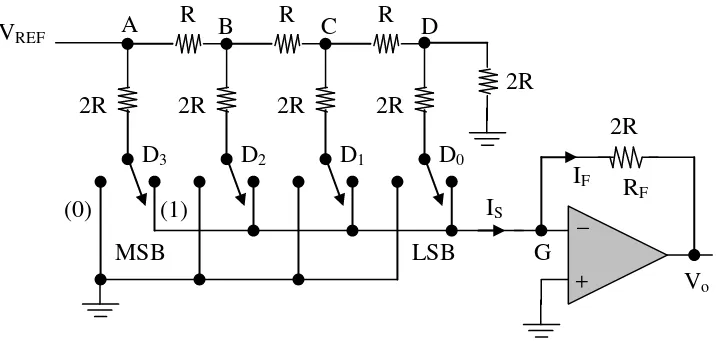

Metode yang sering digunakan dalam rangkaian terpadu (IC) DAC

adalah rangkaian tangga R/2R. Rangkaian itu hanya menggunakan dua nilai

resistor. Rangkaian tersebut, yang dirancang dalam formasi tangga,

merupakan cara cerdas untuk membentuk rangkaian pembagi arus yang

terbobot biner. Pada setiap titik cabang arus terbagi dua sama besar.

Dengan demikian sangat mudah untuk membuat rangkaian DAC dengan

resolusi yang relatif tinggi atau cacah bit yang relatif besar seperti 8 bit, 10

sepasang resistor R/2R dan saklar pada anak tangga MSB. Perhatikan

gambar berikut !.

Informasi digital (word) 4 bit yang akan dikonversi ke analog

dimasukkan melalui saklar D3 s/d D0 (dalam kenyataannya, saklar tersebut

tersusun dari transistor). Jika saklar pada poisis 1, maka akan menyebabkan

arus mengalir melalui resistor RF yang proporsional dengan nilai ekivalen

binernya. Arus pada setiap saklar bernilai dua kali dari LSB-nya atau

setengah kali dari MSB-nya.

Masukan (-) dari Op-Amp berada pada tanah maya (G) sehingga

sembarang arus yang mencapai titik tersebut akan diteruskan menuju RF.

Dengan demikian dapat ditentukan bahwa resistor tangga dan arus yang

melalui anak tangga tidak dipengaruhi oleh posisi saklar (D3 s/d D0). Hal ini

disebabkan karena :

1. Ketika suatu saklar pada posisi 0, ujung bawah resistor 2R pada saklar

itu terhubung ke tanah (ground).

2. Ketika suatu saklar pada posisi 1, ujung bawah resistor 2R pada saklar

itu terhubung ke tanah maya (G) yang berkelakuan sebagai tanah

(ground).

VREF

2R

+ _

Vo

RF

IF

G

R R R

D0

D1

D2

D3

2R 2R

2R 2R

2R

MSB LSB

D

A B C

IS

Untuk menghitung arus yang disumbangkan olah setiap anak tangga,

pertama kali harus dihitung arus total yang meninggalkan VREF. Dengan

menyederhanakan rangkaian resistor pada setiap bagian anak tangga dari

LSB, akan diperoleh 2R yang paralel dengan 2R, yang menghasilkan R. R

ini terhubung seri dengan R antara titik C dan D. Prosedur ini diteruskan

untuk seluruh anak tangga sampai dengan siperoleh resistansi total, yaitu sama dengan R, yang “terlihat” oleh VREF. Dengan demikian arus total yang

meninggalkan VREF sebesar VREF / R. Perhatikan gambar berikut !.

Ternyata, setiap arus cabang sama dengan setengah dari arus sebelumnya

dan membentuk proporsi yang terbobot biner yang kemudian disumbangkan

untuk resistor RF pada Op-Amp. Ketika saklar pada posisi 1, maka arus

dilewatkan pada RF dan memberikan sumbangan tegangan pada Vo . Jika

saklar pada posisi 0, maka arus dilewatkan langsung ke tanah (ground) dan

tidak menyumbangkan tegangan ke Vo . Jika nilai komponen pada rangkaian

DAC seperti pada gambar berikut, maka arus total yang meninggalkan VREF

sebesar VREF / R sama dengan 500 A. Setelah sampai di titik A, arus

tersebut dibagi dua menjadi 250 A yang masing-masing mengalir menuju B

VREF

A 2R

D 2R

R

2R

R

2R

R

2R B

C

Ketika arus dari VREF

mencapai titik A akan terbagi

dua sama besar karena setiap

cabang setara dengan 2R.

Arus yang mencapai titik B

jterpecah menjadi dua sama

besar. Prosedur pemecahan

arus ini terjadi terus-menerus

Besar sumbangan arus masing-masing saklar (D3 s/d D0) kepada Vo adalah

DAC 4 bit tersebut di atas mempunyai 24 = 16 kombinasi biner dari status

saklar D3 s/d D0 . Setiap kombinasi membentuk bilangan biner Bin. Tegangan

keluaran total Vo dari masukan sembarang kombinasi biner pada DAC 4 bit

dapat ditentukan dengan persamaan :

Vo = - (VREF x 8

in

B

).

Hubungan antara keadaan masukan biner dan tegangan keluaran pada DAC

4 bit seperti contoh di atas adalah sebagai berikut :

1. Susunlah rangkaian DAC seperti gambar di atas, di mana voltmeter

digital dipasang pada saluran Vo (pin 6 pada IC LM-741) untuk

mengetahui tegangan keluarannya. Pastikan sambungannya benar !

2. Kenakan status/keadaan logik pada setiap saluran masukan (B7 B6 B5 B4

B3 B2 B1 B0) sedemikian hingga membentuk word-biner yang tegas, di

mana status logik 0 suatu saluran benar-benar dikenakan pada ground

dan status logik 1 dikenakan pada +5 volt.

3. Selidiki untuk semua status logik yang mungkin. Untuk setiap status logik

masukan (word biner) kemudian ukurlah tegangan keluran Vo. Masukkan

hasilnya ke dalam tabel berikut !

Word-biner V

o

( mV ) B7 B6 B5 B4 B3 B2 B1 B0

0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 1

0 0 0 0 0 0 1 0

0 0 0 0 0 0 1 1

0 0 0 0 0 1 0 0

0 0 0 0 0 1 0 1

Dst.

1 1 1 1 1 1 0 1

1 1 1 1 1 1 1 0

1 1 1 1 1 1 1 1

4. Berdasarkan hasil pengamatan langkah 3), buatlah grafik yang

menunjukkan hubungan antara tegangan keluaran (Vo) dengan word

biner (B7 B6 B5 B4 B3 B2 B1 B0).

5. Tentukanlah resolusi dan linieritas DAC tersebut !

6. Informasi apa saja yang dapat Anda peroleh setelah mengamati dan

menganalisis grafik dan data percobaan ? Jelaskan !