Fasilkom UI – 2005 Versi: 2.2

Fakultas Ilmu Komputer Universitas Indonesia

Review Memory Systems &

Technology Trends

Johny Moningka ([email protected])

OSK/JM-2005/V2.2/2

Overview

Review: Memory Technology

Apa yang seharusnya anda ketahui

• Kuliah sebelumnya: prinsip dasar kerja cell & jenis memory, organisasi chips memory etc.

Teknologi Trends: benchmark (memory access)

• SDRAM, DDR SDRAM, RDDRAM.

Review: Memory Hierarchy

Prinsip dasar rancang bangun semua sistim memori

komputer

OVERVIEW:

1. Fokus utama pada pengantar kuliah “Sistim Memori” adalah melakukan review materi yang telah didapat pada kuliah sebelumnya mengenai teknologi memori. 2. Review diberikan dengan memberikan prespektif dan wawasan bahwa suatu

komponen dan orgnisasinya dalam sistim komputer tidak beridiri sendiri tapi merupakan integrasi yang sinambung untuk mendukung komponen yang lain. 3. Jika pada bagian sebelumnya telah dibahas peningkatan dan teknik organisasi

komponen CPU sehingga meningkatkan kinerja (performance) CPU lipat dua setiap tiga tahun, maka pembahasan selanjutnya bagaimana organisasi memori direalisasikan supaya dapat mendukung CPU yang cepat.

4. Secara khusus bagian ini juga memberikan tinjauan dasar dan ide dari seluruh sistim memori dalam dunia komputasi yang bertumpu pada model hirarkis.

OSK/JM-2005/V2.2/3

Memory Technology: Terminology (1/2)

Ditinjau dari cara akses, memori dibagi:

Random Access:

• “Random” is good: waktu akses sama untuk semua address memory

• Pengertian akses dapat dilakukan pada semua lokasi data (data availabile, dgn waktu akses sama).

• Tipikal: semikonduktor memori (tanpa ada latency mekanis).

“Non-so-random” Access Technology:

• Waktu akses tergantung lokasi dan kapan di akses. • Terdapat lokasi dimana diperlukan search data (mis.

head pada disk)

Sequential Access Technology: access time linear in

location (e.g., tape)

WAWASAN:

1. Ditinjau dari cara dan waktu akses maka memory atau storages data untuk komputer dapat dibagi atas random, mendekati random, dan linear.

2. Random tidak berarti “acak” tapi merupakan konsep dimana kita dapat

mengakses lokasi yang acak (any address, any time) dan waktu akses adalah sama. Umumnya dalam bentuk semikontukdor memori, sehingga dikenal nama, RAM = Random Access Memory, dalam bentuk berbagai produk, seperti

Dynamic RAM, Static RAM, Flash RAM/Disk.

3. Produk memori yang lain untuk kapasitas besar memerlukan bantuan penyimpanan (media) yang lebih besar dalam bentuk magnetis sehingga

permukaan media tersebut cukup luas untuk diakses dan diperlukan pergerakan “head” untuk menentukan lokasi data, sehingga walaupun terdapat perbedaan waktu yang sangat kecil tapi terdapat waktu tunggu yang menjadi ciri khas jenis memory tersebut. Dalam kategori ini adalah hard-disk, CD-ROM dll.

4. Terdapat akses yang sangat bervariasi menyolok tergantung lokasi data seperti pada gulungan pita tape, mendekati linear, karena perlu search yang umumnya dari awal (tidak dapat dilakukan secara “random”).

OSK/JM-2005/V2.2/4

Memory Technology: Terminology (2/2)

Ukuran kinerja memory

Access time

• Waktu interval antara request data dibaca (ditulis) dan data tersebut deliver (stored)

Cycle time

• Waktu antara memori tersebut diakses, sampai waktu memori tersebut dapat diakses lagi.

• Waktu antara request

Examples: Disk, CDROM

Bandwidht (throughput)

• Rate dimana data dapat ditransfer dari/ke memory

Latency = cycle time + access time

DASAR:

1. Kinerja sistim memori berbeda dengan CPU (seberapa cepat instruksi dijalankan), tapi lebih bersifat seberapa cepat data dapat dibaca atau ditulis. 2. Secara historis storage system (DRAM pada sistim komputer mainframe,

super-komputer etc., disk dll) kinerja sistim tersebut, ditentukan dua faktor utama, yakni cycle time dan bandwidth.

3. Misalkan: Cycle time sangat berpengaruh pada sistim memori DRAM konvensional (mis. EDO RAM,), karena diperlukan selang waktu tertentu (stabilized state dari rangkaian elektronik) untuk dapat mengakses memory kembali. DRAM cycle time membatasi seberapa sering kita dapat mengakses memori.

4. Uktuk access time: EDOR RAM: 50 ns, Tipikal SDRAM 2 clock cycles => 20 ns (Collumnt AT)+ 7 ns

Note: Saat ini rancangan semikonduktor memory secara keseluruhan telah membungkus kelemahan latency tersebut dalam bentuk memory module (controller, memory chipset) yang mengakses secara “burst” semua bit selanjutnya dari data dan melakukan transfer ke CPU sesuai dengan clock rate memory tsb. Jadi misalkan clock rate 100 MHz, maka Synchronous DRAM dapat memberikan clock cycle time untuk burst 10ns (bandingkan dgn chips DRAM => 50 ns).

Sering pada marking chips SDRAM, terdapat variasi tergantung kualitas produk chips, misalkan -12, (setara 12 ns) cocok utk clock 66 MHz, atau, -8 (mampu sampai 125 MHz) dapat digunakan pada clock 100 MHz system. Kemudain dibuat standar PC100 utk comply deng 100 MHz, dan PC133 dengan 133 MHz (setara dgn chips -6).

OSK/JM-2005/V2.2/5

Semiconductor RAM

Key features

Dalam bentuk package chips (semikonduktor memory)

Basic storage unit: cell (satu bit per cell)

Multipe RAM chips membangun sistim memory

SRAM: Static Random Access Memory

Low density, high power, expensive, fast

Static: content will last (until lose power)

DRAM: Dynamic Random Access Memory

High density, low power, cheap, slow

Dynamic: need to be “refreshed” regularly

DASAR:

1. SRAM (Static RAM), digunakan pada cache memory, atau kebutuhan memory kecil dengan akses yang cepat. Bit disimpan pada konfigurasi flip-flop transistor (4 - 6 transistor per bit), tidak perlu refresh, tapi tetap volatile.

2. Karena menggunakan transistor untuk menyimpan bit informasi, relatif “kebal” (insensitives) terhadap gangguan (noise) elektronis.

3. Karakteristik utama: Kecepatan: 8 s/d 16 kali lebih cepat dari DRAM, tapi cost 100x lebih mahal. 4. SRAM karena stabil dan tidak perlu refresh tegangan, banyak digunakan untuk devices yang

“low power” seperti HP, PDA, dimana daya baterai sangat terbatas utk terus menerus mencatu kapasitor DRAM..

5. DRAM (Dynamic Random Access Memory), digunakan pada main memory. Informasi disimpan pada kapasitor (tegangan). Sifat volatile diperlukan refresh secara berkala tegangan kapasitor tsb setiap 10 – 100 ms.

6. Karena menggunakan kapasitor lebih sensitif terhadap gangguan noise. Lebih lambat dari SRAM tapi kapasitannya lebih besar.

7. Karakteristik utama: Densitas tinggi (1 transistor per 1 bit) dan kapasitas besar (cost per bit rendah). Alasan ini menyebabkan DRAM menjadi pilihan teknologi untuk main memory yang memerlukan kapasitas besar dan low cost.

OSK/JM-2005/V2.2/6

Non-volatile Memories

DRAM & SRAM adalah volatile memory

Informasi hilang jika “powered off”

Non-volatile memory tetap menyimpan informasi

walaupun “powered off”

Generik: ROM (Read Only Memory), walaupun terdapat

jenis ROM yang dapat diubah (write).

Jenis ROM:

Programmable ROMs (PROM)

Eraseable Programmable ROM (EPROM)

Flash Memory

WAWASAN:

1. DRAM & SRAM adalah “volatile”, data hilang jika tegangan listrik hilang. 2. Terdapat jenis memory semikonduktor yang sifatnya “non-volatile”. Secara

historis namanya dikategorikan ROM (Read Only Memory), walaupun dalam perkembangannya ROM dapat juga ditulis (update).

3. Suatu programmable ROM (PROM) dapat diprogram sekali saja, sedangkan EEPROM (electical EPROM) dapat dihapus dan diprogram lagi. Flash memory adalah istilah yang digunakan untuk jenis non-volatile memory (EPROM) dalam bentuk “card” untuk digunakan pada laptop, video game dsb.

4. Sering program kecil yang berada di ROM, disebut firmware (sebagai pilihan dari istilah software).

5. Dengan sifat non-volatile maka pemakaian yang terbesar dari ROM adalah menyimpan program pada memory yang cepat untuk digunakan oleh komputer saat dihidupkan (boot).

6. Misalkan PC, menyimpan boot dan BIOS (basic input/output systems) dalam ROM. BIOS adalah rutin sederhana untuk kontrol devices hardware. Devices lain seperti graphics card, disk drives, mempunyai juga firmware untuk

REVIEW:

1. Gambaran sekilas perkembangan performance teknologi mikro-prosesor dibandingkan dengan memori dalam kurun waktu tahun 1980 – 2000.

Y-axis adalah performance (skala logarithmic) dalam hal “latency” dari kedua komponen utama komputer.

X-axis adalah tahun perkembangan teknologi CPU dan memory.

2. Base-line untuk memory: 64 KB DRAM, dengan perkembangan 7% per-tahun dalam hal latency (access time). Sedangkan CPU dapat diasumsikan 35% per-tahun (sampai 1986), dan 55% per-tahun untuk seterusnya.

3. Untuk memory adalah peningkatan kinerja dalam penurunan “access time”, sedangkan CPU adalah peningkatan kinerja dalam penurunan waktu eksekusi instruksi.

4. Dalam gambar ini terjadi ketimpangan (gap) dimana CPU jauh lebih cepat peningkatan kinerja dibandingkan memory, sehingga kemungkinan CPU akan idle (menunggu data dari memori).

5. Hal ini menjadikan peningkatan kinerja CPU (clock rate dll) merupakan faktor yang semakin kecil pengaruhnya (“diminishing factor”) dalam keseluruhan kinerja sistim komputer. OSK/JM-2005/V2.2/7 µProc 55%/yr. DRAM 7%/yr.

1

10

100

1000

1980 1981 1983 1984 1985 1986 1987 1988 1989 1990 1991 1992 1993 1994 1995 1996 1997 1998 1999 2000 DRAM CPU 1982 Processor-Memory Performance Gap: (grows 50% / year)Performance

Time

Processor-DRAM Memory Gap (latency)

OSK/JM-2005/V2.2/8

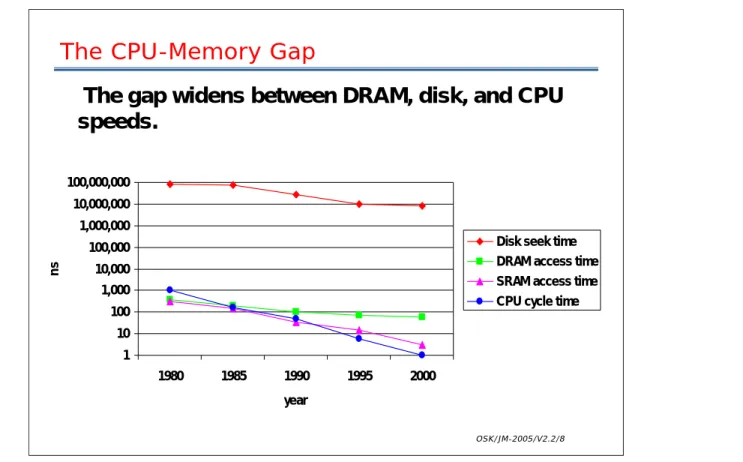

The CPU-Memory Gap

The gap widens between DRAM, disk, and CPU

speeds.

1 10 100 1,000 10,000 100,000 1,000,000 10,000,000 100,000,000 1980 1985 1990 1995 2000 year nsDisk seek time DRAM access time SRAM access time CPU cycle time

Tabel di atas memberikan gambaran secara kuantitatif perbandingan peningkatan performance (kecepatan) dari komponen komputer: logic (CPU), DRAM dan disk dalam kurun waktu 1980 - 2000.

Y-axis, menggambarkan “latency” dari komponen komputer sebagai satuan ukuran kinerja dalam nano-detik (ns), dalam skala log.

X-axis, adalah waktu (tahun).

1. Pengertian CPU cycle time: seberapa cepat (waktu) instruksi dapat diberikan ke CPU (kecepatan CPU menerima dan menjalankan instruksi). Data historis, Pentium III (600 MHz, tahun 2000) mempunyai cycle time: 1,5 ns; bandingkan dengan 8086 (prosesor x86) mempunyai CPU cycle time: 1000 ns.

2. Chip DRAM, hanya menurun latency dari 375 ns (tahun 1980) dan 60 ns (tahun 2000). Dengan kata lain terdapat perbandingan peningkatan kinerja CPU dan memory, adalah 600 : 11.

Tahun 1980, chip DRAM dengan kapasitas terbesar yang dapat anda beli adalah 64Kb, dengan “cycle time” sekitar 250 ns.

Tahun 1995, terdapat 64 Mb DRAMs chips, dengan kapasitas 1000x dan kecepatan 2 kali lebih cepat.

Secara historis kapasitas DRAM meningkat 4 kali dalam kurun waktu 3 tahun, tapi “cycle time” DRAM, hanya meningkat 2 kali dalam 10 tahun.

3. Ini berarti kecepatan DRAM relatif terhadap prosesor menjadi makin hari makin lambat.

TRENDS:

1. Teknologi DRAM mengalami perubahan sejak Intel mengadopsi SDRAM (Synchronous DRAM) untuk arsitektur PC, tahun 1996. Sebelumnya terdapat Fast Page Mode (FPM) DRAM

(Asyncrhonous DRAM). Asynch. DRAM saat ini masih digunakan untuk upgrade “sistim yang lama” dan tahun 2001, akan mengalami phase out.

2. Sesuai dengan namanya SDRAM disinkronkan dengan pulsa clock, sehingga tidak diperlukan “control lines” (seperti Asynch. DRAM) dalam berkomunikasi/sinkronisasi dengan memory controller. Dengan cara ini penyampaian bit data dapat dilakukan secara “burst mode”, menurunkan “access time”.

3. Intel mengeluarkan dua standar PC100 dan PC133 untuk SDRAM (simbol 100 dan 133 menunjukkan clock). Jadi ukuran kecepatan akses ditentukan oleh clock mis. PC100,

mempunyai clock 100 MHz (dianggap setara dengan 10 ns). Perkembangan teknologi SDRAM terbentur pada peningkatan clock (harus sinkronus), dengan clock makin tinggi terdapat pada keterbatasan rangkaian sinyal/listrik dalam bandwidth memory yang lebar.

.

Note: SDRAM Pipelining means that the chip can accept a new command before it has finished processing the previous one. In a pipelined write, the write command can be immediately

followed by another command without waiting for the data to be written to the memory array. In a pipelined read, the requested data appears a fixed number of clock pulses after the read

command. It is not necessary to wait for the data to appear before sending the next command. This delay is called the latency and is an important parameter to be considered when purchasing SDRAM for your computer.

• SDRAM was introduced in 1997, and by the 2000s had replaced plain DRAM in modern computers, because of its greater speed.

OSK/JM-2005/V2.2/9

Memory Technology: DRAM (1/2)

Sinkronus DRAM (SDRAM)

Kecepatan memori bus meningkat dari 66 MHz,

menjadi 100 MHz, 133 MHz

Interface baru chipset (controller):

• transfer/latch data secara sinkronus (burst) dari/ke CPU (dikenal: 100 Mhz setara dgn 10 ns).

Double Data Rate DRAM (DDR SDRAM)

Interface sama seperti SDRAM, hanya memanfaatkan

“edge/trigger clock” naik dan turun => 2 sinyal pada 1 clock

• Secara efektif clock 100 MHz => 2 x 100 MHz => 200 MHz

OSK/JM-2005/V2.2/10

Memory Technology: DRAM (2/2)

Saat ini trend teknologi “main memory” dikuasai

oleh DDR SDRAM (open standar JEDEC)

Chip specification

DDR-333: DDR-SDRAM - 166 MHz

DDR-400: DDR-SDRAM - 200 MHz

Stick/module specification

PC-2700: DDR-SDRAM using DDR-333 chips,

2.667 GByte/s bandwidth per channel

PC-3200: DDR-SDRAM using DDR-400 chips,

3.200 GByte/s bandwidth per channel

From Wikipedia, the free encyclopedia.

DDR SDRAM or double-data-rate synchronous dynamic random access memory is a type of memory integrated circuit used in computers. It achieves greater bandwidth than ordinary SDRAM by

transferring data on both the rising and falling edges of the clock signal (double pumped). This effectively nearly doubles the transfer rate without increasing the frequency of the front side bus. Thus a 100 MHz DDR system has an effective clock rate of 200 MHz when compared to equivalent SDR SDRAM, the “SDR” being a retrospective designation.

With data being transferred 8 bytes at a time DDR RAM gives a transfer rate of (memory bus clock rate) × 2 (for dual rate) × 8 (number of bytes transferred). Thus with a bus frequency of 100 MHz, DDR-SDRAM gives a max transfer rate of 1600 MB/s.

JEDEC has set standards for speeds of DDR SDRAM, divided into two parts: The first specification is for memory chips and the second is for memory modules.

Direct Rambus DRAM (DRDRAM)

Direct Rambus DRAM (DRDRAM), often called RDRAM, is internally similar to DDR SDRAM, but uses a special method of signaling developed by the Rambus Company that allows faster clock speeds. RDRAM chips are packaged on modules called RIMMs, which are not compatible with the DIMMs used for plain SDRAM. Intel licensed the Rambus technology and introduced chipsets with RDRAM support. Early P4 systems could only use RDRAM, but as prices remained high, Intel finally introduced support for DDR. (The company VIA had a DDR chipset for the Pentium 4 before this, but legal threats put motherboard manufacturers off using it. VIA then decided to make their own boards with the chipset but these didn't gain much traction either) RDRAM all but disappeared in new systems around 2003, due to the availability of DDR chipsets for the Pentium 4 and the lower cost of SDRAM. Sony used RDRAM in its PlayStation 2 video game console, and announced it would use Rambus's XDR memory in its PlayStation 3, expected in 2006.

OSK/JM-2005/V2.2/11

Memory Technology: DRAM (3/3)

Dual Channel DDR

Platform => dua kanal memory module dapat diakses

oleh CPU sekaligus.

Terintegrasi dgn sistim chipset (motherboard).

Rambus (RDRAM)

Protocol based => asinkronus (proprietary Intel dan

Rambus Inc.)

Interface baru dalam bentuk chips controller dengan

clock rate yang lebih tinggi dari SDRAM.

Proprietary: mahal dan tidak mendapat dukungan dari

industri

Tidak banyak dukungan lagi, setelah Intel terpaksa

mendukung DDR DRAM pada Pentium 4.

TRENDS:

1. Terminologi dual channel DDR sebenarnya tidak berdiri sendiri dalam kontek komponen/modul memori DRAM, tapi merupakan suatu platform rancangan chipset (motherboard) dimana dimungkinkan dua kanal memori yang memberikan data secara serentak ke CPU, jadi terdapat peningkatan pada besaran kinerja “bandwidth” dari gabungan kedua modul tersebut. Solusi ini merupakan pilihan terbaik dibandingkan meningkatkan clock rate yang cukup tinggi pada modul memori SDRAM. Perkiraan peningkatan kinerja secara keseluruhan tidak mencapai 2x lipat tapi hanya berkisar 10% s/d 20%.

2. Rambus (nama perusahaan) mengubah interface DRAM dengan menggunakan bus (tanpa RAS/CAS) dan terdapat chip controller untuk akses/referesh dll. Dengan konsep bus, clock Rambus dapat mencapai 400 MHz.

3. Tahun 2001, Intel mengumumkan bahwa hanya Rambus yang akan digunakan untuk P4, tapi mengubah keputusannya dengan mendukung DDR SDRAM, dengan mengeluarkan chipset i845 yang mendukung DDR SRAM pada P4, setelah mendapat tekanan dari berbagai produk chipset komersial lain VIA etc. yang lebih dulu menggunkan DDR SRAM utk P4.

4. Trend memori teknologi untuk tahun 2004 dst, akan didominasi oleh DDR SDRAM, dan semakin berkurang pemakaian SDRAM konvensional. Rambus mengalami setback dalam masalah cost yang lebih mahal dari DDR SDRAM dan dukungan vendor (proprietary technology), tapi tetap dapat menjadi alternatif teknologi memori untuk masa depan.

OSK/JM-2005/V2.2/12

Recap. Memroy Property: fast, cheap & big

Fakta teknologi memory (tipikal PC):

Static RAM: access time: 1-2 ns; size: 256K

SDRAM: access time: 20 ns – 100 ns: size 1024 MB

Hard-disk (Disk): access time: 5 ms – 10 ms;

size: 40 – 200 GB

Tape/Network: access time: > 10 ms; size > 1000 GB

Fakta & cost:

Memori dengan akses cepat => kapasitas kecil

Memori dengan kapasitas kecil => high cost

Memory dengan kapasitas besar dan “low cost”, pasti

lambat,

Bagaimana membuat sistim memori yang besar,

murah dan cepat (… most of the time)?

WAWASAN:

1. Melihat gap kecepatan antara CPU, DRAM dan disk (slides selelumnya), terdapat issue dalam organisasi sistim komputer untuk mengurangi jurang ini. 2. Fakta teknologi storages/memory yang ada saat ini memperlihatkan kapasitas

dan cost yang termurah ($/MB) dimiliki oleh memory dengan waktu akses paling lambat. Kapasitas storages data yang besar (penting untuk “program” dan data) menjadi issue karena program (OS, dan program aplikasi) mempunyai

kecenderungan makin besar.

3. Tantangan yang ada dalam organisasi sistim memory/storages komputer adalah mencapai ketiga parameter: cepat, murah dan besar. Secara individual

teknologi komponen memory, mis. SRAM, DRAM, disk atau tape) tidak dapat mencapai ketiga parameter di atas.

4. Jadi walaupun terdapat asumsi bahwa programmer akan menggunakan memory tanpa batas, terdapat solusi ekonomis yang memanfaatkan prinsip lokalitas ini dikaitkan dengan cost/performance komponen memory (storages) yang kita pelajari sebelumnya.

5. Dalam slides selanjutnya akan diperlihatkan bagaimana organisasi komputer modern saat ini dapat mencapai (almost) ketiga parameter tersebut.

OSK/JM-2005/V2.2/13

Locality of Programs

Principle of Locality:

Program cenderung menggunakan kembali (reuse)

data dan instruksi yang sebelumnya digunakan (recently)

Temporal locality: Recently referenced items are likely to be referenced in the near future.

Spatial locality: Items with nearby addresses tend to be referenced close together in time.

Umumnya instruksi (code program) mempunyai

karakteristik kedua locality tsb

Structured programming: flow program

Procedure call

PRINSIP:

1. Salah satu faktor penting dalam sistim komputer adalah sifat atau karakteristik program. Terdapat karakteristik umum untuk program (aplikasi), dimana

program cenderung menggunakan data atau instruksi yang selang waktu sebelumnya dieksekusi (reuse, digunakan berulang), misalkan instruksi, data, atau prosedur (function).

2. Pengamatan sederhana menunjukkan 90% waktu eksekusi program hanya menggunakan 10% dari kode program.

3. Terdapat dua alasan prinsip lokalitas ini merupakan “sifat” program aplikasi modern (well written): Struktur programming: code dalam bentuk blok dan terstruktur flow program tsb. Programmer cenderung menulis “code” secara kompak, dan menggunakan variabel secara efisien (berulang), mis. loop dsb. 4. Program dengan lokalitas temporal yang baik: lokasi memory yang diakses

kemungkinan besar akan diakses lagi berkali-kali dalam waktu dekat kelak. 5. Program dengan lokalitas spatial yang baik: sekali lokasi memori diakses makan

OSK/JM-2005/V2.2/14

Locality Example

• Data

– Reference array elements in succession (stride-1 reference pattern):

– Reference sum each iteration:

• Instructions

– Reference instructions in sequence: – Cycle through loop repeatedly:

Spatial locality Spatial locality Temporal locality Temporal locality sum = 0; for (i = 0; i < n; i++) sum += v[i]; return sum; CONTOH:

1. Fragmen “kode program” (Program C) di atas sering ditemukan dalam bentuk loops.

Bentuk loops sangat umum: secara logikal menggambarkan suatu flow program yang jelas, secara penulisan cukup kompak.

2. Logika program tersebut: menjumlahkan suatu array (larik) data integer

(bilangan bulat) dan menyimpan hasilnya pada variabel sum. Panjang (jumlah) data (array) adalah n (dari 0 s/d n-1).

3. Reference data program tersebut menunjukkan “spatial locality” yang sangat baik, karena mengakses array secara berurut atau atau melakukan “stride 1”. Jadi melakukan referensi ke lokasi data yang terdekat.

Demikian juga untuk kasus “temporal locality”, kita melihat dalam “body” dari loop, sum dilakukan referensi berulang-ulang (setiap iterasi).

4. Reference ke instruksi juga dalam bentuk berurut (spatial locality), dan menjalankan instruksi yang sama berulang dalam interasi loop (temporal locality). Asumsi umum program akan disimpan dalam lokasi memory secara berurut.

5. Kesimpulan dapat dikatakan “bentuk code” di atas mempunyai lokalitas program yang baik.

OSK/JM-2005/V2.2/15

Memory Hierarchies

Properti dasar dari hardware dan software:

Teknologi storage yang cepat lebih mahal per-byte,

dengan kapasitas yang lebih kecil.

Umumnya program cenderung mengikuti prinsip

lokalitas.

Terdapat kesenjangan (gap) antara kecepatan CPU

dan memory => perlu memory yang cepat

Properti ini yang saling melengkapi untuk

membangun sistim memory/storages komputer

dalam bentuk

memory hierarchy

.

BIG PICTURE:

1. Berdasarkan pengamatan “trend” teknologi storages (kuliah sebelumnya), maka teknologi storages yang cepat, pasti mahal dan kapasitasnya kecil. Disamping itu membutuhkan “power” yang lebih besar untuk setiap sel memori (mis. SRAM memerlukan 6 transistor, sedangkan DRAM hanya 1 transistor). Tabel di bawah ini memberikan perbandingan waktu akses dan cost (tahun 1997)

Teknologi Memori Waktu akses (tipikal) Cost $ per MB (1997)

SRAM 5 ns – 25 ns $100 - $250

DRAM 60 ns – 120 ns $5 - $10

Disk 10 – 20 juta ns $0,10 – $0.20

2. Program umumnya menganut prinsip lokalitas: program hanya memerlukan kode dan data yang kecil (karena spatial dan temporal locality) pada satu saat. 3. Terdapat “gap” dari kinerja CPU dan memory yang melebar, sehingga kita harus

meningkatkan kecepatan memory.

4. IDE: Membangun memori secara hirarkis dalam bentuk “tingkatan”, dengan memory yang cepat (faster) terdekat dengan CPU.

OSK/JM-2005/V2.2/16

An Example Memory Hierarchy

registers on-chip L1 cache (SRAM)

main memory (DRAM)

local secondary storage (local disks) Larger, slower, and cheaper (per byte) storage devices

remote secondary storage

(tapes, distributed file systems, Web servers)

Local disks hold files retrieved from disks on remote network servers. Main memory holds disk blocks retrieved from local disks.

off-chip L2 cache (SRAM)

L1 cache holds cache lines retrieved from the L2 cache memory. CPU registers hold words retrieved from L1 cache.

L2 cache holds cache lines retrieved from main memory.

L0: L1: L2: L3: L4: L5: Smaller, faster, and costlier (per byte) storage devices KONSEP:

1. Tujuan memory hirarkis adalah “ .. present user with as much memory as is available in the cheapest technology, while providing access at the speed offered by the fastest memory”.

2. Dari gambar di atas terlihat, bahwa memory yang tercepat dan termahal berada di CPU (register). Namun register jumlahnya sangat terbatas (mis. 32 buah register) jadi kapasitas yang paling kecil. Sedangkan tape, mempunyai kapasitas yang terbesar dan termurah (cost/MB), tapi waktu akses yang paling lambat. 3. Memori hirarkis menggunakan teknologi memori yang cepat (vs. kapasitas kecil)

dekat dengan CPU. Jadi akses pada level tertinggi dari hirarkis tadi dapat dilakukan dengan cepat. Di lain pihak pada tingkat bawah terdapat memory dengan kapasitas yang lebih besar tapi lebih lambat.

4. Dengan prinsip lokalitas maka terdapat ekspektasi bahwa CPU akan

mendapatkan (hit) data/program pada “upper level” dari memory hirarkis. Jikat program/data tidak berada (miss) di “upper level” (karena kapasitasnya kecil) maka akses dilakukan pada “lower level” (kapasitas lebih besar).

5. Kesimpulan: jika “hit rate” tinggi, maka secara efektif waktu akses akan

mendekati teknologi memory pada level tertinggi (tercepat), dan kapasitas sama dengan level paling bawah (terbesar).

OSK/JM-2005/V2.2/17

Caches

Cache:A smaller, faster storage device that acts as a

staging area for a subset of the data in a larger, slower device.

Ide dasar dari memory hirakis:

Untuk setiap k, “faster”, “smaller” device pada tingkat k melayani sebagai cache untuk “larger”, “slower” device pada tingkat (k+1).

Fungsi cache?

Program cenderung mengakses data pada tingkat k lebih sering dibanding mengakses data pada tingkat (k+1).

Jadi, storage pada tingkat (k+1) dapat lebih lambat, tapi lebih besar dan murah per-MB.

Net effect: A large pool of memory that costs as much as

the cheap storage near the bottom, but that serves data to programs at the rate of the fast storage near the top.

KONSEP:

1. Secara umum pengertian harafiah dari “cache” adalah tempat aman untuk menyimpan sesuatu. Istilah cache dalam pengertian “hardware” adalah tingkat memori yang ditambahkan antara CPU dan main memory pada mesin

komersial. Dalam sistim komputer, terdapat banyak implementasi “cache” yang sering kita dengar, misalkan cache memory, cache proxy (web services), cache disk dsb. Jadi cache menjadi istilah umum untuk “any storage” yang

memanfaatkan keuntungan akses dari prinsip lokalitas.

2. IDE: Terdapat hirarkis dalam peralatan hardware/software/system dalam bentuk caches untuk meningkatkan performance.

3. Keseluruhan efek dari memori hirarkis adalah: kita merancang sistem storage dengan kapasitas terbesar dan cost termurah pada tingkat terendah, namun memberikan waktu akses tercepat pada tinggkat teratas.

KONSEP:

1. Bagaimana memory hirarkis dapat efektif? Misalkan “hit ratio” tinggi.

Secara prinsip jika kita melakukan asumsi program cenderung mengikuti prinsip

lokalitas, misalkan lokalitas waktu (temporal), maka memory hirarkis akan menyimpan data yang “barusan” diakses atau baris instruksi yang dijalankan, dekat dengan

prosesor. Hal ini disebabkan kemungkinan besar prosesor akan menggunakan data/instruksi tersebut dalam waktu dekat.

2. Dalam penerapan memory hirarkis, maka terdapat “copy” data/program dari “lower level” ke “upper level” dalam bentuk blok. Jadi memindahkan sekaligus sekumpulan data/program yang berdekatan (spatial locality).

3. Pemindahan blok data/program menjadi issue dalam rancangan memory hirakis untuk “tingkat” yang berdekatan saja. Dengan kata lain, tidak diperlukan keseragaman mekanisme/tata-cara pemindahan blok untuk seluruh tingkat pada memory hirarkis. Misalkan terdapat mekanisme yang berbeda hubungan antara “cache memory” (upper level) dan “main memory” (lower level), dibandingkan dengan “main memory” (upper level) dan “disk” (lower level).

OSK/JM-2005/V2.2/18

Memory Hierarchy: How Does it Work?

Temporal Locality (Locality in Time):

=> Keep most recently accessed data items closer to

the processor

Spatial Locality (Locality in Space):

=> Move blocks consists of contiguous words to the

upper levels Lower Level Memory Upper Level Memory To Processor From Processor Block Block copy

OSK/JM-2005/V2.2/19

Caching in a Memory Hierarchy

0 1 2 3

4 5 6 7

8 9 10 11

12 13 14 15

Larger, slower, cheaper storage device at level k+1 is partitioned into blocks.

Data is copied between levels in block-sized transfer units

8 9 14 3

Smaller, faster, more expensive device at level k caches a

subset of the blocks from level k+1 Level k: Level k+1: 4 4 4 10 10 10 CONTOH:

1. Pada slide di atas menggambarkan mekanisme yang umum dalam memori hirarkis. Storage pada tingkat (k+1) dibagi atas blok data yang “contiguous”. Setiap blok diberi indeks atau nomor yang unik. Blok dapat berukuran tetap atau dalam kasus khusus bervariasi (mis. file servers).

2. Contoh pada level (k+1), storage dibagi atas 16 blok, dengan nomor 0 s/d 15. Storage pada level k, dibagi juga atas blok dengan ukuran yang sama, tapi tentunya jumlah blok (set) yang lebih sedikit, misalkan hanya 4 blok, yang telah berisi copy dari blok 4, 9, 14, dan 3.

OSK/JM-2005/V2.2/20 Request

14 Request

12

General Caching Concepts

Program perlu objek d, yang tersimpan pada blok b.

Cache hit

Program finds b in the cache at level k. E.g., block 14.

Cache miss

b is not at level k, so level k cache must fetch it from level k+1. E.g., block 12.

If level k cache is full, then some current block must be replaced (evicted). Which one is the “victim”?

• Placement policy:where can the new block go? E.g., b mod 4

• Replacement policy:which block should be evicted? E.g., LRU

9 3 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 Level k: Level k+1: 14 14 12 14 4* 4* 12 12 0 1 2 3 Request 12 4* 4* 12 CONTOH:

1. Saat program memerlukan objek data d pada tingkat (k+1), maka dicari d pada blok yang berada di level k. Jika d telah di cache pada level k, dan kita

menyebutnya sebagai “cache hit”. Program membaca d langsung dari data pada level k, sehingga kinerja meningkat karena level k lebih cepat dari level (k+1). 2. Di lain pihak, jika objek data d tidak ada pada level k, maka disebut “cache

miss”. Jika terjadi miss, maka cache pada level k akan mengambil blok yang berisi d dari level (k+1). Umumnya transfer seluruh blok tersebut dari level (k+1) ke level k.

3. Pada saat transfer ke upper level, tapi karena ukurannya kecil telah penuh, maka diperlukan penggantian (repacement) blok. Penggantian blok adalah copy kembali (update) blok pada level k ke level (k+1), dan “overwrite” blok k tersebut dengan blok yang baru dari level (k+1).

4. Pemilhan blok mana yang akan diganti sering disebut “replacement policy”. Policy yang umum adalah “random”, blok yang mana saja dapat diganti, namum ada juga yang disebut “Least recently used” (LRU), mengganti blok yang paling lama tidak diakses.

5. Contoh: membaca data pada blok 12, menyebabkan cache miss, maka terjadi transfer blok 12 menggantikan blok 4.

OSK/JM-2005/V2.2/21

Examples of Caching in the Hierarchy

Hardware 0 On-Chip TLB Address translations TLB Web browser 10,000,000 Local disk Web pages Browser cache Web cache Network buffer cache Buffer cache Virtual Memory L2 cache L1 cache Registers Cache Type Web pages Parts of files Parts of files 4-KB page 64-bytes block 64-bytes block 4-byte words What is Cached? Web proxy server 1,000,000,000 Remote server disks OS 100 Main memory Hardware 1 On-Chip L1 Hardware 10 Off-Chip L2 AFS/NFS client 10,000,000 Local disk Hardware+ OS 100 Main memory Compiler 0 CPU core Managed By Latency (cycles) Where is it Cached? BIG PICTURE:

1. Tabel di atas menunjukkan jenis/model caching yang dikenal dalam lingkup sistim komputer, dikategorisasi dari jenis, besarnya blok, dimana, latency dan pengaturan.

2. TLB=Tranlation Look Aside Buffer, tabel yang berisi pasangan virtual address dan physical address (untuk mempercepat address translation dalam penerapan virtual memory).

3. Implementasi memori hirarkis dalam sistim komputer mempunyai dampak yang sangat besar bagi programmer, software dan sistim operasi.

4. Misalkan programmer harus mengerti konsep ini untuk menulis program yang efisien dan cepat. Program yang baik harus meng-ekspose prinsip lokalitas secara maksimal, karena akan meningkatkan hit ratio. Jadi tidak benar jika programmer menganggap sistem memory sifatnya “random access” (waktu akses di address mana saja dari memory sama).

OSK/JM-2005/V2.2/22

How is the hierarchy managed?

Apa yang telah dipelajari?

Managed & transfer data?

Siapa yang bertanggung jawab.

Apa yang dapat dilakukan oleh programmer?

Designer? User?

Registers <-> Main-memory

by compiler (programmer?) Cache <-> Main-memory

by the hardware Main-memory <-> Disks

by the hardware and operating system (virtual memory)

BIG PICTURE:

1. Pada tingkat atas hubungan antara: register dan main-memory (misalkan transfer/copy data) diatur oleh compiler yang akan mencoba menggunakan secara efisien register yang ada dan mengurangy copy (load) data dari memory ke register.

2. Pada tingkat berikutnya: cache dan main-memory, maka control dilakukan oleh hardware (chipset dari motherboard).

3. Pada tingkat lebih bawah lagi: main-memory dan disks, dikontrol oleh system software (operating system) dalam konsep virtual memory, atau oleh

OSK/JM-2005/V2.2/23

Summary ..

Perkembangan teknologi dan organisasi CPU jauh

lebih cepat dari memori => terdapat “gap” antara

CPU dan memory.

Solusi teknologi memori mencoba mempersempit

gap ini tapi tidak tetap tidak mampu mengejar

ketinggalan tsb

Terknologi memori utama teranyar: DDR SDRAM,

mampu memompa data ke CPU dalam orde clock 200 MHz, tapi CPU mempunyak clock rate 3 GHz.

RINGKASAN:

1. Sistem komputer mencari solusi dari masalah dimana terdapat “gap” antara kecepatan CPU dan memory.

2. Program menganut prinsip lokalitas, temporal dan spatial.

3. Didukung oleh fakta bahwa terdapat berbagai variasi kecepatan dan cost dari teknologi memori. Prinsip lokalitas dari program menyebabkan kita dapat merancang memori hirarkis yang dapat diterapkan secara cost/effective untuk sistim komputer.

4. Programmer harus memanfaatkan struktur memori hirarkis untuk menulis kode program yang baik dalam mendukung prinsip lokalitas. Sebagai contoh akses ke array dilakukan dalam stride 1, atau lokasi memory yang berurutan.

5. Trend: Terdapat kesenjangan dalam perkembangan teknologi komponen

komputer (prosesor, memory, disk dll) atau system komputer (client, server dll), memori hirarkis dan caching menjadi salah satu pilihan solusi.

OSK/JM-2005/V2.2/24

Summary

Pengamatan

eksekusi program

:

Tidak semua kode program mempunyai kemungkinan

yang sama diakses oleh CPU

Program menganut prinsip lokalitas:

temporal

dan

spatial

Memori hirarkis

adalah pilihan terbaik dalam

menyediakan sistim memori yang cepat dengan

kapasitas dan cost yang termurah

Big IDEA

: “gap” antara kecepatan dan kapasitas

dalam penyimpanan data (komponen komputer)

harus diorganisasikan secara hirarkis dengan

memperpendek “gap” tsb, dengan

OSK/JM-2005/V2.2/25

Review Questions

1. Berikan contoh program (pseudo code) yang tidak menganut prinsip lokalitas (temporal dan spatial) terhada data akses.

Berikan karakteristik umum jenis program tsb.

2. Apakah ada program yang menunjukkan lokalitas temporal yang sangat tinggi, tapi spatial yang rendah terhadap data akses, atau sebaliknya.

3. Berikan contoh program (pseudo code) yang menunjukkan lokalitas temporal yang tinggi terhadap instruction (fetch).

4. Misalkan suatu komputer, waktu akses rata-rata cache = 20 ns, waktu akses rata-rata ke main-memory =100 ns. Asumsikan cache hit ratio dapat mencapai 95%. Hitung waktu rata-rata akses efektif sistim memori tersebut?