FLIP - FLOP

Kelompok :

Angga Surahman Sudibya (10407113) Ma’mun Fauzi (10407527)

Mudesti Astuti (10407571) Randy Septiawan (10407687)

Rahman Rohim (10407679)

JURUSAN TEKNIK ELEKTRO

UNIVERSITAS GUNADARMA

2009

DAFTAR ISI

DAFTAR ISI ...1

DAFTAR GAMBAR ...2

DAFTAR TABEL ...7

BAB I FLIP – FLOP ...9

1.1 Pengertian Flip – Flop ...9

1.2 Jenis-jenis Flip – Flop ...9

1.2.1 Flip – flop RS (dirangkai dengan gerbang NAND) ...9

1.2.2 Flip – flop RS yang berdetak ...11

1.2.3 Flip – flop D ...12

1.2.4 Flip – flop JK ...14

1.2.5 Flip – flop T ...15

DAFTAR GAMBAR

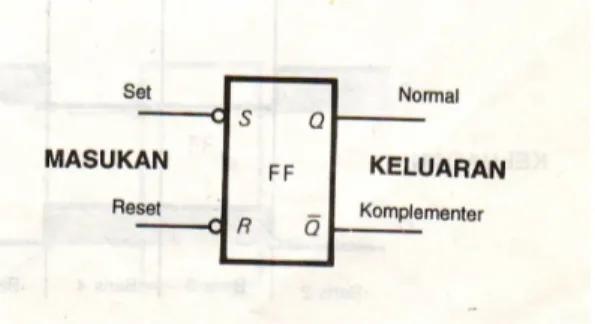

Gambar 1. Simbol logika untuk flip – flop RS.

Gambar 2. (a) simbol flip – flop RS, (b) Rangkaian flip – flop RS yang menggunakan gerbang NAND.

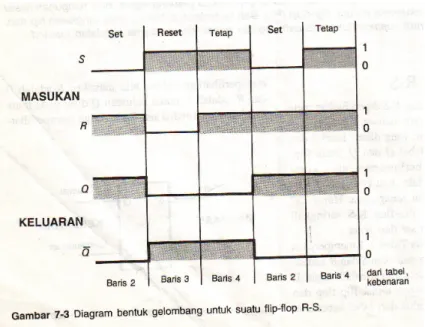

Gambar 3. Diagram bentuk gelombang flip – flop RS

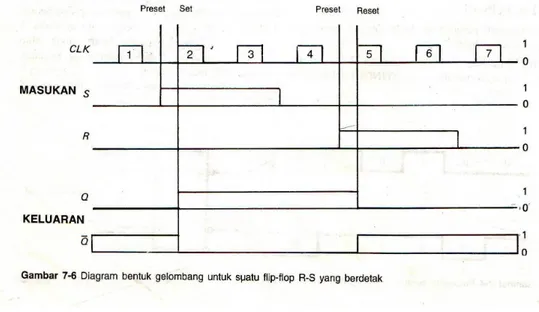

Gambar 5. Diagram bentuk gelombang flip – flop RS

Gambar 6. Rangkaian flip- flop RS berdetak dengan gerbang NAND.

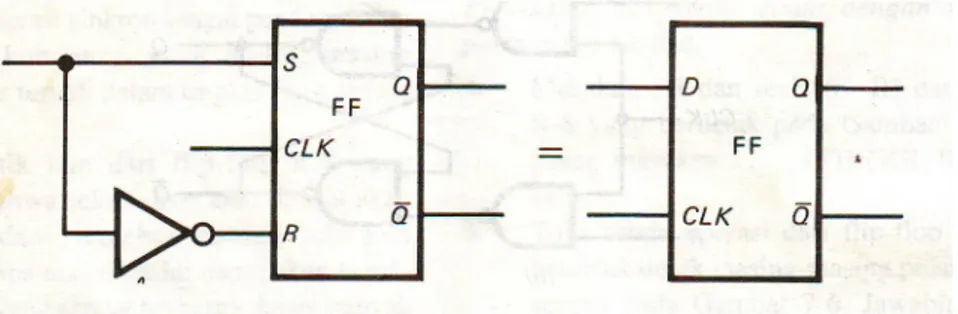

Gambar 8. Rangkaian flip – flop D.

Gambar 9. Flip – flop D komersial.

Gambar 11. Flip – flop T.

Tabel 1. Tabel kebenaran flip – flop RS.

Tabel 2. Tabel kebenaran flip – flop RS yang berdetak.

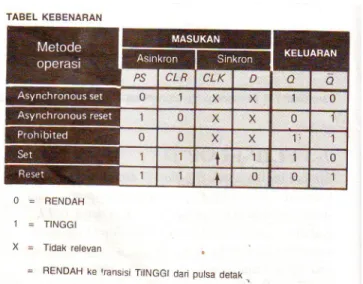

Tabel 4. Tabel kebenaran flip – flop D 7474.

Tabel 5. Tabel kebenaran flip – flop JK

BAB I

FLIP – FLOP

Flip – flop adalah perangkat bistabil, hanya dapat berada pada salah satu statusnya saja, jika input tidak ada, flip – flop tetap mempertahankan statusnya. Maka flip – flop dapat berfungsi sebagai memori 1-bit. Flip – flop termasuk ke dalam rangkaian logika gabungan atau sekuensial.

1.2 Jenis – Jenis Flip – Flop

1.2.1 Flip - Flop RS (dirangkai dengan gerbang NAND)

Simbol logika untuk flip – flop RS diperlihatkan pada gambar 1. Perhatikan bahwa FF – RS mempunyai dua masukan, yang diberi label S dan R. dua keluaran diberi label Q dan Q’. Pada flip – flop, keluaran selalu berlawanan, atau komplementer. Dengan kata lain, bila keluaran Q = 1, maka keluaran Q = 0, dan sebagainya. Huruf S dan R pada masukan flip - flop RS seringkali disebut masukan set dan reset.

Tabel kebenaran pada Tabel 1 memperjelas operasi flip – flop RS. Bila masukan S dan R keduanya 0, maka semua keluaran menjadi logis 1. Ini disebut keadaan larangan untuk flip – flop dan tidak digunakan. Baris kedua dari tabel kebenaran memperlihatkan bahwa bila masukan S adalah 0 dan R adalah 1, maka keluaran Q diset pada logis 1. Ini disebut kondisi set. Baris ketiga memperlihatkan bahwa bila masukan R adalah 0dan S adalah 1, maka keluaran direset menjadi 0. Ini disebut kondisi reset. Baris 4 pada tabel kebenaran memperlihatkan kedua masukan (R dan S) pada 1. Ini merupakan kondisi menganggur atau kondisi istirahat dan membuat Q dan Q’ dalam keadaan komplementer sebelumnya. Ini disebut kondisi tetap.

Dari tabel 1 terlihat bahwa untuk mengaktifkan pengesetan Q ke 1 diperlukan suatu logis 0. Untuk mengaktifkan reset, atau menghapus Q ke 0, juga diperlukan suatu logis Q. Oleh karena itu, untuk membuka atau untuk mengaktifkan diperlukan logis 0.

Flip – Flop RS dapat dibeli dalam suatu paket IC, atau dapat dirangkaikan dari gerbang logika, seperti dirangkai dengan gerbang NAND. Flip- flop RS dengan gerbang NAND ini beroperasi menurut tabel kebenaran pada tabel 1.

Diagram waktu, atau bentuk gelombang banyak diberikan untuk rangkaian logika sekuensial. Diagram ini memperlihatkan taraf tegangan dan pengaturan waktu antara masukan dan keluaran dan bentuknya sama dengan apa yang anda lihat pada osiloskop. Jarak horizontal adalah waktu dan jarak vertikal adalah tegangan. Flip – flop RS juga disebut suatu latch R-S atau suatu flip – flop set-reset.

1.2.2 Flip - Flop RS berdetak

Simbol logika untuk flip – flop RS yang berdetak diperlihatkan pada gambar 4. Amatilah bahwa flip – flop tersebut kelihatannya seperti flip – flop RS, tetapi flip –flop RS yang berdetak mempunyai satu masukan ekstra yang diberi label CLK (untuk detak). Gambar 5 menggambarkan operasi flip- flop RS yang berdetak. Masukan CLK ada pada sebelah atas diagram. Perhatikanlah bahwa pulsa detik (1) tidak mempunyai pengaruh terhadap keluaran Q bila masukan S dan R berada dalam posisi 0. Flip – flop tersebut berada pada mode mengganggur atau tetap selama pulsa detik 1. Pada posisi S preset, masukan S (set) dipindakan ke 1, tetapi keluaran Q belum diset ke 1. Sisi yang naik dari pulsa detak 2 memungkinkan Q menjadi 1. Pulsa 3 dan pulsa 4 tidak berpengaruh terhadap keluaran Q. Selama pulsa 3, flip – flop berada dalam mode set, sedangkan selama pulsa 4, berada dalam mode tetap. Selanjutnya, masukan R dipreset ke 1. Pada sisi yang naik dari pulsa detak 5, keluaran Q direset menjadi 0. Flip – flop berada dalam mode reset baik selama pulsa detak 5 maupun 6. Flip – flop berada dalam mode tetap selama pulsa detak 7; dengan demikian, keluaran normal Q masih tetap 0.

Perhatikan bahwa keluaran flip – flop RS yang berdetak hanya berubah pada satu pulsa detak. Kita katakan bahwa flip – flop ini beroperasi secara sinkron

dalam kalkulator dan komputer, yang masing-masing langkahnya harus terjadi dalam tingkat yang sangat tepat.

Karakteristik lain dari flip – flop RS yang berdetak adalah bahwa sekali diset atau direset akan tetap pada keadaan tersebut kecuali bila kita mengubah beberapa masukan. Ini merupakan karakteristik memori, yang sangat berharga dalam banyak rangkaian digital. Karakteristik ini akan jelas selama mode-tetap dari operasi. Dalam diagram bentuk gelombang pada gambar 5, flip – flop ini ada dalam mode-tetap selama pulsa detak 1, 4, dan 7.

Tabel 2 memperlihatkan tabel kebenaran untuk flip – flop RS yang berdetak. Perhatikanlah bahwa hanya tiga baris sebelah atas dari tabel kebenaran yang digunakan baris sebelah bawah merupakan larangan dan tidak digunakan.

Gambar 6 memperlihatkan diagram rangkaian flip – flop RS yang berdetak. Perhatikanlah bahwa dua gerbang NAND telah ditambahkan pada masukan flip – flop RS untuk menambah sifat detakan.

Simbol flip-flop D diperlihatkan pada gambar 7 hanya mempunyai satu masukan data (D) dan satu masukkan detak (CLK). Flip – flop D sering disebut flip-flop tunda. Kata “ tunda” menggambarkan apa yang terjadi pada data, atau informasi pada masukkan D. Data ( 0 atau 1 ) pada masukkan D di tunda 1 pulsa detak dari pemasukan sampai keluaran Q. Tabel kebenaran yang disederhanakan untuk flip – flop D diperlihatkan pada Tabel 3. Perhatikan bahwa keluaran Q mengikuti masukan D sesudah satu pulsa detak.

Flip – flop D dapat dibentuk dari flip – flop R-S yang berdetak dengan menambahkan satu pemblik, seperti diperlihatkan pada Gambar 8. Umumnya Anda akan menggunakan flip – flop D yang dimasukan ke suatu IC. Gambar 9 memperlihatkan flip – flop D komersial khusus. Dua masukkan ekstra [ PS ( preset ) dan CLR ( clear ) telah ditambahkan pada flip – flop D pada Gambar 9. Masukan PS mengeset keluaran Q menjadi 1 bila dibuka oleh suatu logis 0. Masukan PS dan CLR mengklearkan keluaran Q menjadi 0 bila dibuka oleh suatu logis 0. Masukan PS dan CLR akan menolak masukan D dan CLK. Masukan D dan CLK beroperasi seperti pada flip – flop D pada gambar 7.

Tabel kebenaran yang lebih rinci untuk flip – flop D TTL 7474 komersial diperlihatkan pada Tabel 4. Ingatlah bahwa masukkan asinkron ( bukan sinkron ) ( PS dan CLR ) menolak masukkan sinkron. Masukkan asinkron ada dalam kontrol flip – flop D dalam tiga baris pertama dari tabel kebenaran pada Tabel 4. Masukan sinkron ( D dan CLR ) tidak relevan seperti yang diperlihatkan oleh “X” pada tabel kebenaran, akan dihindarkan. Dengan kedua masukan asinkron tidak dibuka ( PS = 1 dan CLR) =1 ).flip –flop D dapat diset dan direset menggunakan

pulsa detak untuk memindahkan data dari masukkan D kekeluaran Q dari flip – flop. Ini terjadi selangkah dengan detak , dan disebut dengan operasi sinkron.

Flip – flop D dirangkai satu sama lain untuk membentuk register geser dan register penyimpan. Register ini digunakan secara luas dalam sistem digital. Flip-flop D menunda data untuk mencapai keluaran Q satu pulsa detak dan disebut flip-flop tunda. Flip –flop D tercakup di dalam TTL dan CMOS berupa 74HC74, 74H273, 4013 atau 40174 ICs.

1.2.4 Flip - Flop JK

Flip – flop J-K merupakan flip – flop universal dan digunakan paling luas, memiliki sifat dari semua flip – flop jenis lain. Simbol logika untuk flip – flop J-K digambarkan pada gambar 10. Masukan yang diberi label J dan K merupakan masukan data. Masukan yang diberi label CLK merupakan masukan detak. Keluaran Q dan Q merupakan keluaran komplementer biasa pada satu flip – flop. Tabel kebenaran untuk flip – flop J-K diperlihatkan pada Tabel 5. Bila masukan J dan K kedua-duanya O, maka flip – flop tidak dibuka dan keluaran tidak berubah keadaan. Flip – flop tersebut ada dalam mode tetap.

Baris 2 dan 3 dari tabel kebenaran memperlihatkan kondisi reset dan set untuk keluaran Q. Baris 4 melukiskan keluaran penggunaan posisi togel dari flip – flop J-K. Bila kedua masukan data J dan K ada pada 1, pulsa detak yang berulang menyebabkan keluaran berubah mati-hidup-mati-hidup-mati-hidup, dan

Flip – flop J-K digunakan secara luas dalam banyak rangkaian digital. Anda akan menggunakan flip – flop J-K, khususnya dalam pencacah ( counters ). Pencacah dijumpai dalam hampir setiap sistem digital.

1.2.5 Flip - Flop T

Simbol untuk flip – flop T diperlihatkan pada Gambar 11. Flip – flop T merupakan rangkaian flip-flop yang dibangun dengan menggunakan flip-flop J-K yang kedua inputnya dihubungkan menjadi satu maka akan diperoleh flip-flop yang memiliki watak membalik output sebelumnya jika inputannya tinggi dan outputnya akan tetap jika inputnya rendah.