Dessy Wulandari Asfary Putri – Rangkaian Sequensial 1

Rangkaian Sequensial

Rangkaian logika di kelompokkan dalam 2 kelompok besar, yaitu rangkaian logika kombinasional dan rangkaian logika sekuensial. Bentuk dasar dari rangkaian logika kombinasional adalah gerbang logika dan rangkaian logika sekuensial adalah rangkaian flip-flop. Rangkaian logika sekuensial sangat bermanfaat karena karakteristik memorinya.

Flip-flop juga di sebut kancing, multivibrator bistabil atau biner, yaitu multivibrator yang keluarannya berupa suatu tegangan rendah (0) atau tinggi (1), selama belum ada masukan yang merubah keadaan tersebut. Rangkaian yang bersangkutan harus di drive oleh satu masukan yang di sebut pemicu (trigger), keadaan tersebut akan berubah kembali bila ada masukan pemicu lagi. Flip-flop di interkoneksikan untuk membentuk rangkaian logika sekuensial untuk penyimpanan, pewaktu, penghitung dan pengurutan (sequencing).

Berdasarkan cara penyimpanannya flip-flop dapat di golongkan atas : RS flip-flop JK flip-flop D flip-flop T flip-flop Master-slave flip-flop

Flip-Flop RS

Kebanyakan flip-flop dasar di sebut flip-flop RS. Flip-flop ini mempunyai 2 masukan yang di beri label dengan set (S) dan reset (R), flip-flop RS mempunyai masukan rendah aktif pada masukan S dan R. Tidak seperti gerbang logika, flip-flop mempuyai 2 komplementer, keluaran tersebut di beri label Q dan Q’, keluaran Q di anggap merupakan keluaran normal dan paling sering di gunakan. Keluaran lain Q merupakan merupakan komplemen dari keluaran Q dan di sebut juga keluaran komplementer. Pada kondisi normal, keluaran-keluaran ini selalu

Dessy Wulandari Asfary Putri – Rangkaian Sequensial 2 merupakan komplementer, dengan demikian bila Q = 1 maka Q’ = 0, atau bila Q

= 0 maka Q’ = 1 . Q Q S R 1 2

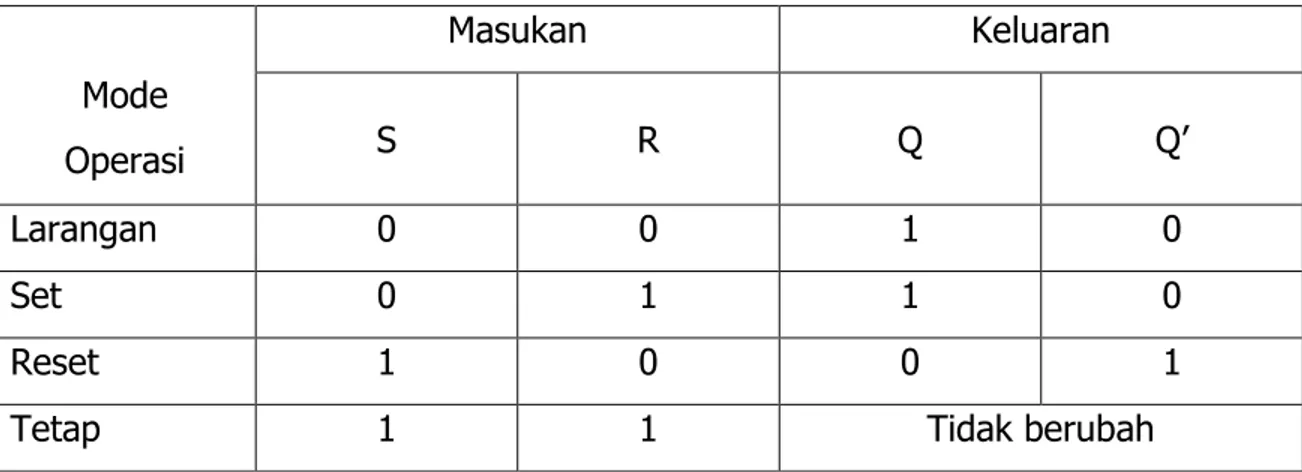

RS flip-flop dengan menggunakan Gerbang-gerbang NAND Mode Operasi Masukan Keluaran S R Q Q’ Larangan 0 0 1 0 Set 0 1 1 0 Reset 1 0 0 1

Tetap 1 1 Tidak berubah

Tabel kebenaran RS flip-flop

Gambar Flip – flop RS di rangkaikan dari dua gerbang NAND seperti di atas, karakteristik yang ada dari keluaran satu gerbang NAND ke masukan gerbang lainnya. Sama halnya dengan gerbang logika, tabel kebenaran merupakan penentuan operasi RS flip-flop ini. Baris 1 pada tabel kebenaran itu di sebut keadaan terlarang dalam arti bahwa keadaan tersebut memungkinkan kedua keluaran menjadi 1 atau tinggi, kondisi ini tidak di gunakan pada flip-flop RS. Baris 2 pada tabel tersebut menunjukkan kondisi set dari flip-flop. Di sini,

Dessy Wulandari Asfary Putri – Rangkaian Sequensial 3 level rendah atau logika 0 mengaktifkan masukan set (S). Logika 0 ini mengeset

keluaran Q normal menjadi tinggi atau 1, seperti di tunjukkan pada tabel kebenaran. Kemudian kondisi set ini akan terlihat bila menganalisa gambar rangkaian rs flip-flop dengan gerbang NAND. Logika 0 pada gerbang 1 membangkitkan 1 pada keluaran. Logika 1 ini di masukkan kembali ke gerbang 2, sekarang gerbang 2 mempunyai dua logika 1 yang di masukkan pada masukannya, sehingga mendorong keluaran menjadi 0. Maka keluaran Q’ menjadi 0 atau rendah, kemudian baris 3 pada tabel merupakan kondisi reset. Level rendah atau logika 0 mengaktifkan masukan reset tersebut. Hal ini akan mereset keluaran normal Q menjadi 0. Kemudian baris ke 4 dari tabel tersebut menunjukkan kondisi tak terbuka atau tetap dari flip-flop RS, keluaran masih tetap seperti keadaan sebelum terjadi kondisi tetap. Jadi tidak terdapat perubahan keluaran dari keadaan sebelumnya.

Bisa di simpulkan, bila tabel kebenaran di atas yang menunjukkan kondisi set, hal ini berarti pengesetan keluaran Q menjadi 1. Begitu pula, kondisi reset berarti di reset dan keluaran Q menjadi 0. Dengan demikian berarti kondisi operasi menunjuk pada keluaran normal dan bahwa keluaran komplementer (Q) adalah berlawanan dengan keluaran tersebut, oleh karena itu fungsi flip-flop yang memegang data sementara, maka flip-flop di sebut kancing RS.

R s Q Q 1 0 1 0 1 0 1 0

Dessy Wulandari Asfary Putri – Rangkaian Sequensial 4

Detak (Clocked) Flip-Flop RS

Flip-flop RS yang berdetak menambahkan suatu sifat suatu sifat sinkron yang berguna untuk kancing RS. Flip-flop RS yang berdetak akan beroperasi serempak dengan detak atau piranti pewaktu atau beroperasi secara sinkron.

2 1 R S Q Q 3 4 CK

RS flip-flop menggunakan Gerbang-gerbang NAND Dengan Clocked

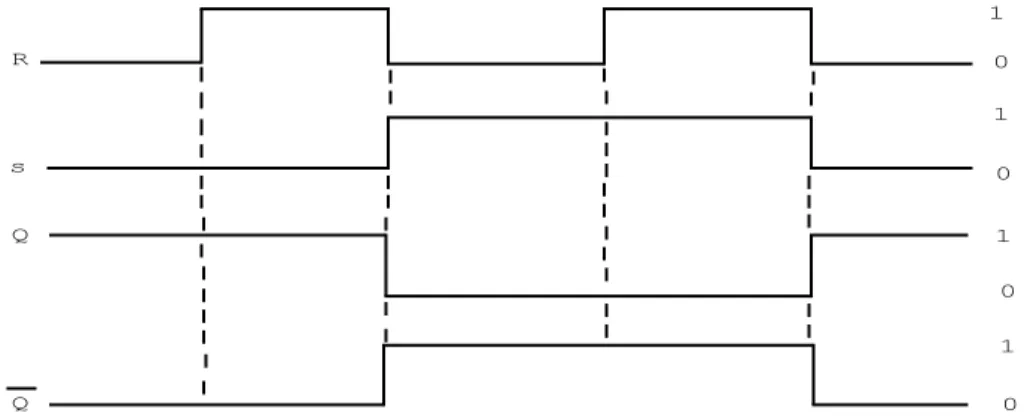

Gambar di atas mengilustrasikan 2 gerbang NAND yang di tambahkan pada Latch RS (flip-flop) untuk membentuk flip-flop RS yang berdetak. Gerbang NAND 3 dan 4 menambahkan sifat berdetak pada kancing RS tersebut, kemudian dengan adanya gerbang 1 dan 2 menyebabkan terbentuknya kancing RS atau flip-flop. Oleh karena pembalikan gerbang 3 dan 4, maka sekarang masukan reset (R) menjadi masukan tinggi aktif. Masukan detak (CK) memacu flip-flop bila pulsa detak menjadi tinggi, flip-flop RS yang berdetak di katakan sebagai suatu peralatan level yang di pacu. Setiap kali pulsa detak menjadi tinggi, maka informasi pada masukan data (R dan S) akan di pindahkan ke keluaran. Bahwa masukan-masukan R dan S adalah aktif selama keseluruhan waktu level pulsa detak tinggi. Level tinggi dari pulsa detak ini di anggap suatu pulsa pembuka.

Dessy Wulandari Asfary Putri – Rangkaian Sequensial 5 Mode

Operasi

Masukan Keluaran

CK S R Q Q’

Tetap 0 0 Tidak berubah

Reset 0 1 0 1

Set 1 0 1 0

Terlarang 1 1 1 1

Tabel kebenaran RS flip-flop dengan clocked

Q S R CK 1 0 1 1 1 0 0 0

Diagram Waktu RS Flip-Flop Dengan Clocked

D Flip-Flop

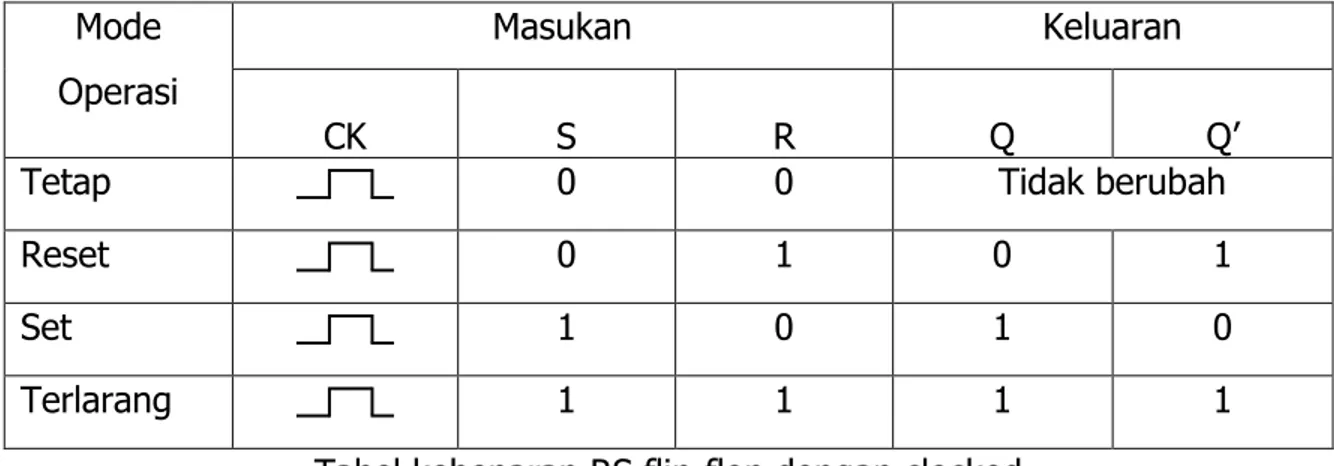

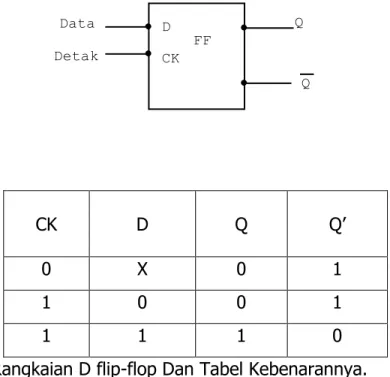

Flip-flop ini mempunyai 2 masukan yaitu masukan data tunggal (D) dan masukan (CK), flip-flp D sering di sebut sebagai flip-flop tunda. Adapun bentuk masukan data (D), masukan tersebut akan tertunda selama satu pulsa detak untuk mencapai keluaran normal (Q), lalu data di pindahkan ke keluaran pada transisi pulsa detak rendah ke tinggi.

Dessy Wulandari Asfary Putri – Rangkaian Sequensial 6 Data Detak Q Q D CK FF CK D Q Q’ 0 X 0 1 1 0 0 1 1 1 1 0

Rangkaian D flip-flop Dan Tabel Kebenarannya.

Berdasarkan dengan tabel kebenaran di atas, x = don’t care atau 1 atau 0,D flip-flop hanya meyimpan data 1 bit. Pada baris 1 pada tabel kebenaran menyatakan D dan CK dalam keadaan sama yakni level rendah dan menghasilkan keluaran rendah pula, kemudian baris 2 saat clock menjadi logika 1 atau level tinggi dan D masih dalam keadaan level rendah, maka keluaran tetap dalam keadaan rendah atau logika 0. Lalu pada baris ke 3 masukan CK dan D sama-sama dalam keadaan tinggi sehingga menyebabkan Q menjadi 1.

D CK Q 1 0 1 0 1 0

Dessy Wulandari Asfary Putri – Rangkaian Sequensial 7 3.4 JK Flip-Flop

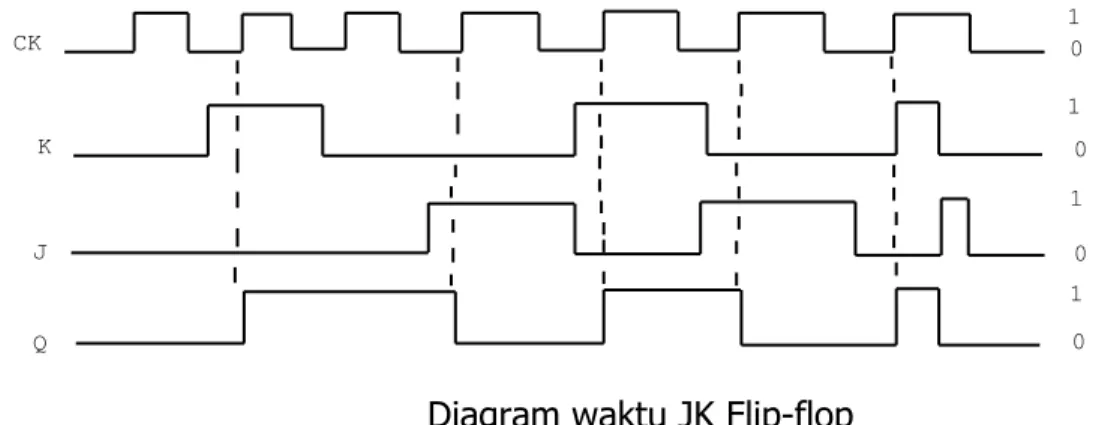

adalah rangkaian flip-flop yang mencacah banyaknya positive edge trigger (pada saat tepi naik) atau negatif edge trigger (pada saat tepi turun). Piranti ini dapat di anggap sebagai flip-flop universal, flip-flop ini mempunyai 3 masukan sinkron yang di ilustrasikan dengan label J, K dan CK. Masukan J dan K merupakan masukan data dan masukan detak memindahkan data dari masukan ke keluaran. Terdapat juga 2 keluaran yakni keluaran normal (Q) danlomplementer (Q’) K Q Q CK FF J J K Detak JK Flip-Fop Mode Operasi Masukan Keluaran CK J K Q Q’ NC 0 0 Tidak berubah Reset 0 1 0 1 Set 1 0 1 0

Togel 1 1 Keadaan Berlawanan

Ket :

NC = No change atau tetap pada nilai terakhirnya

Togel = Keadaan berlawanan dari input sebelumnya atau berpindah ke keadaan lawannya

Berdasarkan mode operasi pada tabel kebenaran di atas, baris ke 1 menunjukkan kondisi tetap atau kondisi terbuka karena masukan J dan K adalah rendah. Kondisi reset dari flip-flop di tunjukkan pada baris 2, bila J = 0 dan K = 1 serta pulsa detak datang pada masukan CK, maka flip-flop tersebut di reset

Dessy Wulandari Asfary Putri – Rangkaian Sequensial 8 (Q = 0). Baris ke 3 menunjukkan kondisi set dari flip-flopJK, bila J = 1 dan K =

0 serta terdapat pulsa detak, maka keleuaran Q di set menjadi 1. Kemudian baris 4 dalam kondisi yang sangat berguna dari flip-flop JK, kondisi ini di sebut posisi togel (Toggle), bila masukan J dan K keduanya sama-sama tinggi, maka keluaran akan berlawanan dengan keadan waktu pulsa tiba pada masukan CK.

Q J K CK 10 1 1 1 0 0 0

Diagram waktu JK Flip-flop 3.5 T Flip-Flop

Adalah di mana outputnya akan selalu berubah pada saat input datang yaitu input di buat bergerak dari 1 ke 0 (nol).

T Q Q 1 0 1 0 T = input Q = Output

Dessy Wulandari Asfary Putri – Rangkaian Sequensial 9 Togel dapat di artikan sebagai output yang berubah terhadap input yang

bergerak dari 1 ke 0, bila tidak ada tanda seperti itu maka dapat di artikan output berubah terhadap input bergerak dari 0 ke 1.

CLOCK T Q Q’

0 1 0

1 0 0

0 1 0

1 0 1