SINKRONISASI PEMANCAR DAN PENERIMA

MODULASI AMPLITUDO DENGAN

EMPAT

FREQUENCY HOPPING

Diajukan untuk memenuhi salah satu syarat memperoleh gelar Sarjana Teknik pada

Program Studi Teknik Elektro

Disusun oleh

ROBERTUS HADI PUTRANDAGA NIM : 045114027

PROGRAM STUDI TEKNIK ELEKTRO

FAKULTAS SAINS DAN TEKNOLOGI

UNIVERSITAS SANATA DHARMA

YOGYAKARTA

SYNCHRONIZATION AMPLITUDE MODULATION

TRANSMITTER AND AMPLITUDE MODULATION

RECEIVER WITH FOUR FREQUENCY HOPPING

Presented as Partial Fulfillment of the Requirements to obtain the Sarjana Teknik Degree

in Electrical Engineering

By :

ROBERTUS HADI PUTRANDAGA Student Number : 045114027

ELECTRICAL ENGINEERING STUDY PROGRAM

SCIENCE AND TECHNOLOGY FACULTY

SANATA DHARMA UNIVERSITY

YOGYAKARTA

v

Saya menyatakan dengan sesungguhnya bahwa tugas akhir yang saya tulis ini tidak

memuat karya atau bagian karya orang lain, kecuali yang telah disebutkan dalam kutipan dan

daftar pustaka, sebagaimana layaknya karya ilmiah.

Yogyakarta, Maret 2010

Penulis

PUBLIKASI KARYA ILMIAH UNTUK KEPENTINGAN AKADEMIS

Yang bertanda tanggan di bawah ini, saya mahasiswa Universitas Sanata Dharma: Nama : Robertus Hadi Putrandaga

Nomor Mahasiswa : 045114027

Demi pengembangan ilmu pengetahuan, saya memberikan kepada Perpustakaan Universitas Sanata Dharma karya ilmiah saya yang berjudul :

Sinkronisasi Pemancar Dan Penerima Modulasi Amplitudo Dengan

Empat Frequency Hopping

beserta perangkat yang diperlukan (bila ada). Dengan demikian saya memberikan kepada Perpustakaan Universitas Sanata Dharma hak untuk menyimpan, me- ngalihkan dalam bentuk media lain, mengelolanya dalam bentuk pangkalan data, mendistribusikan secara terbatas, dam mempublikasikan di internet atau media lain untuk kepentingan akademis tanpa perlu meminta ijin dari saya maupun memberikan royalti kepada saya selama tetap mencantumkan nama saya sebagai penulis.

Demikian pernyataan ini yang saya buat dengan sebenarnya. Yogyakarta, Maret 2010

Teknik frequency hopping (FH) merupakan salah satu metode transmisi data dalam

bidang telekomunikasi. Gangguan-gangguan pada telekomunikasi seperti jamming dan noise

dapat dikurangi dengan menggunakan teknik ini. Penelitian ini bertujuan untuk menghasilkan

perangkat subsistem sinkronisasi yang digunakan pemancar dan penerima Amplitude

Modulation (AM) frequency hopping.

Subsistem sinkronisasi pada pemancar dan penerima AM frequency hopping memiliki

dua bagian utama yaitu tone generator dan tone decoder. Tone generator memiliki keypad

1x3 yang terhubung dengan mikrokontroler ATTINY2313 untuk mengatur waktu tunda.

Sinkronisasi antara pemancar dan penerima AM frequency hopping menggunakan sinyal

DTMF yang dihasilkan dari IC MT8888. Mikrokontroler ATTINY2313 yang digunakan pada tone decoder berfungsi untuk mengatur pembagi terprogram dalam membangkitkan frekuensi carrier dengan data input yang berasal dari IC MT8870.

Hasil dari penelitian ini adalah subsistem sinkronisasi yang dapat mensinkronkan pemancar AM frequency hopping dan penerima AM frequency hopping dalam transmisi data.

Perangkat subsistem sinkronisasi bekerja dengan memodulasi frekuensi carrier secara

bergantian pada empat frekuensi yang berbeda yaitu 900 KHz, 950 KHz, 1000 KHz dan 1050 KHz dengan periode hopping 0,25 detik.

Frequency hopping technique is one of data transmission method in telecommunication. Disturbances in telecommunication like jamming and noise can be reduce with this technique. This research is aimed to produce synchonization subsystem instrument that is used in AM frequency hopping transmitter and AM frequency hopping receiver.

Synchonization subsystem in AM frequency hopping transmitter and AM frequency hopping receiver have two main part, the first one is tone generator and the other part is tone decoder. Tone generator have 1x3 keypad that is connected to ATTINY2313 microcontroller to regulate delay. Synchronization between AM frequency hopping transmitter and AM frequency hopping receiver used DTMF signal that is resulted by IC MT8888. ATTINY2313 that is utilized in tone decoder there is functioned as a regulator programmable divider to raise carrier requency with data input there is originated from IC MT8870.

The result of this research are synchonization subsystem that can synchronized AM frequency hopping transmitter and AM frequency hopping receiver in data transmission. Synchronization subsystem instrument operates to modulation alternately in four different carrier frequency, that is 900 KHz, 950 KHZ, 1000KHz, 1050 KHz with 0,25 second hopping period

Puji dan syukur penulis panjatkan ke Hadirat Tuhan Yang Maha Esa yang telah melimpahkan rahmat dan karunia-Nya sehingga penulis dapat menyelesaikan Tugas Akhir yang berjudul “Sinkronisasi Pemancar Dan Penerima Modulasi Amplitudo Dengan Empat Frequency Hopping”. Tugas Akhir ini disusun sebagai salah satu syarat untuk

memperoleh gelar Sarjana Teknik. Dalam penyusunannya, banyak pihak yang telah membantu dan memberikan dukungan pada penulis, oleh karena itu, penulis ingin mengucapkan terima kasih kepada :

1. Bapak Damar Widjaja, S.T., M.T., selaku Dosen Pembimbing I Tugas Akhir yang telah banyak meluangkan waktu untuk memberi bimbingan.

2. Bapak Alexius Rukmono, S.T. selaku Pembimbing II yang telah bersedia meluangkan waktu untuk membimbing penulis.

3. Untuk seluruh dosen-dosen di program studi Teknik Elektro atas segala tempaan ilmunya.

4. Bapak (N.Kasihhadi H.) dan Ibuku tercinta (Ch. Marini) yang selalu memberiku dorongan, semangat, nasihat dan dukungan moril, spiritual maupun materi. 5. Untuk kakak-kakakku, Hadi Putrandana dan Ayu Damayanti atas segala

bantuan moril, spiritual maupun materi.

6. Untuk Bernadetha Novia Anggraeni atas doa, dukungan, dan semangat tanpa henti.

7. Untuk seluruh teman-teman elektro angkatan 2004 atas segala doa dan dukungannya.

8. Teman-temanku, Robertus Heru Wiranto, Eri Cahyono, Sumin, Antonius Bayu Ariyanto, Sugiarto, Leonardus Agung, Y. Dedeo Indra, Yohanes Mayolis, Nova Budi Prasetyo, Yanuarius Vendi Purnomo, dan Ign. Tulus Setiadi atas segala doa dan dukungannya.

9. Para laboran elektro atas kesabaran dan bantuan yang telah diberikan.

agar dalam proses penulisan di kemudian hari dapat semakin baik. Semoga Tugas Akhir dapat dimanfaatkandan dikembangkan lebih lanjut oleh peneliti lain sehingga tulisan ini dapat lebih bermanfaat.

Yogyakarta, Maret 2010

HALAMAN JUDUL………... i

HALAMAN PERSETUJUAN………... iii

HALAMAN PENGESAHAN……… iv

PERNYATAAN KEASLIAN KARYA………. v

HALAMAN PERSEMBAHAN DAN MOTTO HIDUP………. vi

LEMBAR PERNYATAAN PERSETUJUAN PUBLIKASI KARYA ILMIAH UNTUK KEPENTINGAN AKADEMIS……….. vii

INTISARI………... vii

ABSTRACT………. ix

KATA PENGANTAR……… x

DAFTAR ISI………... xii

DAFTAR GAMBAR……….. xv

DAFTAR TABEL………... xix

BAB I PENDAHULUAN………... 1

1.1 Judul………. 1

1.2 Latar Belakang………. 1

1.3 Batasan Masalah………... 2

1.4 Tujuan dan Manfaat Penelitian………. 2

1.5 Metodologi Penelitian……….. 2

1.6 Sistematika Penulisan………... 2

BAB II DASAR TEORI………. 4

2.1 Modulasi Amplitudo………. 4

2.2 Pemancar AM………... 5

2.3 Penerima AM………... 6

2.4 Sinkronisasi……….. 7

2.5 Teknik Frequency Hopping..……… 8

2.6 DTMF (Dual Tone Multi Frequency)……….. 10

2.6.1 Tone Generator………... 10

2.6.2 Tone Decoder……….. 16

2.7.3 Struktur Mikrokontroler AVR ATTiny2313………... 24

2.7.4 On-Chip Oscillator………. 25

2.7.5 Timer/counter………. 26

2.8 Mixer Audio……….. 26

2.9 Transistor Sebagai Saklar………... 27

2.10 Demultiplekser 4 ke 16 CD4514……….……….………… 28

2.11 Rangkaian penampil………. 30

2.11.1 Decoder BCD ke seven segment………... 30

2.11.2 Seven Segment………... 31

BAB III PERANCANGAN ALAT……… 33

3.1 Diagram Blok Sistem Komunikasi Radio AM Frequency Hopping………… 33

3.2 Diagram Blok dan Penjelasan Umum Subsistem Sinkronisasi Pemancar dan Penerima AM Frequency Hopping………... 33

3.3 Subsistem Sinkronisasi Bagian Pemancar Radio AM………... 35

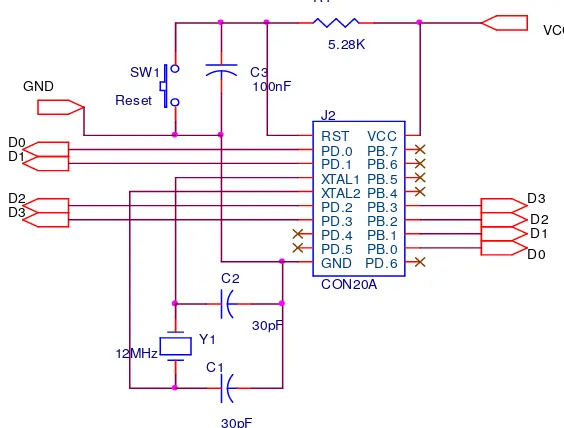

3.3.1. Konfigurasi mikrokontroler ATTINY2313………... 35

3.3.2. Tone Generator……….….………... 36

3.3.3 Mixer Audio……… 38

3.3.4 Rangkaian Keypad 1x3………... 38

3.4 Subsistem sinkronisasi Bagian Penerima Radio AM ……….…………. 39

3.4.1 Tone Decoder……….……….……… 39

3.4.2 Demultiplekser 4 bit ke 16 jalur………. 41

3.4.3 Transistor sebagai saklar……… 42

3.4.4 Rangkaian penampil………... 44

3.5 Perancangan perangkat lunak (Software)………. 45

3.5.1 Program Utama pada Pemancar AM FH……… 45

3.5.2 Inisialisasi Port………... 46

3.5.3 Program Subrutin awal………... 46

3.5.4 Program Subrutin Cek_pin………. 46

3.5.5 Program Subrutin Proses……… 47 3.5.6 Program Subrutin Pin1………... 3.5.7 Program Subrutin Pin2………...

3.6 Mekanisme Pengujian dalam Proses Sinkronisasi………... 51

BAB IV HASIL PENGAMATAN DAN PEMBAHASAN……….. 53

4.1 Perangkat Keras Hasil Perancangan………. 53

4.2 Hasil Pengujian Alat Secara Keseluruhan……… 57

4.2.1 Pengujian Subsistem Sinkronisasi Pada Pemancar AM FH………... 57

4.2.2 Pengujian Subsistem Sinkronisasi Pada Penerima AM FH…………... 62

4.2.3 Pengujian saat terjadi sinkronisasi ……… 65

4.2.4 Tunda Waktu………... 71

4.3 Hasil Pengujian Tiap Blok………... 72

4.3.1 Hasil Pengujian Dan Pengamatan ToneGenerator……… 72

4.4 Hasil Pengujian Dan Pengamatan Bagian Penerima AM FH………... 76

4.4.1 Hasil Pengujian Dan Pengamatan ToneDecoder………... 76

4.4.2 Hasil Pengamatan Pada Penampil………... 77

4.4.3 Hasil pengamatan pada Demultipleksing 4-bit ke 16 jalur……… 79

4.4.4 Pengujian Rangkaian Transistor Sebagai Saklar……… 80

4.5 Pengujian Perangkat Lunak (Software)……… 82

BAB V KESIMPULAN DAN SARAN……….. 91

5.1 Kesimpulan………... 91

5.2 Saran………. 91

Gambar 2.1. Bentuk gelombang carrier……….. 4

Gambar 2.2. Bentuk gelombang pemodulasi………..………... 5

Gambar 2.3. Bentuk gelombang termodulasi………..………. 5

Gambar 2.4. Diagram blok pemancar AM………... 5

Gambar 2.5. Diagram blok penerima AM……… 6

Gambar 2.6. Contoh sistem sinkronisasi frekuensi ………. 7

Gambar 2.7. Contoh sistem sinkronisasi fasa ……….. 8

Gambar 2.8. Teknik frequency hopping ……….. 9

Gambar 2.9. Interferensi pada transmisi frequency hopping ………... 9

Gambar 2.10. Diagram blok dari IC MT8888C ………...………. 11

Gambar 2.11. Kaki IC MT8888C ……….. 14

Gambar 2.12. Diagram blok dari IC MT8870D ……… 16

Gambar 2.13. Tanggapan filter ……….. 17

Gambar 2.14. Konfigurasi kaki IC MT8870D ………... 18

Gambar 2.15. Kaki IC MT8870D ………. 19

Gambar 2.16. Diagram blok fungsional ATTINY2313.……….…... 21

Gambar 2.17. Arsitektur dari AVR ATTINY2313……….……... 22

Gambar 2.18. Kaki AVR ATTINY2313..………...………. 24

Gambar 2.19. Menghubungkan sumber clock ………... 26

Gambar 2.20. Rangkaian mixer audio dengan dua input ………... 27

Gambar 2.21. (a) Rangkaian transistor sebagai saklar ……….. 27

(b) Grafik output dari transistor, keadaan cut-off dan saturasi... 27

Gambar 2.22. Diagram koneksi IC CD4514 ………...……….. 29

Gambar 2.23. Konfigurasi kaki IC 74LS48 ………... 31

Gambar 2.24. Konfigurasi seven segment……….. 32

Gambar 2.25. (a) Common anode………... 32

(b) Common cathode……….... 32

Gambar 3.1. Blok diagram umum sistem komunikasi radio AM FH…………... 33

Gambar 3.2. Diagram blok subsistem sinkronisasi pada pemancar AM FH... 34

Gambar 3.3. Diagram blok subsistem sinkronisasi pada penerima AM FH ….. 34

Gambar 3.7. Rangkaian mixer audio……….... 38

Gambar 3.8. Rangkaian keypad 1×3………. 39

Gambar 3.9. Konfigurasi IC tone decoder ………... 39

Gambar 3.10. Konfigurasi dari demultiplekser 4 bit ke 16……… 41

Gambar 3.11. Rangkaian transistor sebagai saklar ……….... 42

Gambar 3.12. Rangkaian lengkap penampil dengan driver 74LS48……….. 44

Gambar 3.13. Diagram alir program utama untuk tone generator………... 45

Gambar 3.14. Diagram alir program subrutin awal……….... 46

Gambar 3.15. Diagram alir program subrutin cek_pin………... 47

Gambar 3.16. Diagram alir program subrutin proses………. 47

Gambar 3.17. Diagram alir program subrutin pin1……….... 48

Gambar 3.18. Diagram alir program subrutin pin2……….... 48

Gambar 3.19. Diagram alir program subrutin kirim ……….. 49

Gambar 3.20. Diagram alir program utama tone decoder……….. 50

Gambar 3.21. Flowchart proses sinkronisasi pada pemancar……… 51

Gambar 3.22. Flowchart proses sinkronisasi pada penerima………. 52

Gambar 4.1. Blok tone generator (TG) (a) TG tampak sisi depan………. 53

(b) TG tampak sisi samping………. 53

(c) TG tampak sisi atas……… 53

Gambar 4.2. Blok tone decoder (TD) (a) TD tampak sisi depan………. 55

(b) TD tampak sisi samping………. 55

(c) TD tampak sisi atas……… 55

Gambar 4.3. Pengujian transmisi sinyal sinkronisasi pada pemancar………….. 57

Gambar 4.4. Modulasi amplitudo dengan sinyal carrier 900 KHz ………. 58

Gambar 4.5. Sinyal informasi 5 KHz dan tone 1 dengan kombinasi frekuensi 700Hz dan 1240Hz……….. 58

Gambar 4.6. Modulasi amplitudo dengan sinyal carrier 950 KHz……….. 59

700Hz dan 1500Hz ………. 60 Gambar 4.10. Modulasi amplitudo dengan sinyal carrier 1050 KHz………….... 61 Gambar 4.11. Sinyal informasi 5 KHz dan tone 4 dengan kombinasi frekuensi

800Hz dan 1240Hz ………. 61

Gambar 4.12. Sinyal blok audio output saat penerima menala frekuensi 900

KHz……….. 62

Gambar 4.13. Sinyal blok audio output saat penerima menala frekuensi 950

KHz………... 63

Gambar 4.14. Sinyal blok audio output saat penerima menala frekuensi 1000

KHz………... 63

Gambar 4.15. Sinyal blok audio output saat penerima menala frekuensi 1050

KHz………... 64

Gambar 4.16. Modulasi amplitudo dengan sinyal carrier 900 KHz………... 65 Gambar 4.17. Sinyal informasi 5 KHz dan tone 1 dengan kombinasi frekuensi

700Hz dan 1240Hz………... 66

Gambar 4.18. Sinyal blok audio output saat penerima menala frekuensi 900

KHz………... 66

Gambar 4.19. Modulasi amplitudo dengan sinyal carrier 950 KHz………... 67 Gambar 4.20. Sinyal informasi 5 KHz dan tone 2 dengan kombinasi frekuensi

700Hz dan 1360Hz………... 67

Gambar 4.21. Sinyal audio output saat penerima menala frekuensi 950 KHz…... 67 Gambar 4.22 Modulasi Amplitudo dengan Gelombang Carrier 1000 kHz……... 68 Gambar 4.23. Sinyal informasi 5 KHz dan tone 3 dengan kombinasi frekuensi

700Hz dan 1500Hz……….. 68

Gambar 4.24. Sinyal audio output saat penerima menala frekuensi 1000 KHz…. 69 Gambar 4.25 Modulasi Amplitudo dengan Gelombang Carrier 1050 kHz……... 69 Gambar 4.26. Sinyal informasi 5 KHz dan tone 4 dengan kombinasi frekuensi

800Hz dan 1240Hz………... 70

Gambar 4.30. Tone 2 dengan kombinasi frekuensi 700Hz dan 1360Hz hasil

pengiriman angka 2 dari mikrokontroler……….. 73 Gambar 4.31. Tone 3 dengan kombinasi frekuensi 700Hz dan 1500Hz hasil

pengiriman angka 3 dari mikrokontroler……….. 74 Gambar 4.32. Tone 4 dengan kombinasi frekuensi 780Hz dan 1240Hz hasil

pengiriman angka 4 dari mikrokontroler……….. 75 Gambar 4.33. Tunda waktu rangkaian penampil pada blok TG dan TD……….... 77 Gambar 4.34. Contoh gambar tone 1 dengan kombinasi frekuensi 700Hz dan

1240Hz pada seven segment………... 78 Gambar 4.35. Contoh gambar tone 2 dengan kombinasi frekuensi 700Hz dan

1360Hz pada seven segment………... 78 Gambar 4.36. Contoh gambar tone 3 dengan kombinasi frekuensi 700Hz dan

1500Hz pada seven segment………... 78 Gambar 4.37. Contoh gambar tone 4 dengan kombinasi frekuensi 780Hz dan

1240Hz pada seven segment………... 79 Gambar 4.38. Gambar hasil simulasi program tone 1 dengan kombinasi

frekuensi 700 Hz dan 1240 Hz pada bagian TG………... 86 Gambar 4.39. Gambar hasil simulasi program tone 2 dengan kombinasi

frekuensi 700Hz dan 1360Hz pada bagian TG………. 86 Gambar 4.40. Gambar hasil simulasi program tone 3 dengan kombinasi

frekuensi 700Hz dan 1500Hz pada bagian TG………. 87 Gambar 4.41. Gambar hasil simulasi program tone 4 dengan kombinasi

frekuensi 780Hz dan 1240Hz pada bagian TG………. 87 Gambar 4.42. Gambar hasil simulasi program tone 1 dengan kombinasi

frekuensi 700Hz dan 1240Hz pada bagian TD………. 89 Gambar 4.43. Gambar hasil simulasi program tone 2 dengan kombinasi

frekuensi 700Hz dan 1360Hz pada bagian TD………. 89 Gambar 4.44. Gambar hasil simulasi program tone 3 dengan kombinasi

frekuensi 700Hz dan 1500Hz pada bagian TD………. 90 Gambar 4.45. Gambar hasil simulasi program tone 4 dengan kombinasi

Tabel 2.1. Frekuensi DTMF………..……….. 10

Tabel 2.2. Register-register MT8888C………... 11

Tabel 2.3. Susunan bit dalam register kontrol a) Posisi bit register kontrol A……….. 12

b) Posisi bit register kontrol B……….. 12

Tabel 2.4. Output IC MT8888C……….. 14

Tabel 2.5. Kombinasi data output TD………. 17

Tabel 2.6. Fungsi Alternatif dari Port B……….. 23

Tabel 2.7. Fungsi Alternatif dari Port D………... 24

Tabel 2.8. Daftar dari 16 sandi dan fungsi decoding………... 29

Tabel 2.8. (Lanjutan) Daftar dari 16 sandi dan fungsi decoding………... 30

Tabel 2.9. Tabel kebenaran 74LS48……… 31

Tabel 4.1. Keterangan dan fungsi umum blok – blok rangkaian perangkat TG pada pemancar AM ………. 54

Tabel 4.2. Keterangan dan fungsi umum blok-blok rangkaian perangkat TD pada penerima AM………... 56

Tabel 4.3. Hasil lengkap dari output TG………. 76

Tabel 4.4. Tabel output TD untuk keempat tone………. 77

Tabel 4.5. Kombinasi bilangan biner 4-bit menjadi 16 jalur………... 79

Tabel 4.5. (Lanjutan) Kombinasi bilangan biner 4-bit menjadi 16 jalur………... 80

PENDAHULUAN

1.1 Judul

Sinkronisasi Pemancar dan Penerima AM Modulasi Amplitudo dengan 4 Frequency Hopping (Synchronization Transmitter and Receiver Amplitude Modulation with 4 Frequency Hopping)

1.2 Latar Belakang

Komunikasi pada dasarnya merupakan pertukaran informasi antara dua tempat yang berjauhan. Informasi bisa berupa sinyal suara dan gambar. Beberapa tahun terakhir, perkembangan sistem komunikasi berbasis spread spectrum sangat pesat [1]. Disebut spread spectrum karena lebar bidang transmisi yang digunakan jauh lebih besar dari pada bandwidth minimum yang dibutuhkan untuk mentrasmisikan informasi. Teknik modulasi spread spectrum secara umum terbagi menjadi dua teknik, yaitu DSSS (Direct Sequence Spread Spectrum) dan FHSS (Frequency Hopping Spread Spectrum).

Kendala yang dihadapi pada perambatan gelombang radio adalah sinyal informasi yang dipancarkan akan mengalami variasi amplitudo (fading), mendapat interferensi, dan noise. Alternatif solusi yang dapat dipergunakan untuk mengatasi masalah tersebut adalah dengan menggunakan teknik modulasi Frequency Hoping Spread Spectrum (FHSS). Frequency Hopping (FH) adalah perpindahan satu frekuensi ke frekuensi yang lain dalam satu pita frekuensi.

1.3 Batasan Masalah

Perangkat sinkronisasi pemancar dan penerima AM dengan frequency hopping ini memiliki spesifikasi sebagai berikut:

1. Periode perpindahan tiap frekuensi carrier (Frequency Hopping Period) sebesar 0.25 detik.

2. Dapat mensinkronkan empat frekuensi carrier yaitu f1= 900 KHz, f2= 950 KHz, f3=

1000 KHz, dan f4= 1050 KHz yang dikirim secara berurutan dari pemancar AM ke

penerima AM.

3. Sinkronisasi dari pemancar AM ke penerima AM menggunakan tone detector. 4. Penelitian ini di titik beratkan pada sistem sinkronisasi pemancar dan penerima,

sedangkan pemancar dan penerima hanyalah alat bantu presentasi.

1.4 Tujuan dan Manfaat Penelitian

Menghasilkan perangkat sinkronisasi pada pemancar dan penerima AM dengan metode FH. Sinyal informasi dari pemancar AM menggunakan 4 frekuensi carrier secara berurutan dengan teknik FH.Penelitian ini dapat dimanfaatkan sebagai rujukan untuk mengembangkan ilmu pengetahuan dan kehandalan informasi pada komunikasi termodulasi amplitudo dengan FH.

1.5 Metodologi Penelitian

Penelitian ini disusun berdasarkan studi literatur, serta mempelajari cara kerja dan sekaligus cara-cara merencanakan dan membuat peralatan tersebut. Perencanaan peralatan menggunakan teori yang ada untuk mendapatkan karakteristik yang sesuai dengan spesifikasi yang ditentukan. Pembuatan peralatan untuk setiap bagian perangkat sinkronisasi sesuai dengan fungsi masing-masing dan kemudian diujikan.

Pengujian perangkat sinkronisasi memerlukan sebuah pemancar dan penerima AM. Sinyal output dari pemancar akan disinkronkan terlebih dahulu sebelum dipancarkan ke penerima. Penerima harus bisa menerima sinyal yang sudah disinkronisasi pada empat frekuensi berbeda secara bergantian.

1.6 Sistematika Penulisan

BAB I . Pendahuluan

Pendahuluan berisi latar belakang masalah, batasan masalah, tujuan penelitian, manfaat penelitian, metode penulisan dan sistematika penulisan.

BAB II. Dasar teori

Bab ini berisi penjelasan umum dan teori dasar sinkronisasi pemancar dan penerima AM yang terkait dengan perancangan.

BAB III. Perancangan Perangkat Keras

Bab ini berisi mengenai hal-hal yang berkaitan dengan perancangan perangkat sistem kerja sinkronisasi komunikasi gelombang radio AM FH.

BAB IV. Analisis Hasil dan Pembahasan

Bab ini berisi analisis dari hasil pengukuran dan pembahasan yang diperoleh selama penelitian.

BAB V. Penutup

2.1 Modulasi Amplitudo

Modulasi adalah prose

informasi yang mempunyai f

AM) merupakan salah satu

Dalam modulasi amplitudo,

ditambahkan kepada amplitud

Sinyal carrier dinyataka

dengan Ecmax adalah amplitu

adalah fase carrier. Bentuk ge

Sinyal pemodulasi diny

dengan Emmaxadalah amplitud

dan φm adalah fasa pemodulas

Proses modulasi mengh

Bentuk gelombang term

Gam

DASAR TEORI

do

ses pengaturan parameter sinyal berfrekuensi ti

frekuensi rendah. Modulasi amplitudo (Amplit

jenis modulasi yang mengubah amplitudo sin

, suatu tegangan yang sebanding dengan

do carrier.

kan sebagai berikut [1]

( )

c(

c c)

c t E t

e = maxcosω +φ

tudo sinyal carrier, ωc adalah frekuensi sudut

gelombang pembawa ditunjukkan pada Gambar 2

yatakan dengan

( )

m(

m m)

m t E t

e = maxcosω +φ

tudo sinyal pemodulasi, ωm adalah frekuensi su

lasi. Bentuk gelombang pemodulasi ditunjukkan p

ghasilkan sinyal termodulasi yang dinyatakan den

e

( )

t =[

Ecmax +em(t)]

cos(

ωt+φ)

rmodulasi ditunjukkan pada Gambar 2.3.

mbar 2.1. Bentuk gelombang carrier [1]

tinggi oleh sinyal

itude Modulation,

sinyal carrier [1].

sinyal modulasi

ut carrier, dan φc

2.1.

sudut pemodulasi,

pada Gambar 2.2.

ngan

(2.3) (2.2)

Gamba

Ga

2.2

Pemancar AM

Bentuk dasar pemancar

Gamb

Penjelasan tiap blok ad

1. Osilator diguna

sinyal informas

2. Driver berfung

sinyal output os

3. Booster berfun

termodulasi ke a

Osil

bar 2.2. Bentuk gelombang pemodulasi [1]

ambar 2.3. Bentuk gelombang termodulasi [1]

ar AM ditunjukkan pada Gambar 2.4.

Antena

bar 2.4.Diagram blok pemancar AM [1]

adalah sebagai berikut [1] :

nakan sebagai penghasil frekuensi yang akan

asi.

ngsi untuk memperbesar penguatan tegangan k

osilator masih kecil sinyalnya.

ungsi sebagai penguat akhir untuk menguatk

e antena supaya dapat dipancarkan.

Driver Booster silator

Modulator

n dimodulasi oleh

karena amplitudo

4. Modulator ada

akan ditumpan

mempunyai day

5. Antena peman

berupa sinyal el

2.3 Penerima AM

Pesawat penerima AM

menangkap sinyal radio AM

Selanjutnya, penerima harus m

digunakan yaitu 540kHz sam

informasi dari sinyal carrier d

diagram blok penerima AM se

Gamb

Penjelasan tiap blok ad

1. Antena berfun

dipancarkan ole

2. RF (Radio Fr

termodulasi dar

3. Mixer berfungs

(intermediate fr

4. IF (Intermedia

sinyal dari RF Am

dalah pengubah parameter sinyal pembawa agar

angkan pada sinyal pembawa lewat sebuah

aya yang cukup.

ancar digunakan untuk memancarkan sinyal te

elektomagnetik.

M harus melakukan sejumlah fungsi. Pertama,

dari pemancar dan menolak sinyal yang tidak

menguatkan sinyal yang diinginkan sampai ke ti

ampai 1600kHz. Akhirnya, penerima harus me

dan menyampaikan kepada pengguna. Gambar 2

secara umum.

mbar 2.5. Diagram blok penerima AM [1]

adalah sebagai berikut [1] :

fungsi untuk menerima gelombang elektro

oleh pemancar radio.

Frequency) Amplifier berfungsi untuk mem

ari antena serta dapat meningkatkan SNR (Signal

gsi untuk mengubah sinyal frekuensi radio ke s

frequency). Mixer memerlukan input dari sebuah

ate Frequency) Amplifier berfungsi untuk me

Amplifier.

ar informasi yang

trafo modulator

termodulasi yang

a, penerima harus

ak diinginkan [1].

tingkat yang dapat

emulihkan sinyal

r 2.5 menunjukkan

tromagnetik yang

emperkuat sinyal

l to Noise Ratio).

suatu nilai tengah

ah osilator lokal.

5. Detektor berfu

sehingga meng

modulasi atau s

6. LPF (Low Pass

saja.

7. Audio Amplifie

sinyal audio.

8. Osilator Lokal

frekuensi 455kH

9. Speaker berfun

menjadi suara.

2.4 Sinkronisasi

Pengertian sinkronisasi

dilakukan dalam waktu ber

penting dalam konteks siste

sinkronisasi carrier dan sin

sinkronisasi frekuensi dan sink

1. Sinkronisasi frekuensi

Sistem kerja sinkroni

frekuensi input dan frekuensi

Gambar 2.6 [2].

Gamb

rfungsi memulihkan sinyal informasi dari mo

nghasilkan tegangan output proporsional yang m

sinyal informasi [1].

ss Filter) adalah filter yang mampu melewatkan

fier berfungsi memperkuat daya dari filter yan

al berfungsi untuk membangkitkan sinyal sinus

kHz lebih tinggi dari frekuensi radio yang berasal

ungsi untuk mengubah sinyal suara yang berup

si adalah untuk membuat transmisi data atau

ersama-sama. Sinkronisasi merupakan kebutuh

stem komunikasi digital. Ada dua macam sin

inkronisasi waktu

.

Sinkronisasi carrier ada dnkronisasi fasa [2].

nisasi frekuensi secara umum adalah mende

si output dari controlled oscillator (CO) seperti

bar 2.6. Contoh sistem sinkronisasi frekuensi [2]

odulated carrier

merupakan sinyal

n frekuensi rendah

ang menghasilkan

us yang memiliki

sal dari antena.

upa getaran listrik

u informasi dapat

uhan yang paling

sinkronisasi, yaitu

dua jenis, yaitu

deteksi perbedaan

ditunjukkan pada

Sinyal output dari CO k

perbedaan frekuensi yang te

Locked Loop), namun dalam

itu, saat sinkronisasi berada pa

sama dengan sinyal referensi p

yang tepat. Jika CO terjadi

comparator sampai output CO

2. Sinkronisasi fasa

Rangkaian sinkronisasi

dengan proses tala pada rad

langsung [2]. Sistem kerja dar

frekuensi CO pada PLL sepe

perbedaan fasa. Perbedaan fas

fasa yang terjadi dapat dita

disinkronisasi secara akurat.

ukuran dari error fasa.

Gam

2.5 Teknik

Frequency H

Frequency hopping a

pembawa secara periodis yang

informasi selama periode tert

seperti ditunjukkan pada Gam

kemudian diumpan balik untuk mengurangi atau

terjadi. Mekanisme ini ekuivalen dengan sebu

sinkronisasi frekuensi hanya frekuensi saja ya

pada keadaan seimbang frekuensi output yang di

i pada input. Kontrol yang sempurna akan mengh

i error, maka output akan diumpan balikkan m

O tidak terdapat error frekuensi.

i fasa atau sering disebut PLL mempunyai cara

adio kristal, tetapi pengaturan frekuensi dilakuk

ari sinkronisasi fasa sama dengan sistem kerja p

perti yang ditunjukkan pada Gambar 2.7, menda

asa yang terjadi dapat berupa error pada salah sa

itahan secara konstan dengan gelombang ou

t. Frekuensi referensi yang menjadi input tidak

ambar 2.7.Contoh sistem sinkronisasi fasa [2]

Hopping

atau lompatan frekuensi adalah perubahan

ng diatur oleh algoritma tertentu [3]. Frekuensi in

ertentu dan berpindah ke frekuensi yang lain, b

ambar 2.8. Anak panah pada Gambar 2.8 menun

tau menghilangkan

buah PLL (Phase

yang diatur. Selain

dihasilkan dari CO

ghasilkan frekuensi

menuju frekuensi

ra kerja yang sama

ukan secara tidak

a pada sinkronisasi

dapat input berupa

satu fasanya. Error

utput yang telah

k tergantung pada

frekuensi sinyal

ini akan membawa

, begitu seterusnya,

(hop) frekuensi yang berurutan

terjadi berulang-ulang. Perpind

dalam satu detik. Stasiun pe

lompatan yang sama supaya in

Gam

Lompatan dari satu frek

acak dengan menggunakan san

mempunyai deretan sandi yan

Dengan mengacak pola lomp

dihindari. Jika interefensi mun

maka sinyal pembawa akan

frekuensi f2. Hal ini ditunjuk

Gambar 2.9. I

tan, dari frekuensi f1→ f3→ f7→ f2→ f5→

indahan frekuensi terjadi beberapa ratus sampai b

penerima juga harus melakukan perpindahan f

informasi yang dikirimkan dapat diterima kembal

ambar 2.8. Teknik frequency hopping [3]

ekuensi ke frekuensi yang lain diatur secara beru

sandi pseudorandom. Sandi pseudorandom adalah

ang akan terulang secara periodis dalam perioda y

mpatan, sinyal penggangu (interfering signal) d

uncul dan mengganggu salah satu kanal berfreku

n selalu mengalami gangguan tetapi hanya s

ukkan pada Gambar 2.9.

Interferensi pada transmisi frequency hopping [3

6

4 f

f →

→ , dan

i beberapa ribu kali

frekuensi dengan

ali.

urutan atau secara

ah sandi acak yang

yang cukup lama.

diharapkan dapat

kuensi, misal f2,

saat berada pada

2.6

DTMF (Dual Tone M

disandikan dengan dua buah

tersedia [4]. Dua buah frek

ditentukan dalam dua kelompo

kolom vertikal dan kelompok

Sedangkan delapan frekuensi y

1336 Hz, 1477 Hz dan 1633 H

Kombinasi tiap angka

untuk angka 1 disandikan de

kolom pertama. Sedangkan an

1477 Hz pada kolom ketiga.

16 tanda. Selain sandi angka n

Komponen DTMF dibedakan

dan pengawas sandi DTMF (D

2.6.1

Tone Generator

Bagian utama sistem

MT8888C [5]. MT8888C me

membangkitkan tone seperti

inputnya. Diagram blok pada g

ulti Frequency) adalah teknik penyandian an

h frekuensi sinusoidal yang berbeda dari delapan

ekuensi yang berbeda tersebut dijumlahkan ma

pok, yaitu kelompok frekuensi tinggi yang tergab

k frekuensi rendah yang tergabung dalam empat

i yang tersedia adalah 697 Hz, 770 Hz, 852 Hz, 9

Hz.

Tabel 2.1. Frekuensi DTMF [4]

a ditunjukkan dalam Tabel 2.1. Dari tabel dap

dengan frekuensi 697 Hz pada baris pertama da

angka 9 disandikan dengan frekuensi 852 Hz pada

. Kombinasi dari delapan frekuensi tersebut dap

nol (0) sampai 9, DTMF juga mempunyai sandi

n menjadi dua macam, yaitu penyandi DTMF (

(DTMF Decoder).

tone generator (TG) tersusun oleh IC (int

erupakan sebuah DTMF generator yang didesa

ti tone dialing pada telepon dengan 4-bit dat

a gambar 2.10 menunjukkan sebuah fungsional da

angka-angka yang

an frekuensi yang

agnitudenya dan

bung dalam empat

at baris horizontal.

, 941 Hz, 1209 Hz,

apat dilihat bahwa

dan 1209 Hz pada

da baris ketiga dan

apat menyandikan

di *, #, A, B, C, D.

(DTMF Encoder)

ntegrated circuit)

sain khusus untuk

ata biner sebagai

ini membutuhkan sebuah sinyal input gelombang sinus yang dihasilkan dari kristal 3.579545

MHz untuk membangkitkan delapan frekuensi sinyal sinusoidal yang berbeda.

Gambar 2.10 menunjukkan bahwa MT8888C mempunyai 2 register dengan 4 fungsi.

Kedua register tersebut antara lain register kontrol dan register status. MT8888 dilengkapi

dengan jalur alamat RS0 untuk membedakan kedua register ini. Register pertama (RS0=’0’)

dinamakan sebagai register data. Sinyal DTMF yang dibangkitkan MT8888 didapat dengan

cara membaca isi register ini (Receive Data Register), sedangkan sinyal DTMF yang ingin

dikirim disimpan di register ini (Transmit Data Register). Register kedua (RS0=’1’)

dinamakan sebagai register Kontrol/Status. Cara kerja MT8888 diatur dengan cara mengirim

data ke register ini, dan keadaan MT8888 dapat dipantau dengan cara membaca isi register

ini. Tabel 2.2 menunjukkan pengaturan dari register-register MT8888.

Gambar 2.10.Diagram blok dari IC MT8888C [5]

Kapasitas register MT8888 hanya 4 bit, tetapi ada 7 hal yang diatur melalui register

kontrol. Register kontrol dibagi menjadi dua bagian yaitu register kontrol A dan register

kontrol B. Pertama kali menyimpan data ke register kontrol selalu diterima oleh Bagian A

register kontrol, jika RSEL atau bit 3 bernilai tinggi, maka pengiriman data berikutnya akan

diterima oleh Bagian B register kontrol. Tabel 2.3 (a) dan (b) menunjukkan susunan bit dalam

register kontrol A dan register kontrol B.

Table 2.3. Susunan bit dalam register kontrol [5]: (a) Posisi bit register kontrol A (b)

Posisi bit register kontrol B

(a)

(b)

Keterangan Tabel 2.3 adalah sebagai berikut:

1. TOUT

Tout adalah kontrol output tone. Logika tinggi mengaktifkan output tone, sedangkan

logika rendah menonaktifkan output tone. Bit ini mengontrol semua pengiriman fungsi

tone.

2. CP/DTMF

Call progress (proses panggil) atau pilihan mode DTMF. Logika tinggi mengaktifkan

mode proses penerimaan panggilan, sedangkan logika rendah mengaktifkan mode

DTMF. Mode DTMF pada MT8888C mampu menerima dan mengirimkan sinyal

3. IRQ

Logika tinggi mengaktifkan fungsi interupsi, sedangkan logika rendah

menonaktifkan fungsi interupsi. Saat IRQ aktif dan mode DTMF dipilih output pin IRQ

akan menjadi rendah saat sinyal DTMF diterima untuk durasi guard time (GT), atau

pemancar siap untuk mengirimkan beberapa data (burst mode)

4. RSEL (register select)

Logika tinggi mengendalikan register B untuk proses penulisan selanjutnya pada

kendali alamat register. Setelah penulisan ke register B kontrol akan mengikuti proses

penulisan selanjutnya yang akan dilanjutkan ke register A.

5. BURST ENABLE

Logika tinggi menonaktifkan burst mode, sedangkan logika rendah mengaktifkan

burst mode. Pada saat aktif kode-kode digital mewakili sinyal DTMF yang akan ditulis

ke register pengirim. Hasil dari pengiriman sinyal DTMF secara burst dan berhenti yaitu

selama 50 ms.

6. TEST

Logika tinggi mengaktifkan mode test, sedangkan logika rendah menonaktifkan

mode test. Saat mode test aktif dan mode DTMF dipilih, sinyal yang dihasilkan IRQ

berupa sinyal analog yang digunakan untuk mengontrol tunda waktu bit dari status

register.

7. S/D (single or dual tone)

Logika tinggi menghasilkan output berupa single tone, sedangkan logika rendah

menghasilkan dual tone (DTMF).

8. C/R (column or row tone select)

Logika tinggi menghasilkan output pada kolom tone, sedangkan logika rendah

menghasilkan output pada baris tone. Fungsi dari C/R terhubung dengan S/D bit.

Ketika membangkitkan sinyal dual tone, TG membangkitkan satu frekuensi kolom dan

satu frekuensi baris kemudian menjumlahkan sebagai output. Table 2.4 menunjukkan

frekuensi yang dihasilkan oleh TG. Gambar 2.11 menunjukkan bentuk fisik IC MT8888C.

Gambar 2.11 huruf pada setiap baris dan kolom diberi garis di atasnya yang menandakan

Table 2.4.Output IC MT8888C [5]

Gambar 2.11. Kaki IC MT8888C [5]

Fungsi dari masing-masing kaki dari IC MT8888D adalah sebagai berikut:

1. Kaki 1, IN+

Merupakan kaki input non-inverting bagi penguat operasional internal.

2. Kaki 2, IN-

Merupakan kaki input inverting bagi penguat operasional internal.

3. Kaki 3, GS ( gain select)

Merupakan kaki output penguat operasional internal.

4. Kaki 4, Vref (reference voltage)

Merupakan tegangan referensi, nilainya sebesar ½ VDD.

5. Kaki 5, VSS

6. Kaki 6 dan kaki 7, OSC1 dan OSC2

Merupakan kaki input dan output dari osilator yang terhubung dengan sebuah kristal

sebesar 3,579545 Mhz.

7. Kaki 8, output tone

Merupakan tone output dari MT8888C

8. Kaki 9, R/W ( Write)

Merupakan kaki input atau output untuk mengatur register-register. Kaki R/W dipakai

untuk menentukan arah data. Jika R/W=’1’ menandakan proses pengambilan data dari

MT8888C, sedangkan R/W=’0’ berarti pengiriman data ke MT8888.

9. Kaki 10, CS (select chip)

Merupakan kaki input yang aktif jika diperi logika rendah.

10. Kaki 11, RSO (Register Select)

Merupakan kaki input untuk mengatur register pada MT8888C. Kaki ini akan aktif jika

diberi logika tinggi.

11. Kaki 12, RD (Read)

Kaki RD (kaki 12) dipakai untuk mengambil data dari MT8888, dalam keadaan

normal RD=’1’, selama proses pengambilan data RD menjadi ‘0’ dan data diambil dari

MT8888 setelah RD berubah dari ‘0’ menjadi ‘1’

12. Kaki 13, IRQ/CP (Interrupt Request/Call Progress)

13. Kaki 14, 15, 16, dan 17 (Q1-Q4)

Merupakan kaki output atau input biner 4-bit untuk menghasilkan atau mendeteksi

sinyal DTMF.

14. Kaki 18, Est (Early Steering)

Kaki ini akan menampilkan logika tinggi ketika digital algoritma telah mendeteksi

pasangan tone yang valid.

15. Kaki 19, St/GT (Steering Input / Guard time)

Jika tegangan lebih besar dari VTSt ( steering threshold voltage), maka kaki ini akan

menyebabkan IC menyimpan pasangan tone yang terdeteksi. Selaian itu, tegangan yang

kurang dari VTSt akan menyebabkan IC dapat menerima pasangan tone yang baru.

16. Kaki 20, VDD

IC DTMF terdiri dari filter pembagi band dan fungsi encoder digital. Bagian filter

digunakan untuk mensaklarkan kapasitor dari kelompok filter frekuensi rendah dan kelompok

filter frekuensi tinggi. Sedangkan encoder digital digunakan untuk membaca konfigurasi input

IC DTMF.

2.6.2

Penelitian ini menggunakan IC MT 8870D sebagai TD. Tone decoder (TD) diperlukan

disemua sistem yang menggunakan sinyal DTMF. Diagram blok pada Gambar 2.12

menunjukkan sebuah fungsional dari TD. IC MT 8870D merupakan sebuah TD lengkap yang

berfungsi untuk mengartikan sepasang nada pensinyalan dan memberikan data output yang

sesuai dengan sinyal DTMF yang diterima.[6].

Gambar 2.12.Diagram blok dari IC MT8870D[6]

Komponen utama penyusun TD adalah sebuah bandsplit filter dan digital counting.

Bagian bandslit filter berfungsi untuk memisahkan tone dari kelompok frekuensi tinggi dan

frekuensi rendah, sedangkan bagian digital counting berfungsi untuk mendeteksi dan

menerjemahkan sinyal DTMF kedalam bentuk sandi biner 4 bit. Table 2.5 menunjukkan

Tabel 2.5. Kombinasi data output TD[7]

Dari Tabel 2.5 dapat dilihat bahwa kombinasi frekuensi rendah atau baris 697 Hz

dengan frekuensi tinggi atau kolom 1209 Hz menghasilkan output biner 4 bit 0 0 0 1. Output

biner yang dihasilkan pada TD sebanyak 16 data, sesuai dengan kombinasi 8 buah frekuensi

DTMF yang dapat menyandikan 16 data.

Gambar 2.13.Tanggapan filter [7]

Proses pemisahan nada-nada kelompok frekuensi rendah dan kelompok frekuensi tinggi

dapat dicapai dengan memberikan sinyal DTMF ke input bandpass filter. Bandpass filter

adalah bandwidth yang terhubung dengan kelompok frekuensi rendah dan kelompok frekuensi

penolakan terjadi untuk tone dial tertentu seperti yang ditunjukkan pada Gambar 2.13. Bagian

filter dibagi menjadi dua yang digunakan untuk memperhalus sinyal. Kedua bagian filter

terdiri dari filter untuk kelompok frekuensi rendah dan filter untuk kelompok frekuensi tinggi.

Konfigurasi untuk kaki IC MT8870D pada rangkaian TD dapat dilihat pada Gambar

2.14. Faktor penguatan pada rangkaian konfigurasi IC MT8870D digunakan untuk

menguatkan sinyal DTMF yang akan diterima oleh TD. Penguatan pada rangkaian TD dapat

diperoleh dengan membandingkan nilai dari R2 dan R1 seperti pada persamaan (2.8).

Gambar 2.14.Konfigurasi kaki IC MT8870D [6]

Fungsi Est (Early Steering) pada TD adalah untuk mendeteksi ada atau tidak sinyal

DTMF. Output Est (Early Steering) akan aktif, jika TD mendeteksi adanya sinyal DTMF.

Setelah output Est (Early Steering) aktif sinyal DTMF yang dideteksi akan dikonversi

kedalam kode biner 4-bit dan dimasukkan ke latch output. Pada keadaan ini output Guard time

(GT) akan diaktifkan mengikuti perubahan output dari output Est (Early Steering). Waktu

yang diperlukan guard time (GT) bagi waktu kehadiran tone dapat dicari dengan

menggunakan persamaan 2.5. Jika sinyal DTMF yang dikonversikan dalam bentuk biner telah

dikeluarkan, maka output dari StD akan berlogika tinggi. Gambar 2.15 menunjukkan bentuk

fisik MT8870D dan kegunaan dari masing-masing kaki.

Gambar 2.15.KakiIC MT8870D [6]

Fungsi dari masing-masing kaki dari IC MT8870D adalah sebagai berikut:

1. Kaki 1 dan 2, IN+ dan IN-

Merupakan kaki input non-inverting dan input inverting bagi penguat operasional

internal.

2. Kaki 3, GS ( gain select)

Merupakan kaki output penguat operasional internal.

3. Kaki 4, Vref (reference voltage)

Merupakan tegangan referensi, nilainya sebesar ½ VDD.

4. Kaki 5, INH ( Inhibit )

Bila kaki input ini berlogika tinggi maka akan menonaktifkan tone yang

merepresentasikan karakter-karakter A, B, C, dan D.

5. Kaki 6, PWDM ( power down)

Kaki ini merupakan aktif tinggi. Tegangan yang diberikan pada kaki ini akan

menonaktifkan IC dan menghambat proses osilasi.

6. Kaki 7 dan kaki 8, OSC1 dan OSC2

Merupakan kaki input dan output dari osilator yang terhubung dengan sebuah kristal

sebesar 3,579545 Mhz.

(2.5)

7. Kaki 9, VSS

Kaki ini dihubungkan ke ground (0 V)

8. Kaki 10, TOE (Three State Output Enable)

Jika kaki ini diberikan input logika tinggi, maka output- output Q1-Q4 akan aktif.

9. Kaki 11, 12, 13, dan 14 (Q1-Q4)

Merupakan kaki output biner 4-bit hasil dari decoder sinyal DTMF.

10. Kaki 15, StD (Delayed Steering)

Kaki ini akan menampilkan logika tinggi ketika pasangan tone yang diterima telah

dikeluarkan.

11. Kaki 16, Est (Early Steering)

Kaki ini akan menampilkan logika tinggi ketika digital algoritma telah mendeteksi

pasangan tone yang valid.

12. Kaki 17, St/GT (Steering Input / Guard time)

Jika tegangan lebih besar dari VTSt ( steering threshold voltage), maka kaki ini akan

menyebabkan IC menyimpan pasangan tone yang terdeteksi. Selain itu, tegangan yang

kurang dari VTSt akan menyebabkan IC dapat menerima pasangan tone yang baru.

13. Kaki 18, VDD

Merupakan input sumber tegangan positif yang biasanya sebesar 5V.

Bagian ini akan mendeskripsikan tentang Mikrokontroler AVR ATTINY2313 yang

merupakan pembangkit IC TG untuk dapat menghasilkan deretan tone [8]. Beberapa bagian

yang akan dibahas diantaranya yaitu arsitektur mikrokontroler, gambaran mengenai instruksi,

mode pengalamatan memori dan program, serta peripheral-peripheral pendukung yang

terdapat dalam Mikrokontroler ATTINY2313.

Mikrokontroler AVR ATTINY2313 merupakan mikrokontroler 8 bit dengan teknologi

CMOS (Complementary Metal Oxide Semiconductor) yang dibangun menggunakan arsitektur

RISC (Reduce Intruction Set Computer) mampu melakukan sebuah intruksi dalam satu siklus

clock. Teknologi arsitektur RISC (Reduce Intruction Set Computer) tersebut yang

Per Second) per MHz yang memungkinkan perancangan dapat dioptimalkan dalam konsumsi

daya dan kecepatan proses. Gambar 2.16 menunjukkan diagram blok mikrokontroler

ATTINY2313.

AVR menggabungkan teknologi RISC (Reduce Intruction Set Computer) dengan 32

register multifungsi (General Purpose Register) yang terhubung langsung dengan ALU

(Arithmetic Logic Unit), sehingga memungkinkan dalam satu putaran clock 2 buah register

yang terpisah diakses. Arsitektur ini menghasilkan mikrokontroler yang mempunyai kode

yang efisien sampai sepuluh kali lebih cepat dibandingkan dengan mikrokontroler

berarsitektur CISC (Complex Intruction Set Computer).

Gambar 2.16. Diagram blok fungsional ATTINY2313 [8]

AVR ATTINY2313 mempunyai bagian-bagian antara lain: 2 kilo bytes in-system

programmable flash, 128 bytes EEPROM (Electrical Erasable Programmable Random

Access Memory), 128 bytes SRAM (Static Random Access Memory), 15 line input/output, 32

Asyncronous Receiver Transmitter), Timer/Counter, Interupsi internal dan eksternal, osilator

internal, Watchdog timer, dan SPI (Serial Port Interface) untuk in-system programming.

Mikrokontroler ATTINY2313 dirancang menggunakan teknologi ATMEL non-valatile

memory yaitu memori yang tidak hilang walaupun tidak ada catu daya. On-chip In-System

Programmable Flash membuat memori program dapat diprogram kembali melalui SPI serial

tanpa menggunakan downloader board.

Konsep pengaksesan register file yang cepat terdiri dari 32x8 bit register fungsi umum

dengan waktu akses dalam satu siklus clock. Dalam satu siklus clock mempunyai arti yaitu

satu operasi ALU (Arithmetic Logic Unit) dikerjakan dan dua buah register diakses, kemudian

hasil dari operasi ini disimpan kembali ke dalam register file. Gambar 2.17 menunjukan

arsitektur dari AVR ATTINY2313 [8].

Enam dari 32 register multifungsi dapat digunakan sebagai 3 (tiga) buah pasangan

register untuk pengalamatan data tak langsung (Indirect Data Addressing). Ketiga register

tambahan ini yaitu16 bit register X, register Y, dan register Z. ALU digunakan untuk operasi

aritmatika dan logika antara register dengan register, atau antara register dengan suatu nilai

konstanta tertentu. Memori I/O terdiri dari 64 alamat untuk fungsi-fungsi dari peripheral

seperti Control register, timer/counter, A/D Converters, dan fungsi-fungsi I/O lainnya.

!

Mikrokontroler AVR dilengkapi dengan peripheral pendukung yang built in dalam satu

chip. Peripheral dalam AVR ATTINY2313 secara umum akan dijelaskan sebagai berikut.

1. two kilo byte in-system programable flash memory

ATTINY2313 dilengkapi two kilo byte in-system programable flash untuk

menyimpan program. Memori ini mampu dihapus atau ditulis sampai 1000 kali.

2. EEPROM (Electrically Erasable Programmable Read Only Memory)

ATTINY2313 mempunyai 128 bytes EEPROM yang diatur terpisah dengan

data space, dengan tiap byte dapat dibaca atau ditulis sendiri. EEPROM dapat

menyimpan data ketika program sedang bekerja dan data tidak akan hilang saat

catu daya dimatikan. EEPROM dapat dihapus dan ditulis sebanyak 100.000 kali.

3. Fiveteen General Purpose Input/Output Lines

ATTINY2313 mempunyai dua port multifungsi yang terdiri dari delapan buah

kaki pada PORTB dan tujuh kaki pada PORTD. Kedelapan kaki dari PORTB yaitu

PB0, PB1, PB2, PB3, PB4, PB5, PB6, dan PB7. Ketujuh kaki dari PORTD yaitu

PD0, PD1, PD2, PD3, PD4, PD5, dan PD6. Kedua port tersebut dapat diprogram

sebagai port input dan port output secara terpisah pada tiap-tiap bit. Selain itu,

dapat juga digunakan untuk fungsi alternatif lain seperti terlihat dalam tabel 2.6

dan tabel 2.7.

Tabel 2.6. Fungsi Alternatif dari Port B [8]

Port Pin Fungsi Alternatif

PB0 AINO (Analog comparator positive input)

PB1 AIN1 (Analog comparator negative input)

PB2 OC0A (Timer/Counter0 output comper A match output)

PB3 OC1A (Timer/Counter1 output comper A match output)

PB4 OC1B (Timer/Counter1 output comper B match output)

PB5 MOSI (Data input line for memory uploading)

PB6 MOSO (Data output line for memory uploading)

Tabel 2.7. Fungsi Alternatif dari Port D [8]

Port Pin Fungsi Alternatif

PD0 RXD (Receive data input for the UART)

PD1 TXD (Transmit data output for the UART)

PD2 INT0 (External interrupt 0 input)

PD3 INT1 (External interrupt 1 input)

PD4 T0 (Timer/Counter 0 external input)

PD5 T1 (Timer/Counter 1 external input)

PD6 ICP (Timer/Counter 1 input capture pin)

"

Mikrokontroler ATTINY2313 mempunyai 20 kaki, 15 kaki diantaranya digunakan

sebagai port paralel [8]. Satu port paralel terdiri dari 7 kaki dan 8 kaki, dengan demikian 15

kaki tersebut membentuk 2 buah port paralel. Kedua port tersebut adalah port B dan port D.

Konfigurasi kaki AVR ATTINY2313 bisa dilihat pada Gambar 2.18.

Gambar 2.18. Kaki AVR ATTINY2313 [8]

Fungsi dari masing-masing kaki dari ATTINY2313 adalah sebagai berikut:

1. Kaki 1, RST

merupakan input reset yang berfungsi untuk mereset mikrokontroler dengan

memberikan logika ”1” selama 2 mc (machine cycle).

2. Kaki 2, 3, 6, 7, 8, 9, dan 11 (PD0- PD6)

Port D mempunyai 7 bit I/O data yaitu PD0, PD1, PD2, PD3, PD4, PD5, dan PD6.

berfungsi sebagai input dengan memberikan logika ”1”. Sebagai output, port ini dapat

memberikan sink output keempat buah input TTL. Sedangkan sebagai fungsi khusus

dalam hal ini untuk In-System Programming (ISP), port D mempunyai keterangan sebagai

berikut:

a. Kaki 2, PD.0 atau RXD sebagai serial input port.

b. Kaki 3, PD.1 atau TXD sebagai serial output port.

c. Kaki 6, PD.2 atau CKOUT/XCK/INTO sebagai external interrupt 0 port atau

USART external clock input/output.

d. Kaki 7, PD.3 atau INT1 sebagai external interrupt 1 port.

e. Kaki 8, PD.4 atau TO sebagai external timer 0 input port.

f. Kaki 9, PD.5 atau OcoB/T1 sebagai external timer 1 input port atau timer/counter

0 output compare B match output.

g. Kaki 11, PD.6 atau ICP sebagai timer/counter 1 input capture pin.

3. Kaki 4, XTAL1 sebagai oscillator input

4. Kaki 5, XTAL2 sebagai oscillator output

5. Kaki 10, GND sebagai ground

6. Kaki 12, 13, 14, 15, 16, 17, 18, dan 19 (PB.0- PB.7)

Port B mempunyai 8 bit I/O data yaitu PB0, PB1, PB2, PB3, PB4, PB5, PB6 dan

PB7. Port ini mempunyai internal pull up dan berfungsi sebagai input dengan memberikan

logika ”1”. Sebagai output, port ini dapat memberikan sink output keempat buah input

TTL. Sedangkan sebagai fungsi khusus dalam hal ini untuk In-System Programming

(ISP), dapat berperan sebagai:

a. Kaki 19, PB.5 atau D1/MOSI digunakan untuk serial data input.

b. Kaki 18, PB.6 atau D0/MOSO digunakan untuk serial data output.

c. Kaki 17, PB.7 atau SCK digunakan untuk serial clock input.

7. VCC pada kaki 20 sebagai input suplai tegangan.

2.7.4 On-Chip Oscillator

Mikrokontroler mempunyai osilator yang tersedia pada kemasan IC tersebut sebagai

ATTINY2313 dihubungkan dengan sebuah kristal dan kapasitor yang terhubung dengan

ground. Gambar 2.19 menunjukkan cara menghubungkan kristal yang digunakan sebagai

sumber clock dengan mikrokontroler ATTINY2313. Besar kapasitor yang terhubung dengan

sumber clock tergantung pada jenis dari sumber clock tersebut. Jika sumber clock berupa

kristal, maka besar kapasitor yang terpasang adalah kira-kira 10pF samapai 30pF. Jika jenis

sumber clocknya berupa keramik, maka besar kapasitor yang terpasang kira-kira 10pF sampai

40pF.

Gambar 2.19.Menghubungkan sumber clock [8]

2.7.5 Timer/counter

ATTINY2313 memiliki dua buah Timer/counter yang masing-masing mempunyai

sileksi prescale terpisah dari prescale yang sama [8]. Pertama adalah timer/counter 8 bit yang

dapat digunakan sebagai timer dengan sumber clock dari prescale CK atau sumber clock yang

diambil dari kaki T0 (fungsi lain dari PD.4).

Kedua timer/counter 1 merupakan timer/counter 16 bit yang digunakan sebagai timer.

Timer/counter 1 mendapat sumber clock dari prescale CK atau sumber clock yang diambil

dari kaki T1 (fungsi lain dari PD.5). Timer/counter 1 dapat juga digunakan sebagai PWM

(Pulse Width Modulator) yang dikeluarkan melalui kaki OC1A (fungsi lain dari kaki PB.3).

2.8

Mixer Audio

Mixer audio adalah suatu perangkat yang digunakan untuk mencampurkan dua sinyal

menjadi satu sinyal [7]. Mixer juga digunakan untuk menghasilkan frekuensi yang lain dengan

penggabungan frekuensi dari masing-masing sinyal. Rangkaian mixer audio dengan dua input

Kapasitor yang terdapat di r

melewatkan sinyal sinus. Gam

Gambar 2.20. R

2.9 Transistor sebagai sa

Komponen transistor d

yang ideal [7]. Saklar adalah

keadaan off. Keadaan on meru

dengan kata lain tidak ada r

merupakan suatu keadaan tida

ditunjukkan pada Gambar 2.

transistor harus dapat berpinda

daerah cut-off (saklar dalam ke

(a)

Gambar 2.2

(b) Grafik outpu

Titik cut-off adalah tit

mempunyai IB sama dengan n

rangkaian berfungsi untuk menghalangi sinyal

mbar 2.20 menunjukkan rangkaian mixer audio d

Rangkaian mixer audio dengan dua input [9]

saklar

dapat digunakan sebagai saklar, walaupun buka

h suatu alat yang mempunyai dua keadaan yaitu

rupakan suatu keadaan saat arus bisa mengalir de

resistivitas dan besar tegangan sama dengan n

idak ada arus yang mengalir. Rangkaian transisto

2.21(a). Agar dapat berfungsi sebagai saklar,

dah – pindah dari daerah saturasi (saklar dalam k

keadaan “off”) seperti terlihat pada Gambar 2.21

(b)

.21. (a) Rangkaian transistor sebagai saklar

put dari transistor, keadaan cut-off dan saturasi [7

titik dimana garis beban memotong kurva IB =

nol dan tidak ada IC. Hal ini berarti transistor tu

al DC dan hanya

dengan dua input.

kan sebagai saklar

itu keadaan on dan

dengan bebas, atau

nol. Keadaan off

stor sebagai saklar

, maka titik kerja

keadaan “on”) ke

1(b).

7]

= 0. Titik cut-off

(2.7)

dari garis beban dan kurva IB = IB(sat) disebut saturasi. IB pada titik perpotongan sama dengan

IB(sat) dan IC maksimum. Agar transistor dalam keadaan saturasi, IB harus minimal sebesar IC

maksimal dibagi dengan penguatan arus (hFE) dari transistor seperti dinyatakan dalam

persamaan berikut:

( )

FE sat C B

h I

I ≥

IC saat saturasi adalah:

( )

C CC sat

C

R V

I =

Jika IB lebih kecil dari pada IB(sat), maka transistor beroperasi pada daerah aktif. Daerah

aktif transistor terletak di suatu tempat di antara titik saturasi dan titik cut-off. Selain itu, saat

IB lebih besar dari pada IB(sat), IC sama dengan Vcc dibagi dengan RC. Titik saturasi dihasilkan

oleh perpotongan garis beban dengan setiap IB yang bertambah besar.

Penjumlahan tegangan disekitar loop masukan memberikan:

IBRB+VBE-VBB = 0

dengan IB diperoleh dari:

B BE BB

R V V − =

B

I

Transistor menjadi saklar off, jika IB lebih besar atau sama dengan IB(sat) dan titik kerja

Q berada pada ujung atas dari garis beban seperti ditunjukkan pada Gambar 2.21 (b).

Transistor menjadi saklar on, jika IB sama dengan nol dan transistor bekerja pada ujung bawah

dari garis beban.

2.10 Demultiplekser 4 ke 16 CD4514

Demultiplekser terdiri dari rangkain TTL yang mendekodekan empat buah kode biner

ke salah satu dari 16 output [10]. Jika kaki inhibit diberi logika rendah, maka salah satu dari

16 output akan mempunyai logika tinggi sesuai dengan alamat yang ditunjuk 4 buah kode

biner sebagai input dan output yang lain mempunyai nilai logika rendah. Daftar dari 16 sandi

dan fungsi decoding dapat dilihat pada Tabel 2.8. Gambar 2.22 menunjukkan diagram koneksi

dari IC CD4514.

(2.9) (2.8)

Gambar 2.22. Diagram koneksi IC CD4514 [10]

Tabel 2.8. Daftar dari 16 sandi dan fungsi decoding [10]

desimal

Input biner

D3D2D1D0

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

1 0 0 0 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0

2 0 0 1 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0

3 0 0 1 1 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0

4 0 1 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0

5 0 1 0 1 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0

6 0 1 1 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0

7 0 1 1 1 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0

Tabel 2.8. (Lanjutan) Daftar dari 16 sandi dan fungsi decoding [10]

desimal

Input biner

D3D2D1D0

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

9 1 0 0 1 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0

10 1 0 1 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0

11 1 0 1 1 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0

12 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0

13 1 1 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0

14 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0

15 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1

2.11 Rangkaian penampil

Rangkaian penampil ini berfungsi untuk mengubah data berupa tegangan digital

menjadi informasi yang dapat dilihat. Rangkaian penampil terdiri dari rangkaian decoder BCD

ke seven segment dan seven segment.

2.11.1

Decoder

BCD ke

seven segment

Pada penelitian ini, decoder BCD ke seven segment menggunakan IC 74LS48. Decoder

seven segment adalah rangkaian untuk menterjemahkan bilangan biner agar dapat ditampilkan

pada display seven segment, misalkan 0 (nol) dalam biner adalah 0000 pada display seven

segment [11]. Decoder ini sering disebut sebagai decoder 4 ke 10.Decoder akan memberikan

logika tinggi pada semua kaki (a,b,c,d,e,f) kecuali pin g dalam menampilkan angka 0 (nol) ke

seven segment.

Input decoder BCD ke seven segment ada empat buah yaitu A, B, C, dan D. output

yang dihasilkan oleh decoder BCD ke seven segment ada tujuh output yang terhubung ke

dari IC 74LS48. Ketujuh output tersebut adalah a, b, c, d, e, f, dan g. Tabel kebenaran dari

decoder BCD ke seven segment dapat dilihat pada Tabel 2.9.

Gambar 2.23. Konfigurasi kaki IC 74LS48 [11]

Tabel 2.9.Tabel kebenaran 74LS48 [11]

2.11.2

Seven Segment

Seven segment merupakan komponen elektronika yang dapat digunakan untuk

menampilkan karakter angka [11]. Seven segment didesain dari tujuh led dan 1 dot point

Gamb

Seven segment dapat d

common anode dan common

menggabungkan seluruh kaki

dan dapat menampilkan, jika

segment yang menggabungka

Common cathode aktif dan

menunjukkan jenis dari seven s

(a)

Gambar 2.25. Jenis sev

bar 2.24. Konfigurasi seven segment [11]

dibedakan menjadi dua menurut cara penyam

n cathode. Common anode adalah jenis seve

ki anode dari LED ke satu kaki yaitu Vcc. Com

ika diberi logika rendah. Common cathode ad

kan seluruh kaki cathode dari LED ke satu ka

n dapat menampilkan, jika diberi logika tingg

segment.

(b)

ven segmen(a)Common anode(b)Common cat

mbungannya yaitu

en segment yang

mmon anode aktif

adalah jenis seven

kaki yaitu ground.

ggi. Gambar 2.25

PE

3.1 Diagram Blok Sistem

Sistem komunikasi radi penyusun sistem. Gambar 3.1 AM FH.

Gambar 3.1. Blok diag

Bagian pemancar (Trans untuk membangkitkan sinya frekuensi carrier yang telah te (Receiver) secara bergantian tersinkronisasi, pada bagian untuk mendeteksi sinyal mana

3.2 Diagram Blok dan

FrequencyHopping

Rancangan subsistem si bagian penerima. Gambar 3.2 pemancar AM FH. Subsistem decoder counter dan TGDTM sebagai pencacah saluran input

ERANCANGAN ALAT

em Komunikasi Radio AM Frequency Ho

dio AM frequency hopping (FH) mempunyai blok 3.1 menunjukkan blok diagram umum sistem kom

agram umum sistem komunikasi radio AM FH

ansmitter) terdapat blok tone generator (TG) ya nyal tersinkronisasi dari empat frekuensi carri

tersinkronisasi tersebut kemudian diterima oleh pe n sesuai waktu yang telah ditentukan. Saat mene penerima terdapat blok tone decoder (TD) ya na yang sesuai.

n Penjelasan Umum Pemancar dan Pen

sinkronisasi ini terdiri dua bagian, yaitu bagian p menunjukkan diagram blok subsistem sinkronis em sinkronisasi bagian pemancar AM dengan F

MF (Dual Tone Multi Frequency). Decoder count input generator DTMF, sehingga generator D

opping

blok-blok utama omunikasi radio

yang berfungsi rier. Keempat h penerima AM enerima sinyal yang berfungsi

enerima AM

menghasilkan sinyal-sinyal DTMF secara berurutan. Sinyal-sinyal yang dihasilkan oleh subsistem sinkronisasi dicampur dengan sinyal informasi oleh audio mixer. Sinyal hasil pencampuran kemudian ditransmisikan ke bagian pemancar sebelum dipancarkan dan diterima oleh TD pada penerima AM.

ANTENA

SINYAL INFORMASI

TONE G

![Table 2.4. Output IC MT8888C [5]](https://thumb-ap.123doks.com/thumbv2/123dok/1678559.2076252/34.612.182.447.85.445/table-output-ic-mt-c.webp)

![Gambar 2.14. Konfigurasi kaki IC MT8870D [6]](https://thumb-ap.123doks.com/thumbv2/123dok/1678559.2076252/38.612.187.438.236.459/gambar-konfigurasi-kaki-ic-mt-d.webp)

![Gambar 2.16. Diagram blok fungsional ATTINY2313 [8]](https://thumb-ap.123doks.com/thumbv2/123dok/1678559.2076252/41.612.196.467.260.561/gambar-diagram-blok-fungsional-attiny.webp)

![Gambar 2.19. Menghubungkan sumber clock [8]](https://thumb-ap.123doks.com/thumbv2/123dok/1678559.2076252/46.612.220.400.215.342/gambar-menghubungkan-sumber-clock.webp)

![Gambar 2.22. Diagram koneksi IC CD4514 [10]](https://thumb-ap.123doks.com/thumbv2/123dok/1678559.2076252/49.612.93.513.359.695/gambar-diagram-koneksi-ic-cd.webp)

![Tabel 2.8.�(Lanjutan)�Daftar dari 16 sandi dan fungsi decoding [10]](https://thumb-ap.123doks.com/thumbv2/123dok/1678559.2076252/50.612.92.513.87.371/tabel-lanjutan-daftar-sandi-fungsi-decoding.webp)

![Gambar 2.23. Konfigurasi kaki IC 74LS48 [11]](https://thumb-ap.123doks.com/thumbv2/123dok/1678559.2076252/51.612.174.457.288.598/gambar-konfigurasi-kaki-ic-ls.webp)

![Gambar 2.25. Jenis sevven segmen (a) Common anode (b) Common catthode [11]](https://thumb-ap.123doks.com/thumbv2/123dok/1678559.2076252/52.612.238.420.62.196/gambar-jenis-sevven-segmen-common-anode-common-catthode.webp)