JETri,

Volume 8, Nomor 1, Agustus 2008, Halaman 1-16, ISSN 1412-0372PERANCANGAN MIXER UP-CONVERSION CMOS

UNTUK RANGKAIAN RF TERINTEGRASI

Cecilia Susilawati

Dosen Jurusan Teknik Elektro – Fakultas Teknologi Industri Universitas Trisakti

Abstract

The design, analysis and implementation of a high frequency 1-3GHz tunable pure NMOS Quadrature Up-Conversion mixer topology are presented. The mixer is implemented in a deep submicron 0,25 µm CMOS process technology. Utilizing an off-chip tunable inductor achieves tunable range of frequency. Various passive components had been incorporated in its circuitry to increase the linearity of the topology. The mixer, which is a configuration of a balanced modulator, is composed from a Parallel Structure Low Voltage Multiplier topology, a High Gain Phase Shifting network and a Differential Cascade amplification stage at the output. Various topology of four quadrant multiplier, biased in different region of operation has been simulated and analyzed. The utilized topology requires fewer amount of stacked transistors, thus reducing the voltage headroom requirement of the circuitry. The proposed high gain phase shifter relaxes the requirement of cascading several stages of limiting amplifier at the output. Operating from a power supply of 2.0V, it consumes 150mW of power, with an OIP3 of 0dBm and 1dB compression level of 4.6dB.

Keywords: Balanced Modulator, CMOS analog integrated circuit, Mixers, Phase shifters,

RFIC

1. Pendahuluan

Pengirim dan penerima wireless dapat dipisahkan secara konseptual menjadi dua bagian yaitu bagian baseband dan bagian radio frekuensi (RF). Bagian RF dari pengirim mengubah sinyal yang telah diproses ke kanal yang diinginkan dan melepaskan sinyal ke media (Razavi, 1998: 5). Umumnya rangkaian RF CMOS dirancang menggunakan sirkuit yang sama dengan bagian bipolarnya, sehingga dibutuhkan disipasi daya yang tinggi.

Mixer up – conversion digunakan pada pengirim dari transceiver,

mengubah sinyal input menjadi komponen dengan frekuensi lebih tinggi agar transmisi lebih dapat diandalkan. Hal ini juga meningkatkan waktu hidup per berat dari batere yang digunakan. Pengecilan ukuran transistor CMOS juga akan meningkatkan kecepatan sirkuit dan kepadatannya (Hastings, 2001: 10). Perancangan dari mixer up – conversion pada teknologi CMOS standar akan dibahas dan simulasi menggunakan program P-Spice.

Cecilia Susilawati. Perancangan Mixer Up-Conversion CMOS Untuk Rangkaian RF Terintegrasi

2. Implementasi Rangkaian

2.1. Perancangan Multiplier tegangan rendah

Untuk mengurangi konsumsi daya pada sistem komunikasi, tegangan rendah sangat cocok digunakan untuk merancang IC RF namun terdapat komponen pasif yang butuh lebih banyak daya. Tegangan rendah diberikan dengan mengurangi jumlah dari transistor, yang akan mengurangi sumber tegangan dc (Vdd>VT) untuk setiap pasangan transistor, sehingga

sirkuit turun hingga skala teknologi submikron. Dengan tegangan VT 0,72

V, telah direalisasikan pada teknologi proses CMOS TSMC 0,25μm. Rangkaian paralel dari pengali (multiplier) 4 kuadran CMOS digunakan sebagai inti dari mixer, prinsip operasinya diberikan pada Gambar 1.

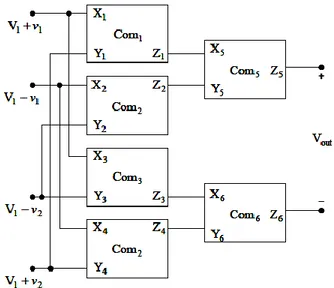

Gambar 1. Pengali Analog dengan menggunakan 6 buat penggabung. Pada Gambar 1., ke 6 blok (com1 – com6) disebut penggabung

(combiner) sinyal masukkan untuk menciptakan keluaran. Persamaan

output-nya dapat dinyatakan:

Zi = A1Xi 2 + A2Yi 2 + A3Xi + A4Yi + A5 , (i = 1 - 4) (1) Zi = B1Xi 2 + B2Yi 2 + B3Xi + B4Yi + B5 , (i = 5,6) (2)

dimana

Cecilia Susilawati. Perancangan Mixer Up-Conversion CMOS Untuk Rangkaian RF Terintegrasi

Persamaan (1) dan (2) berbeda dimensi transistor W/L pada penggabung keluaran (Com5-6) dan masukkan (Com1-4). Keluaran dari Com5

dan Com6 juga berbeda. Masukkan dari X1 dan X3 dinyatakan sebagai

V1+v1 dan masukkan dan X2 dan X4 dinyatakan sebagai V1-v1. Hal ini

dikarenakan tegangan dc common mode adalah V1 dan dipengaruhi oleh

tegangan sinyal masukkan +v1, dimana Y2 dan Y3 ditulis sebagai V1 - v2

dan Y1 dan Y4 sebagai V1 + v2. Keluaraannya adalah Vout = Z5 - Z6.

Vout = 8B1(2A1V1 + A3)(1A2V1 + A4)v1v2 = K'v1v2 (3)

Dengan mengasumsikan B1 = B2 dan B3 = B4, apabila ada

perbedaan koefisien akan mengakibatkan timbul sinyal yang tidak diinginkan pada bagian keluaran, sehingga respon non linear pada rangkaian. Distorsi seperti nilai dc offset, frekuensi kapasitor yang tinggi, dan interferensi pada kanal mempengaruhi sinyal. Dari persamaan (3) keluaran merupakan perkalian linear antara v1v2 dan konstanta K’. Realisasi

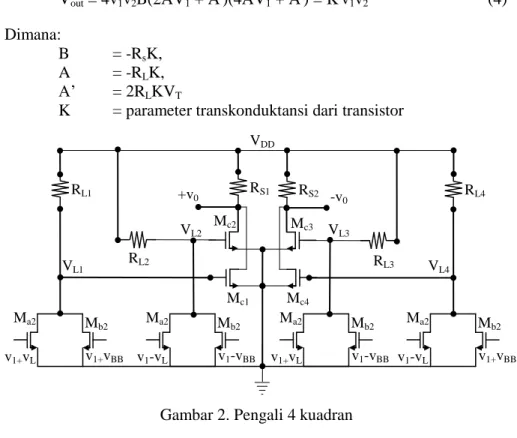

rangkaian pada Gambar 1. diberikan pada Gambar 2., keluaran yang timbul:

Vout = 4v1v2B(2AV1 + A')(4AV1 + A') = K'v1v2 (4)

Dimana:

B = -RsK,

A = -RLK,

A’ = 2RLKVT

K = parameter transkonduktansi dari transistor

Gambar 2. Pengali 4 kuadran

Mc1 Mc4 VDD VL1 VL4 v1+vBB v1+vL Ma2 Mb2 v1-vBB v1-vL Ma2 Mb2 v1+vBB v1-vL Ma2 Mb2 v1-vBB v1+vL Ma2 Mb2 RL4 RL1 RS1 RS2 Mc2 Mc3 RL2 VL2 VL3 +v0 -v0 RL3

Cecilia Susilawati. Perancangan Mixer Up-Conversion CMOS Untuk Rangkaian RF Terintegrasi

Sehingga fungsi perkalian dapat direalisasikan. Dari persamaan (4), v1 = vL merupakan sinyal pembawa masukkan, didapat dari osilator yang

dikendalikan oleh tegangan eksternal (VCO), v2=vBB yang merupakan

sinyal masukkan. Walaupun K terbalik dari VGS – VT untuk model transistor

orde 2, hal ini diasumsikan konstan untuk perhitungan dan variasi yang timbul karena hal ini dianggap tiada.

2.2. Penggeser Phasa dan Perancangan Penguat cascade 2.2.1. Penggeser Phasa

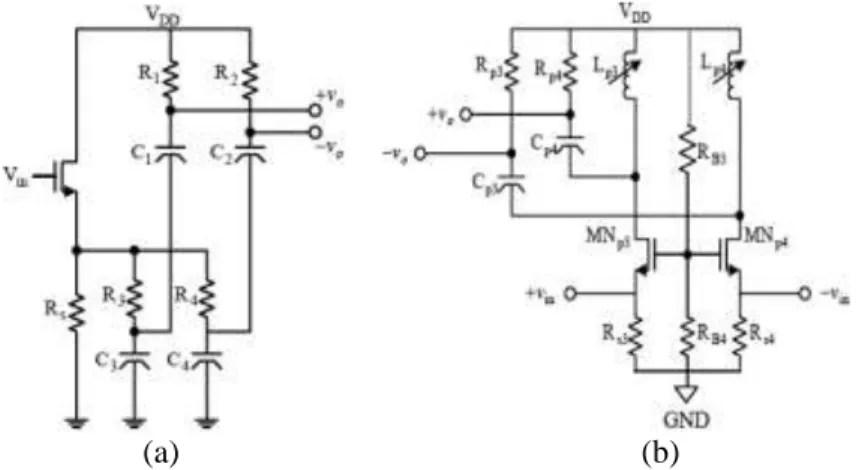

Perancangan dari penggeser phasa sangat penting dalam mixer, karena untuk menekan komponen sideband yang tidak diinginkan. Penggeser phasa 90o tambahan yang terdiri dari rangkaian jembatan CR-RC, Gambar 3a, memiliki akurasi phasa yang baik tetapi memiliki kesalahan amplitudo yang besar. Rangkaian jembatan diikuti oleh beberapa bagian dari penguat untuk mengatasi kesalahan amplitudo tersebut.

Rangkain penggeser phasa 90o dengan penguatan besar ditunjukkan Gambar 3b. rangkaian ini terdiri dari induktor yang dapat diubah (LP3 dan

LP4) untuk mengatur amplitudo dari gelombang keluaran sehingga bagian –

bagian selanjutnya tidak saturasi. Masukkan akan melalui resistor (RS3 dan

RS4) untuk meningkatkan kelinearan sistem. Rangkaian ini memiliki

toleransi kesalahan phasa sebesar 0,1% dan kapasitor penghalang dc tidak dibutuhkan karena potensial keluarannya adalah Vpp, dimana Vpp diset pada

nilai dc yang konstan. Vpp juga mengakibatkan bias masukkan dc, Vpp<Vdd.

(a) (b)

Gambar 3.a. Rangkaian Penggeser Phasa RC-CR konvensional, b. Rangkain Penggeser Phasa dengan penguatan tinggi.

Cecilia Susilawati. Perancangan Mixer Up-Conversion CMOS Untuk Rangkaian RF Terintegrasi

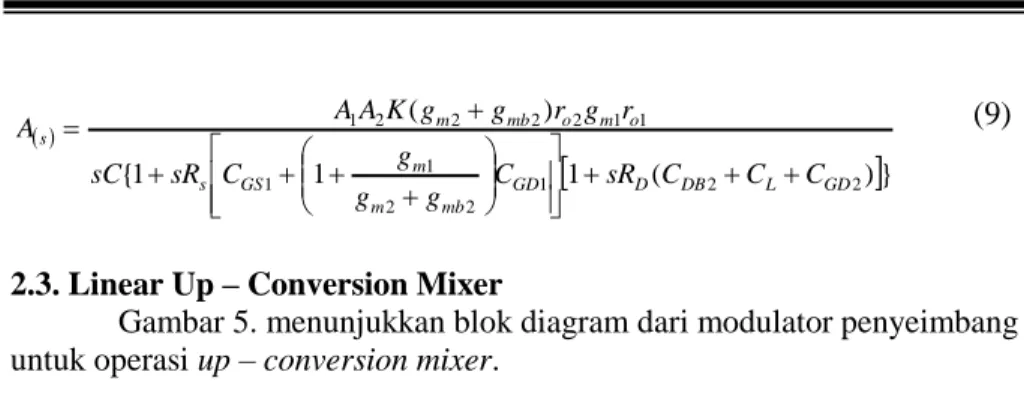

2.2.2. Perancangan Penguat cascade

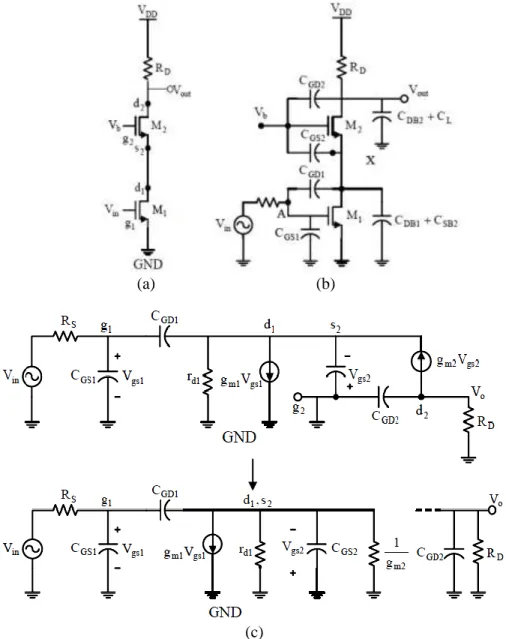

Gambar 4. menunjukkan diagram sederhana dari penguat cascade (Razavi, 2001: 25).

(a) (b)

(c)

Gambar 4.a. Penguat Cascade, b.Model Frekuensi Tinggi untuk Penguat Cascade, c.Rangkaian Ekuivalen Sinyal Rendah Orde 2

Cecilia Susilawati. Perancangan Mixer Up-Conversion CMOS Untuk Rangkaian RF Terintegrasi

Transistor M2 memisahkan terminal masukkan dan keluaran dan

mencegah penguatan miller dari kapasitor antara Gatedan Drain dari M1.

Integrasi dari penguatan cascade frekuensi tinggi ini meningkatkan sensitifitas dari bentuk gelombang keluaran. Pada Gambar 4., transistor M2

akan meningkatkan impedansi keluaran M1 dengan (gm2 + gmb2)ro2.

Hambatan keluarannya menjadi:

Rout (gm2 + gmb2) ro2 ro1 (5)

Sehingga penguatan tegangan keluaran juga meningkat. Penguatannya diberikan oleh persamaan (6).

1 ( )

1 1 ) ( 2 2 1 2 2 1 1 1 1 2 2 2 GD L DB D GD mb m m GS s o m o mb m s C C C sR C g g g C sR r g r g g A (6)Karena 1/gm2<<rd pada Gambar 4.(c)., terlihat antara drain dari M1 dan

ground dari hambatan total kurang lebih 1/gm2. CGS2 and 1/gm2

menghasilkan fungsi alih dengan frekuensi:

T m GS g C 2 2 2 1 1 (7)

dimana lebih tinggi daripada frekuensi yang timbul karena adanya interaksi dari Rs dan kapasitor masukkan CGS1. Dalam penghitungan tegangan pada

drain M1, CGS2 dapat ditiadakan.

Vd1 -gm1Vgs1 2 1 m g -Vgs1 (8)

Persamaan (8) didapat dengan mengasumsikan kedua transistor M1

dan M2 sama dalam hal dimensi dan parameternya (gm1 ≈ gm2) dan

penguatan antara g1 dan d1 kurang lebih -1 dan didapat mengaplikasikan

teorema Miller untuk mengganti kapasitor jembatan CGD1 dengan kapasitor

2CGD1 antara d1 dan ground. Efek dari kapasitor Miller ini terjadi pada

operasi frekuensi tinggi, bila transistor M1 dan M2 sama dalam nilai

Cecilia Susilawati. Perancangan Mixer Up-Conversion CMOS Untuk Rangkaian RF Terintegrasi

1 ( )

} 1 1 { ) ( 2 2 1 2 2 1 1 1 1 2 2 2 2 1 GD L DB D GD mb m m GS s o m o mb m s C C C sR C g g g C sR sC r g r g g K A A A (9)2.3. Linear Up – Conversion Mixer

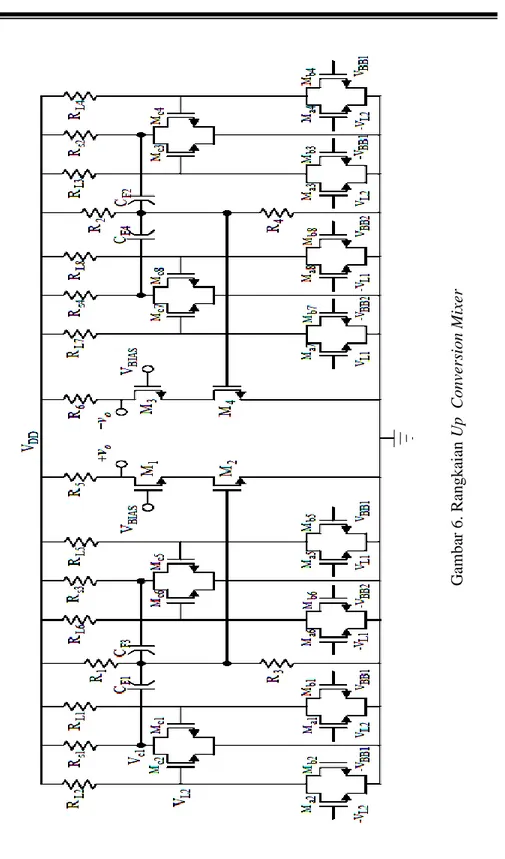

Gambar 5. menunjukkan blok diagram dari modulator penyeimbang untuk operasi up – conversion mixer.

Gambar 5. Diagram Blok Up Conversion Mixer

Keluaran dari up – conversion mixer dirasakan berbeda untuk menekan distorsi. Tegangan masukkan dikopling melalui kapasitor untuk menjadi masukkan dari penguat cascade untuk menghindari kopling dc.

Setiap bagian dari transistor mewakili penggabung, disusun secara seimbang untuk menghindari distorsi karena ketidakcocokan dari transistor. Hambatan pasif diberikan utnk meningkatkan kelinearan rangkaian. Penguatan dari rangkaian up – converter diberikan pada Persamaan (7) dimana A1 dan A2 adalah amplitudo pembawa dan sinyal baseband dan C =

CF1 = CF2 = CF3 = CF4, yang merupakan kapasitor kopling pada Gambar 6.

Analisa performa dari mixer ini diukur melalui IIP3 (intercept point orde 3),

IIP2 (Intercept point orde 2), kehilangan akibat konversi dan feedthrough

suppression. Tidak mudah untuk menilai kualitas dari suatu perangcangan.

Suatu parameter E dapat didefinisikan:

E =

10 ) ( ) ( 3 dBm LO dBm IIP power (10)Sudah merupakan aturan bahwa IIP3 dai perancangan mixer yang baik bernilai 10dB diatas daya pembawa, yang membuat nilai E = 1. Nilai E tersebut menentukan performa dari mixer. Gambar 6. adalah Rangkaian perancangan Up – Conversion Mixer tanpa rangkaian penggeser phasa.

+900 +900 sin ωBBt

sin ωLOt

Cecilia Susilawati. Perancangan Mixer Up-Conversion CMOS Untuk Rangkaian RF Terintegrasi G am ba r 6. R an gka ian U p C onve rs ion M ixe r

Cecilia Susilawati. Perancangan Mixer Up-Conversion CMOS Untuk Rangkaian RF Terintegrasi

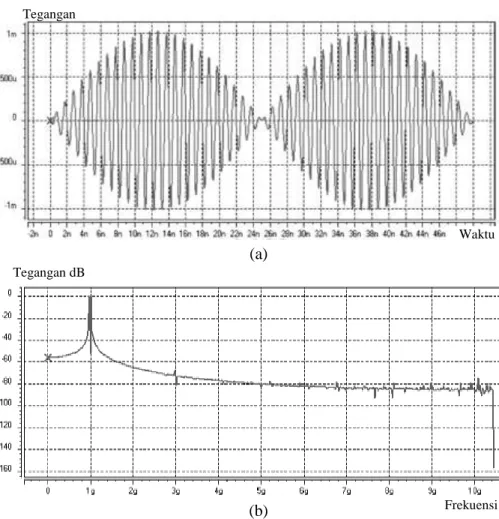

3. Hasil simulasi

Gambar 7.(a). menunjukkan keluaran dari pengali antara tegangan analog 4 kuadran pada 20 MHz dengan frekuensi baseband dan frekuensi osilator 1 GHz. Gambar 7.(b). menunjukkan koefisien puncak transformasi Fourier pada frekuensi sideband bawah dan sideband atas, yang ada pada 0,98 GHz dan 1,02 GHz. Simulasi menggunakan tegangan supply 1,2 Vdc

dan disipasi daya 28,85 mW. Tegangan keluaran adalah 2 mVpp.

(a)

(b)

Gambar 7.(a). Bentuk Gelombang double sideband suppressed carrier pada sinyal baseband 20MHz, (b). Respon Transformasi Fourier

Pada Gambar 7.(b) sinyal keluaran memiliki puncak yang mengakibatkan operasi ada pada mode linear.

Tegangan

Frekuensi Tegangan dB

Cecilia Susilawati. Perancangan Mixer Up-Conversion CMOS Untuk Rangkaian RF Terintegrasi

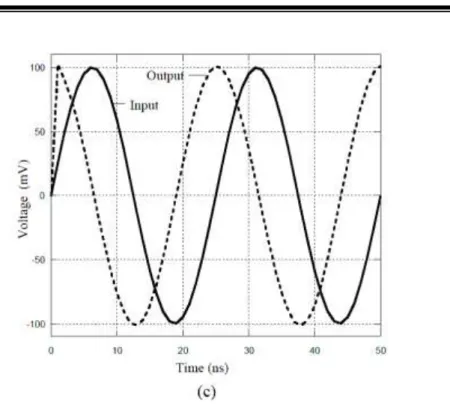

Gambar 8.(a). Respon masukkan dan keluaran dari rangkaian penggeser phasa RC-CR, (b). Respon Penggeser Phasa pada 40 MHz, (c). Respon

Penggeser Phasa pada 1 GHz.

Gambar 8. merupakan respon masukan dan keluaran dari rangkaian penggeser phasa RC-CR, dimana penambahan rangkaian penggeser phasa RC-CR, mengakibatkan akurasi phasa yang lebih baik tetapi memiliki kesalahan amplitudo.

Penguatan cascade pada rangkaian penggeser phasa agar memiliki akurasi amplitudo yang baik. Kesalahan phasa pada rangkaian mendekati 0,1% yang dapat ditiadakan. Penggeser phasa RC – CR memiliki 90% kesalahan amplitudo, yang memerlukan beberapa bagian penguatan lagi untuk mengembalikan sinyal ke kondisi awal.

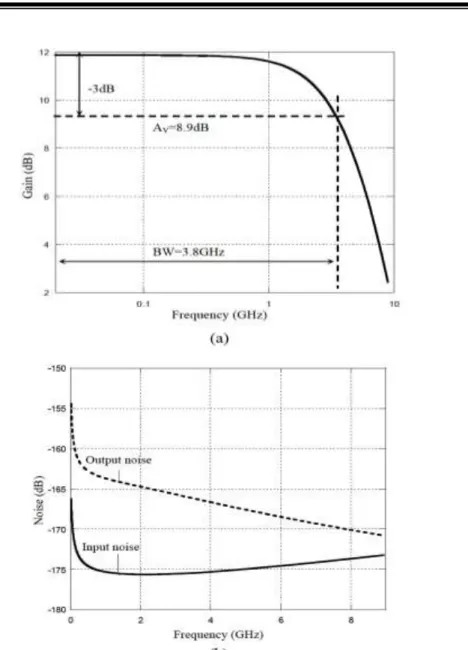

Gambar 9. menunjukkan respon penguatan dan analisa noise masukkan dan keluaran pada penguat cascade. Penguatan -3 dB pada penguat cascade adalah 8,9 dB dengan bandwidth 3,8GHz. Noise keluaran adalah -163 dB dan noise keluaran adalah -175 dB pada 1 GHz dari frekuensi pembawa. Nilai dari disipasi daya adalah 2.648 mW, dengan sumber tegangan 2 Vdc.

Cecilia Susilawati. Perancangan Mixer Up-Conversion CMOS Untuk Rangkaian RF Terintegrasi

Gambar 9.(a). Respon Penguatan dari Penguat cascade, (b). Respon Noise masukkan dan keluaran dari Penguat cascade

Gambar 10. menunjukkan karakteristik keluaran dari up –

conversion mixer pada 40 MHz baseband frekuensi dan 1 GHz pada

frekuensi pembawa. Rangkaian ini direalisasikan dengan sumber tegangan 2 Vdc dan disipasi daya 150 mW. Noise keluaran adalah 7,25x10

-16

Cecilia Susilawati. Perancangan Mixer Up-Conversion CMOS Untuk Rangkaian RF Terintegrasi

Gambar 10.(a). menunjukkan respon transien keluaran pada pengali analog empat kuadran, respon kedua sideband juga ditunjukkan. Gambar 10.(b). menunjukkan respon transien masukkan dan keluaran dari penguat

cascade, yang merupakan bagian sideband atas. Gambar 10.(c).

menunjukkan koefisien transformasi fourier pada keluaran.

Gambar 10.(a). Respon Double Sideband Suppressed Carrier dengan penggeseran phasa 90o dan tidak digeser. (b). Respon transien masukkan dan keluaran pada penguat cascade, (c). Koefisien dari transformasi fourier

Cecilia Susilawati. Perancangan Mixer Up-Conversion CMOS Untuk Rangkaian RF Terintegrasi

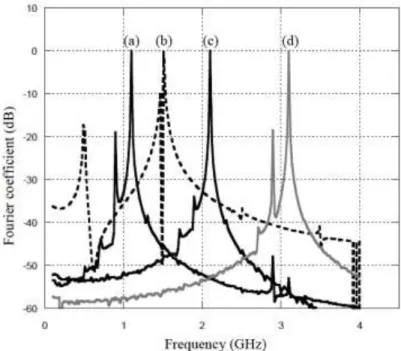

Karakteristik perancangan mixer seperti Gambar 11. menunjukkan koefisien transformasi Fourier dari mixer pada baseband dan frekuensi pembawa yang berbeda – beda.

Gambar 11. dapat ketahui respon frekuensi baseband 100 MHz dan frekuensi pembawa 1 GHz, frekuensi baseband 500 MHz dan frekuensi pembawa 1 GHz, frekuensi baseband 100 MHz dan frekuensi pembawa 2 GHz, frekuensi baseband 100 MHz dan frekuensi pembawa 3 GHz.

Gambar 11. Respon Transformasi Fourier dengan (a). Baseband 100MHz, pembawa 1GHz, (b). Baseband 500MHz, pembawa 1GHz, (c). Baseband

100MHz, pembawa 2GHz, c. Baseband 100MHz, pembawa 3GHz Ukuran performa dari mixer diukur dari loss pada saat konversi dan nilai IIP3. Kehilangan pada saat konversi menunjukkan efisiensi dari mixer

dan nilai IIP3 menunjukkan kelinearan dari mixer.

Gambar 12. menunjukkan plot dari loss pada saat konversi terhadap perubahan baseband dan level sinyal pembawa pada mixer yang beroperasi pada daerah linear.

Cecilia Susilawati. Perancangan Mixer Up-Conversion CMOS Untuk Rangkaian RF Terintegrasi

Gambar 12. Plot loss pada saat konversi terhadap perubahan baseband dan level sinyal pembawa

Gambar 13 menunjukkan plot loss saat konversi terhadap perubahan level sinyal baseband.

Gambar 13. Plot loss saat konversi terhadap perubahan level sinyal

Cecilia Susilawati. Perancangan Mixer Up-Conversion CMOS Untuk Rangkaian RF Terintegrasi

Table 1. menunjukkan parameter performa dari mixer yang dirancang.

Parameter Hasil Sumber Tegangan 2,0Vdc Disipasi daya 150mW Frekuensi Baseband 40MHz Frekuensi Pembawa 1GHz Daya Pembawa -50dBm

Suppresi Sideband bawah -24,2dB

Feedthrough pembawa -33,2dB

Output OIP3 0dBm

Faktor E 5,0

1dB Konversi Level 4,6dB

4. Kesimpulan

Up conversion mixer dengan range frekuensi yang dapat diubah – ubah

dirancang dengan menggunakan metode pergeseran phasa. Penggeser phasa dengan kesalahan phasa yang dapat ditiadakan dengan penguat cascade frekuensi tinggi telah dirancang dan disimulasikan.

Daftar Pustaka

1. Hastings, A. 2001. The Art Of Analog Layout. United States: Prentice Hall.

2. Razavi, B. 1998. RF Microelectronic. London: Prentice Hall.

3. Razavi, B. 2001. Design od Analog CMOS Integrated circuit. New York: McGraw– Hill.