TUGAS AKHIR

Diajukan untuk memenuhi salah satu syarat

Memperoleh gelar Sarjana Teknik

Program Studi Teknik Elektro

i

Disusun oleh:

HADI SANJAYA

NIM : 005114061

PROGRAM STUDI TEKNIK ELEKTRO

JURUSAN TEKNIK ELEKTRO

FAKULTAS SAINS DAN TEKNOLOGI

UNIVERSITAS SANATA DHARMA

YOGYAKARTA

FINAL PROJECT

Presented as Partial Fulfillment of the Requirements

To Obtain the Sarjana Teknik Degree

In Electrical Engineering

ii

By :

HADI SANJAYA

Student ID Number : 005114061

ELECTRICAL ENGINEERING STUDY PROGRAM

ELECTRICAL ENGINEERING DEPARTMENT

SAINS AND TECHNOLOGY FACULTY

SANATA DHARMA UNIVERSITY

YOGYAKARTA

2007

tidak beranak dan tidak diperanakkan. Dan

tidak ada satupun yang menyamai-Nya”.

(Al Ikhlash)

Karya ini kupersembahankan untuk :

Allah SWT dan junjungan Nabi

Muhammad SAW

(

atas berkat dan rahmat-Nya

)

Bapak Iswandi Umar & Ibu

Sumarni yang selalu memberikan

doa, kekuatan dan mendidikku

dengan penuh cinta,

Kakakku Eko Susanto &

Adik-adikku Mira Tulistiana,

Nery Indriana, terima kasih

atas dukungannya,

Almamaterku

vii

frekuensi penggal yang dapat dikendalikan secara digital dengan menggunakan

masukan kode digital. Secara umum alat ini terdiri dari bagian digital dan bagian

analog.

Bagian digital terdiri dari pengendali masukan digital dan pengali, dan bagian

analog terdiri dari filter pelewat rendah. Untuk pengendali masukan digital

menggunakan 8 saklar dan untuk pengali menggunakan DAC 0832. Jadi frekuensi

penggal pada filter ditala secara digital tergantung dari besarnya nilai dari masukan

digital. Untuk filter digunakan filter jenis tapis peubah kondisi dengan tujuan agar saat

frekuensi penggal diubah-ubah, faktor kualitasnya tetap. Proses perkalian antara

masukan digital dengan komponen pengali ‘k’ dan tegangan referensi keluaran dari

penguat beda pada rangkaian tapis peubah kondisi. Hasil perkalian merupakan masukan

untuk rangkaian integrator pada rangkaian tapis peubah kondisi. Nilai masukan digital

ditampilkan oleh LED dan frekuensi penggal diukur dengan menggunakan osiloskop.

Pada

tanggapan

magnitude diperoleh laju kemiringan (roll-off) yang

mempunyai kesalahan rata-rata sebesar 4,1 % dibandingkan dengan nilai teoritis, dan

untuk pengukuraan frekuensi penggal didapatkan kesalahan rata-rata sebesar 2,36 %

dibaningkan nilai teoritis.

viii

Digitally controlled low pass filter is low pass filter that cut-off frequency of

filter could be controlled digitally using binary code digital. This appliance consist of

digital part and analog part.

Part of digital consist of digital input controller and multiplier. Part of analog

consist of low pass filter. Digital input use eight switch and multiplier component use

DAC 0832. The cut-off frequency was tuned digitally depend of digital input value. The

filter use State Variable Filter (SVF) type which so that quality factor (Q) of filter kept

constant. Multiplying operation between digital input voltage with multiplier

component called as ‘k’, and reference voltage from differensiator on state variable

filter. The output of multiplier use as input to integrator on state variable filter. The

value of digital input was displayed by LED and the cut-off frequency was measure by

osciloscope.

From the magnitude response can be analyzed the roll-off value and it has an

error about 4,1 % and for measurement of cut-off frequency has an error about 2,36 %

from theory value.

ix

karena petunjuk dan rahmat-Nya sehingga penulis dapat meyelesaikan Tugas Akhir

yang berjudul “Filter Pelewat Rendah Terkendali Digital”. Tugas Akhir ini disusun

sebagai salah satu syarat untuk memperoleh gelar Sarjana pada jurusan Teknik Elektro,

Fakultas Teknik Universitas Sanatha Dharma Yogyakarta.

Tersusunnya tugas akhir ini tidak terlepas dari bantuan dan dukungan dari berbagai

pihak. Pada kesempatan ini tidak lupa penulis mengucapkan terima kasih yang dalam

kepada :

1. Bapak Martanto, S.T., M.T., selaku Dosen Pembimbing I yang telah banyak

memberikan bimbingan dan pengarahan hingga tugas akhir ini dapat tersusun.

2. Bapak Ir. Tjendro, selaku dosen pembimbing II atas bimbingan dan bantuannya

sehingga penulis dapat menyelesaikan tugas akhir ini.

3. Bapak Djoko Untoro, S.Si., M.T., selaku Dosen Penguji yang telah memberikan

masukan dan saran.

4. Ibu Ir. Th. Prima Ari Setyani, M.T., selaku Dosen Penguji yang telah memberikan

masukan dan saran.

5. Bapak Iswandi Umar dan Ibunda Sumarni yang telah memberikan kasih dan

sayangnya, doa, dorongan, semangat, biaya yang tiada henti hingga terselesaikan

studi dan penyusunan tugas akhir ini.

6. Kakakku Eko Susanto dan Adik-adikku Mira Tulistiana, Nery Indriana atas

dukungan dan semangatnya.

xi

HALAMAN JUDUL ... ..

i

HALAMAN PERSETUJUAN PEMBIMBING... .. iii

HALAMAN PENGESAHAN ... .. iv

HALAMAN PERNYATAAN KEASLIAN KARYA ... .. v

HALAMAN PERSEMBAHAN ... .. vi

INTISARI ... ... .. vii

ABSTRACT... ... .. viii

KATA PENGANTAR ... .. ix

DAFTAR ISI ... ... .. xi

DAFTAR TABEL .... ... .. xiv

DAFTAR GAMBAR ... .. xiv

DAFTAR LAMPIRAN ... .. xvi

BAB

I PENDAHULUAN ... .. 1

1.1 Judul ... .. 1

1.2 Latar Belakang... ..

1

1.3 Rumusan Masalah ... .. 2

1.4 Batasan Masalah... .. 2

1.5 Tujuan dan Manfaat Penelitian... ..

3

1.6 Metodologi Penelitian ... .. 3

xii

2.1.2 Klasifikasi Filter ... .. 6

2.2 Penguat Operasional (Operasional Amplifier, Op-Amp) sebagai

pembangun dasar ... .. 10

2.2.1 Dasar-Dasar Penguat Operasional... .. 10

2.2.2 Penguat Membalik (Inverting Amplifier) ... .. 11

2.2.3 Penguat Tidak Membalik (Non Inverting Amplifier) ... .. 12

2.2.4 Pengikut Tegangan (Voltage Follower) ... .. 13

2.2.5 Penguat Penjumlah (Summing Amplifier) ... .. 14

2.2.6 Integrator ... .. 14

2.3 Filter Pelewat Rendah (Low Pass Filter, LPF) ... .. 16

2.4 Penapis Peubah Kondisi (State Variable Filter, SVF).. ... .. 17

2.5 Digital to Analog Converter (DAC) ... .. 21

2.5.2 DAC 0832... .. 22

2.5.3 Akurasi dan Resolusi... .. 23

2.6 Pengali (Multiplier) ... .. 24

2.7 Saklar Mekanik... .. 26

2.8 Saklar Transistor... .. 27

BAB III

RANCANGAN

PENELITIAN ... ..

30

xiii

3.5 Saklar Sebagai Kendali Masukan Digital... .. 38

BAB

IV HASIL PENGAMATAN DAN PEMBAHASAN ... .. 40

4.1 Tanggapan Magnitude Sebagai Fungsi Frekuensi... .. 40

4.2 Penaksiran Nilai Roll-off pada Tanggapan Magnitude Sebagai

Fungsi Frekuensi ... .. 55

4.3 Hubungan Antara Input Digital dengan Frekuensi cut-off... .. 61

4.4 Hubungan Antara Tegangan Referensi dengan Tegangan

Keluaran Pengali ... .. 65

BAB

V KESIMPULAN DAN PENUTUP ... .. 68

5.1 Kesimpulan ... .. 68

5.2 Saran ……. ... .. 68

DAFTAR PUSTAKA …….. ... .. 70

LAMPIRAN

xiv

Tabel 4.1 Konfigurasi saklar masukan digital saat pengamatan tanggapan

magnitude .. ... .. 41

Tabel 4.2 Tanggapan amplitudo relatif MdB (ω) pengamatan untuk urutan

rendah ... ... .. 42

Tabel 4.3 Tanggapan amplitudo relatif MdB (ω) teoritis untuk urutan rendah... .. 44

Tabel 4.4 Tanggapan amplitudo relatif MdB (ω) pengamatan untuk urutan

sedang ... ... .. 46

Tabel 4.5 Tanggapan amplitudo relatif MdB (ω) teoritis untuk urutan sedang .. .. 48

Tabel 4.6 Tanggapan amplitudo relatif MdB (ω) pengamatan untuk urutan

tinggi... ... .. 51

Tabel 4.7 Tanggapan amplitudo relatif MdB (ω) teoritis untuk urutan tinggi .... .. 53

Tabel 4.8. Penaksiran nilai roll-off pada tanggapan magnitude pengamatan... .. 61

xv

Gambar 2.2 Karakteristik ideal filter pelewat tinggi ...

8

Gambar 2.3 Karakteristik ideal filter pelewat jalur ...

9

Gambar 2.4 Karakteristik ideal filter penolak jalur...

9

Gambar 2.5 Simbol Op-Amp dalam rangkaian ... 10

Gambar 2.6 Comparator non inverting dengan bias positif ... 11

Gambar 2.7 Comparator inverting dengan bias positif ... 11

Gambar 2.8 Rangkaian penguat inverting... 11

Gambar 2.9 Rangkaian penguat non inverting... 12

Gambar 2.10 Rangkaian pengikut tegangan... 13

Gambar 2.11 Rangkaian penguat penjumlah... 14

Gambar 2.12 Rangkaian integrator Op-Amp... 14

Gambar 2.13 Rangkaian integrator yang menggunakan resistor untuk

meminimalkan offset error ... 15

Gambar 2.14 Tanggapan frekuensi Low Pass Filter Butterworth... 17

Gambar 2.15 Blok diagram filter pelewat rendah ... 18

Gambar 2.16 Rangkaian filter pelewat rendah... 20

Gambar 2.17 Rangkaian ternormalisasi filter pelewat rendah ... 21

Gambar 2.18 Simbol DAC 0832 ... 22

Gambar 2.19 Rangkaian R-2R Ladder pada DAC ... 23

xvi

Gambar 2.24 Rangkaian saklar transistor... 27

Gambar 2.25 Karakteristik keluaran transistor... 28

Gambar 2.26 Transistor sebagai saklar tertutup... 29

Gambar 2.27 Transistor sebagai saklar terbuka ... 29

Gambar 3.1 Diagram blok filter pelewat rendah terkendali digital... 30

Gambar 3.2 Rangkaian pengikut tegangan menggunakan IC LF347... 31

Gambar 3.3 Diagram blok yang mempresentasikan persamaan (3.6)... 32

Gambar 3.4 Rangkaian filter pelewat rendah dengan pengali menggunakan

DAC... 34

Gambar 3.5 Rangkaian saklar transistor untuk menyalakan LED ... 35

Gambar 3.6 Gambar rangkaian penampil LED... 38

Gambar 3.7 Rangkaian saklar masukan digital ... 38

Gambar 3.8 Rangkaian 8 saklar masukan digital... 39

Gambar 4.1. Tanggapan magnitude hasil pengamatan dari urutan 1 sampai

urutan 3... 44

Gambar 4.2 Tanggapan magnitude secara teoritis dari urutan ke 1 sampai urutan

ke 3 ... 46

Gambar 4.3 Tanggapan magnitude hasil pengamatan untuk dari urutan ke 100

sampai urutan ke 102... 48

Gambar 4.4 Tanggapan magnitude secara teoritis dari urutan ke 101 sampai

xvii

Gambar 4.6 Tanggapan magnitude secara teoritis dari urutan ke 253 sampai

urutan ke 255 ... 55

Gambar 4.7 Nilai roll-off tanggapan magnitude untuk urutan ke 1 ... 58

Gambar 4.8 Nilai roll-off tanggapan magnitude untuk urutan ke 2 ... 58

Gambar 4.9 Nilai roll-off tanggapan magnitude untuk urutan ke 3 ... 59

Gambar 4.10 Nilai roll-off tanggapan magnitude untuk urutan ke 100 ... 59

Gambar 4.11 Nilai roll-off tanggapan magnitude untuk urutan ke 101 ... 60

Gambar 4.12 Nilai roll-off tanggapan magnitude untuk urutan ke 102 ... 60

Gambar 4.13 Nilai roll-off tanggapan magnitude untuk urutan ke 253 ... 61

Gambar 4.14 Nilai roll-off tanggapan magnitude untuk urutan ke 254 ... 61

Gambar 4.15 Nilai roll-off tanggapan magnitude untuk urutan ke 255 ... 62

Gambar 4.16 Grafik hubungan antara masukan digital dengan frekuensi cut-off

berdasarkan pengamatan dan teori ... 64

Gambar 4.17 Grafik hubungan antara masukan digital dengan galat untuk

frekuensi

cut-off... 65

Gambar 4.18 Grafik hubungan antara masukan digital dengan tegangan referensi

dan keluaran pengali... 67

Gambar 4.19 Grafik hubungan antara masukan digital dengan galat untuk tegangan

keluaran pengali... 68

xviii

Tabel hubungan input digital dengan frekuensi cut-off... A

Tabel hubungan input digital dengan tegangan referensi dan tegangan output

pengali... ...

B

Gambar rangkaian keseluruhan ... C

Gambar rangkaian catu daya ... D

BAB I

PENDAHULUAN

1.1. Latar Belakang Masalah

Kemajuan ilmu pengetahuan dan teknologi pada saat ini telah mempengaruhi segala bidang kehidupan manusia, termasuk dalam bidang elektronika. Salah satu pengaruh yang ditimbulkan adalah adanya pengembangan suatu sistem pengendalian, yaitu yang semula dilakukan secara analog kini telah mulai dialihkan secara digital. Pengembangan tersebut dimaksudkan agar pekerjaan yang dilakukan menjadi lebih praktis. Dalam hal ini, pengembangan dilakukan atas suatu sistem yang lama atau hanya mengubah beberapa bagian kecil saja.

Sistem pengendalian secara digital sebenarnya tidak jauh berbeda dengan sistem pengendalian secara analog. Namun jika dilihat dari segi kepraktisan, sistem pengendalian secara digital lebih praktis sebab hanya memasukkan bit-bit data secara langsung atau tidak langsung melalui saklar yang sudah tersedia.

Dalam sistem komunikasi, filter mempunyai kegunaan yang sangat besar sebab bertugas untuk melewatkan sinyal dengan frekuensi yang dikehendaki dan melemahkan sinyal dengan frekuensi yang tidak diinginkan. Berdasarkan hal tersebut, telah banyak peralatan elektronik pendukung sistem komunikasi yang digunakan oleh manusia, seperti telefon, radio, maupun televisi, menggunakan filter sebagai salah satu komponen. Pada penelitian ini akan dibahas mengenai salah satu jenis filter, yaitu Filter Pelewat Rendah (Low Pass Filter, LPF) yang

dikendalikan secara digital sehingga diperoleh frekuensi cut-off yang dapat diubah-ubah. Pengendalian dilakukan dengan cara menambahkan pengali (multiplier) di dalam filter yang bekerja berdasarkan kondisi masukan digital dari 8 saklar.

1.2. Rumusan Masalah

Rumusan masalah yang dihadapi adalah bagaimana merancang Filter Pelewat Rendah menggunakan modul integrator, agar dapat diketahui posisi pengali sebagai pengendali frekuensi cut-off. Bagaimana mengubah-ubah frekuensi cut-off dari konfigurasi yang telah diperoleh sehingga perubahan frekuensi tiap bit mempunyai step yang tetap dari batas minimum sampai batas maksimum.

1.3.

Batasan Masalah

Pada penelitian ini, dilakukan batasan-batasan terhadap sistem yang akan diteliti. Batasan yang dilakukan antara lain :

1. Dalam realisasi digunakan Penapis Peubah Kondisi (State Variable

Filter, SVF) yang berbasis pada Butterworth orde 2 serta frekuensi

yang diubah-ubah hanya frekuensi cut-off dari Low Pass Filter. 2. Step kenaikan frekuensi ditentukan sebesar 100 Hz, dimulai dari

frekuensi 100 Hz.

3. Berbasis Butterworth orde 2 (faktor kualitas (Q) sebesar 0,707).

5. Pengendalian frekuensi cut-off menggunakan Digital to Analog

Converter 8 bit.

6. Untuk penunjang yang lain digunakan saklar sebagai masukan

digital dan buffer analog.

7. Pengujian sistem dibatasi pada tanggapan frekuensi yang sekaligus

menyatakan tanggapan magnitude, sedangkan tanggapan fase tidak diperhatikan.

1.4.

Tujuan dan Manfaat Penelitian

Tujuan yang ingin dicapai adalah dapat merancang dan membuat Filter Pelewat Rendah menggunakan rangkaian State Variable Filter yang dikendalikan secara digital.

Beberapa manfaat yang diharapkan dapat diperoleh dari penelitian ini adalah sebagai berikut :

1. Tersedianya Filter Pelewat Rendah untuk menghasilkan frekuensi

cut-off yang dapat diubah-ubah.

2. Sistem pengendalian yang dilakukan secara praktis.

3. Sebagai dasar pengembangan untuk aplikasi yang lebih bervariasi.

4. Sebagai referensi yang dapat mendukung penelitian selanjutnya yang berkaitan dengan Filter Pelewat Rendah.

1.5.

Metodologi Penelitian

Dalam penyusunan Tugas Akhir ini dilakukan beberapa metodologi penelitian. Adapun metodologi penelitian yang dilakukan terdiri dari :

1. Studi Pustaka, yaitu dengan mengumpulkan dan mempelajari

berbagai informasi, baik dari buku, makalah maupun internet mengenai hal-hal yang berkaitan dengan Filter Pelewat Rendah, sehingga informasi yang diperoleh dapat digunakan sebagai referensi pendukung dalam penyusunan laporan.

2. Merealisasikan pengetahuan yang diperoleh dalam bentuk

perancangan hardware.

3. Melakukan pengujian terhadap hasil perancangan agar dapat

diketahui hasil secara realistis.

4. Menganalisis hasil pengujian dan membandingkan dengan teori

yang ada.

5. Mengambil kesimpulan terhadap perancangan dan pengujian yang

telah dilakukan. 6.

1.6.

Sistematika Penulisan

Sistematika penulisan Tugas Akhir ini terbagi menjadi 5 bab yang disusun sebagai berikut :

Bab ini berisi tentang latar belakang masalah, rumusan masalah, batasan masalah, tujuan dan manfaat penelitian, metodologi penelitian serta sistematika penulisan.

BAB II. DASAR TEORI

Bab ini berisi penjelasan-penjelasan umum serta persamaan

matematis yang berkaitan dengan filter pelewat rendah terkendali digital.

BAB III. RANCANGAN PENELITIAN

Bab ini berisi tentang rancangan filter pelewat rendah terkendali

sigital, yang meliputi diagram blok, penjelasan cara kerja secara singkat dan pemilihan komponen.

BAB IV. HASIL PENGAMATAN DAN PEMBAHASAN

Bab ini hasil dari penelitian dan pembahasan dari pengujian yang

telah dilakukan. BAB V. PENUTUP

BAB II

DASAR TEORI

2.1.

Filter

2.1.1. Definisi Filter

Filter didefinisikan sebagai sebuah alat atau rangkaian atau substansi

yang meneruskan atau meloloskan arus listrik pada frekuensi-frekuensi atau jangkauan frekuensi tertentu serta menahan (menghalangi) frekuensi-frekuensi lainnya.

2.1.2.

Klasifikasi Filter

Berdasarkan komponen pendukung, filter dapat diklasifikasikan

menjadi 2 macam, yaitu : filter pasif dan filter aktif. 1. Filter Pasif

Filter pasif merupakan rangkaian filter yang hanya terdiri dari inti filter, yaitu kombinasi resistor (R), kapasitor (C), dan induktor (L). Kelebihan yang dimiliki yaitu : mampu memenuhi karakteristik filter yang bagus dengan penerapan yang luas dari frekuensi audio sampai frekuensi yang sangat tinggi, serta handal pada penerapan frekuensi yang sangat tinggi. Sedangkan kekurangannya, yaitu : adanya masalah pada sisi frekuensi rendah pada rentang frekuensi audio, ukuran fisik induktor yang semakin besar untuk induktansi yang besar dan biaya untuk pengadaan induktor yang relatif cukup besar.

2. Filter aktif

Filter aktif merupakan suatu rangkaian filter yang terdiri dari kombinasi resistor, kapasitor dan satu atau lebih komponen aktif, biasanya penguat operasional dengan feedback. Kelebihan yang dimiliki yaitu : penguat operasional mampu menyediakan penguatan atau gain. Sinyal masukan tidak akan mengalami pelemahan (atenuasi) selama sinyal-sinyal dengan frekuensi-frekuensi yang dikehendaki dilewatkan oleh filter. Biaya pembuatan filter murah sebab tidak menggunakan komponen induktor yang harganya relatif mahal dan tidak selalu tersedia di pasaran, mudah diatur (tune) untuk jangkauan frekuensi yang lebar tanpa mempengaruhi tanggapan rangkaian yang telah ditentukan (sesuai dengan yang diinginkan), serta memiliki impedansi masukan yang tinggi dan keluaran yang rendah akibat dari penggunaan penguat operasional yang juga hampir menjamin tidak adanya interaksi antara filter dengan sumber atau beban sinyal. Sedangkan kekuranganya, yaitu : membutuhkan catu daya sendiri, kurang handal dibandingkan komponen pasif, perlu feedback sehingga ada kemungkinan tidak stabil dan batasan frekuensi kerja 100 KHz (bekerja baik dibawah frekuensi 100 KHz).

Berdasarkan jangkauan frekuensi yang dilewatkan (passband) dan jangkauan frekuensi yang ditolak (stop band), filter dapat diklasifikasikan menjadi 4 macam, yaitu : Filter Pelewat Rendah (Low Pass Filter, LPF), Filter Pelewat Tinggi (High Pass Filter, HPF), Filter Pelewat Jalur(Band Pass Filter, BPF) dan Filter Penolak Jalur (Band Rejected Filter, BRF).

1. Filter Pelewat Rendah

Filter pelewat rendah memilih frekuensi-frekuensi rendah dan menolak frekuensi-frekuensi tinggi. Karakteristik ideal filter pelewat rendah ditunjukkan oleh gambar 2.1.

Gambar 2.1. Karakteristik ideal filter pelewat rendah

2. Filter Pelewat Tinggi

Filter pelewat tinggi menolak frekuensi-frekuensi rendah dan

melewatkan frekuensi tinggi. Karakteristik ideal filter pelewat tinggi ditunjukkan oleh gambar 2.2.

Gambar 2.2. Karakteristik ideal filter pelewat tinggi

3. Filter Pelewat Jalur

Filter pelewat jalur melewatkan frekuensi-frekuensi dalam pita tertentu, sedangkan frekuensi-frekuensi diatas pita semuanya ditolak. Karakteristik ideal filter pelewat jalur ditunjukkan oleh gambar 2.3.

Gambar 2.3. Karakteristik ideal filter pelewat jalur

4. Filter Penolak Jalur

Filter penolak jalur menolak frekuensi-frekuensi dalam pita tertentu dan melewatkan frekuensi-frekuensi diatas dan dibawah pita frekuensi tersebut. Karakteristik ideal filter penolak jalur ditunjukkan oleh gambar 2.4.

Gambar 2.4. Karakteristik ideal filter penolak jalur

Terdapat 2 area pada filter dengan karakteristik ideal diatas, yaitu : 1. Pass Band, ditunjukkan dengan nilai 1.

2. Stop Band, ditunjukkan dengan nilai 0.

Filter aktual tidak mempunyai karakteristik ideal seperti gambar diatas, sehingga mempunyai 3 area, yaitu :

1. Pass Band, rentang tertentu dengan penguatan.

2. Stop Band, rentang tertentu di bawah level yang ditentukan.

2.2. Penguat Operasional (Operasional Amplifier, Op-Amp)

sebagai pembangun dasar

2.2.1. Dasar-Dasar Penguat Operasional

Istilah penguat operasional atau Op-Amp awalnya dikenal dalam bidang elektronika analog dan biasanya digunakan untuk operasi-operasi aritmetika seperti penjumlahan, integrasi dll. Op-Amp sebenarnya merupakan sebuah penguat tegangan DC differensial. Adapun simbol Op-Amp ditunjukkan oleh gambar 2.5.

Gambar 2.5 Simbol Op-Amp dalam rangkaian

Karakteristik ideal yang dimiliki , yaitu : lebar pita yang tak berhingga (infinite

bandwidth), impedansi masukkan yang tak berhingga (infinite input impedance),

serta impedansi keluaran yang sama dengan nol (zero output impedance). Dari gambar 2.5 terlihat bahwa Op-Amp memiliki dua masukkan, yaitu masukan positif (V+) dan masukan negative (V-). Biasanya Op-Amp diberi catu daya

dengan polaritas ganda atau bipolar dalam jangkauan ± 5 Volt hingga ±15 Volt. Seperti telah disebutkan sebelumnya Op-Amp memiliki dua masukan. Agar status keluarannya mengindikasikan mana diantara kedua tegangan masukan yang lebih besar, maka suatu Op-Amp dapat digunakkan sebagai komparator. Dengan menerapkan bias DC pada masukan Op-Amp, level transisi dapat diset pada level tegangan yang diinginkan. Hal ini tergantung pula pada polaritas bias

dan pada terminal Op-Amp mana yang diberi bias. Comparator non inverting dengan bias positif ditunjukkan oleh gambar 2.6.

Gambar 2.6. Comparator non inverting dengan bias positif

Comparator inverting dengan bias positif ditunjukkan oleh gambar 2.7.

Gambar 2.7 Comparator inverting dengan bias positif

Selanjutnya pada pembahasan-pembahasan berikutnya rangkaian Op-Amp yang digunakan dalam filter aktif selalu berbentuk atau menggunakan umpan balik eksternal yang berguna untuk menstabilkan karakteristik Op-Amp itu sendiri.

2.2.2. Penguat Membalik (Inverting Amplifier)

Rangkaian penguat inverting ditunjukkan pada gambar 2.8.

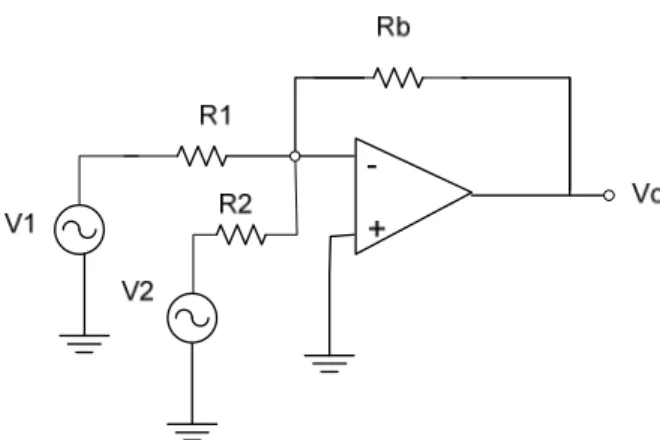

Gambar 2.8 Rangkaian penguat inverting

Penguatan tegangan atau perbandingan tegangan keluaran terhadap tegangan masukan dapat dituliskan sebagai :

b a i R R V V − = 0 (2.1)

Dengan demikian, penguatan tegangan bisa kurang dari 1, sama dengan 1 (unity) atau lebih dari 1. Biasanya Ra = 1 KΩ, karena impedansi masukan

penguat inverting tersebut sama dengan Ra.

2.2.3. Penguat Tidak Membalik (Non Inverting Amplifier)

Rangkaian penguat non inverting ditunjukkan oleh gambar 2.9.Gambar 2.9 Rangkaian penguat non inverting

Persamaan untuk menentukan penguatan tegangan adalah :

b a i R R V V + =1 0 (2.2)

Berbeda dengan penguat inverting, pada penguat non inverting penguatan tegangan selalu lebih besar dari 1. Perbedaan ini terlihat dari persamaan (2.1) dan (2.2).

-+ Vo Ra Vi Rb2.2.4. Pengikut Tegangan (Voltage Follower)

Pengikut tegangan kadang-kadang disebut penyangga atau buffer dan memiliki fungsi yang sama dengan pengikut emitter (emitter follower). Ciri-ciri yang dimiliki, yaitu : impedansi masukan sangat tinggi (lebih dari 100 KΩ) dan impedansi keluaran yang sangat rendah (kurang dai 75Ω).

Gambar 2.10 menunjukkan rangkaian pengikut tegangan.

Gambar 2.10 Rangkaian pengikut tegangan

Jika dibandingkan dengan rangkaian penguat non inverting, pada rangkaian pengikut tegangan, Ra = ∞ dan Rb = 0. Dengan demikian penguatan tegangan

selalu 1. 0 =1 i V V (2.3)

Sehingga dapat diketahui bahwa sinyal keluaran sama persis (identik) dengan sinyal masukan. Fungsi utama dari dari rangkaian ini adalah sebagai penyangga atau mengisolasi beban dari sumber.

2.2.5. Penguat Penjumlah (Summing Amplifier)

Rangkaian penguat penjumlah dapat menjumlahkan dua atau lebih masukan-masukan bebas. Gambar 2.11 menunjukkan rangkaian untuk penguat penjumlah.

Gambar 2.11 Rangkaian penguat penjumlah

Penguatan tegangan untuk masing-masing masukan, yaitu :

1 1 1 R R V V A o b v = =− (2.6) 2 2 2 R R V V A o b v = =− (2.7)

Tegangan keluaran yang diperoleh :

+ − = 2 2 1 1 V R R V R R V b b o (2.8)

2.2.6. Integrator

Integrator Op-Amp dibentuk dengan cara mengganti resistor umpan balik dari rangkaian penguat inverting dengan sebuah kapasitor. Gambar 2.12 menunjukkan suatu rangkaian integrator Op-Amp.

Berdasarkan gambar diatas, sinyal masukan diintegralkan dan sekaligus menyatakan “luasan dibawah kurva”. Tegangan keluaran yang dihasilkan, yaitu : =−

∫

V dt C R V s a o 1 (2.9) Bentuk C Ra 1harus sesuai dengan masukan frekuensi minimum yang

diharapkan : min 2 1 f C Ra π = (2.10)

Karena integrator juga bereaksi terhadap sembarang tegangan offset resultant keluaran (berkaitan dengan offset arus bias Op-Amp), sebuah resistor (Ra )

sering diletakkan diantara masukan positif dengan ground untuk meminimalkan

offset ini. Gambar 2.13 menunjukkan rangkaian integrator yang menggunakan

resistor untuk meminimalkan offset error.

Gambar 2.13 Rangkaian integrator yang menggunakan resistor untuk meminimalkan offset

error

Efek offset dapat melibatkan tegangan maupun arus, dan dapat terjadi secara internal maupun eksternal terhadap Op-Amp itu sendiri. Suatu arus atau

tegangan offset dapat menyebabkan tegangan keluaran tidak nol untuk tegangan masukan yang nol. Biasanya, Op-Amp itu sendiri memiliki offset yang telah disesuaikan hingga beberapa milivolt mengacu pada masukan. Offset terjadi pada saat arus bias masukan mengakibatkan penurunan tegangan yang melalui hambatan masukan. Jika penurunan tegangan terjadi pada masukan (+) dan (-) dapat dibuat sama atau identik, maka offset tersebut dapat dihilangkan.

2.3. Filter Pelewat Rendah (Low Pass Filter, LPF)

Seperti telah dijelaskan sebelumnya, LPF melewatkan frekuensi-frekuensi rendah dan menolak frekuensi-frekuensi-frekuensi-frekuensi tinggi. Adapun fungsi alih dari (transfer function) untuk LPF orde 2 Butterworth standar ditunjukkan oleh persamaan berikut : 2 0 0 2 2 0 0 ω ωω + + = s Q s A Hlp (2.11) dengan : ωo = frekuensi cut-off LPF Ao = penguatan tegangan Q = faktor kualitas

Faktor kualitas pada LPF Butterworth orde 2 adalah 0,707. Sedangkan fungsi alih dalam keadaan tunak (steady state), H(jω) untuk LPF orde 2 dapat dinyatakan sebagai : n fc f M 2 ) / ( 1 1 ) ( + = ω (2.12)

Sedangkan dalam bentuk decibel : n db fc f M 2 10 ) / ( 1 1 log 20 + = (2.13) atau

[

n]

db f fc M 2 10 1 ( / ) log 10 + − = (2.14)Tanggapan frekuensi Low Pass Filter Butterworth ditunjukkan oleh gambar 2.14.

Gambar 2.14. Tanggapan frekuensi Low Pass Filter Butterworth

2.4. Penapis Peubah Kondisi (State Variable Filter, SVF)

State Variable Filter digunakan untuk implementasi Low Pass Filter

(LPF), High Pass Filter (HPF), Band Pass Filter (BPF), dan Band Rejected Filter (BRF) dalam satu struktur yang sama. Istilah State Variable Filter berhubungan dengan analisis yang disebut teori State Variable yang memberikan penyelesaian

sistematis suatu persamaan differensial dari sistem yang besar. Secara teoritis, dapat dirancang SVF orde berapapun, tapi kebanyakan perancangan berbasis pada orde 2. Perancangan dengan orde 2 lebih tahan terhadap variasi parameter dibandingkan dengan perancangan menggunakan orde lebih tinggi. Orde yang lebih tinggi dibuat dengan mengkaskade orde-orde berbasis 2, sedangkan untuk perancangan dengan orde ganjil diperlukan filter dengan orde ganjil.

Untuk mengimplementasikan filter pelewat jalur dalam bentuk SVF, digunakan persaman fungsi alih filter pelewat rendah orde 2 standar, yaitu seperti diperlihatkan pada persamaan (2.11). Persamaan tersebut dapat diubah menjadi sebagai berikut : 2 0 0 2 2 0 0 ω ωω + + = s Q s A V V i lp (2.15)

Dari persamaan (2.19), dilakukan sintesis sehingga menjadi rangkaian yang dibentuk dari rangkaian modul integrator. Ada 3 tahapan matematis dasar yang diperlukan untuk mengimplementasikan persamaan fungsi alih ini, yaitu :

• Perkalian silang (cross multiplying), yaitu perkalian antara sinyal keluaran dengan penyebut dan antara sinyal masukan sengan pembilang dari fungsi alih filter pelewat rendah.

• Melakukan pembagian hasil tahap pertama dengan variabel s yang memiliki

pangkat terbesar.

• Menyusun kembali persamaan hasil tahap kedua untuk mendapatkan

pernyataan sinyal keluaran.

(

2)

2 2 o o i o o lp s V A Q s V ω ω = ω + + (2.16) = + + 022 2 2 0 0 1 s A V s sQ Vlp ω ω i oω (2.17) 2 0 0 2 0 1 − − = s V s Q V s A V Vlp i o ω lp ω lp ω (2.18) − − + − − = s V V Q s A V s Vlp ω0 i o ω0 1 lp lp ω0 (2.19)[

]

+ − − − = i o lp lp lp V Q V A V s s V ω0 ω0 1 (2.20)Persamaan (2.24) menyatakan persamaan untuk sebuah jaringan dengan

menggunakan modul integrator, komponen (ωo/s) menunjukkan suatu modul

integrator dalam filter. Untuk memperoleh realisasi yang paling sederhana, persamaan (2.24) dapat disusun menjadi :

[

]

− − − − − = lp i o lp lp V Q A V V s s V ω0 ω0 1 (2.21)Diagram blok yang mempresentasikan persamaan (2.21) ditunjukkan pada gambar 2.15. s o ω − s o ω − Q 1

Σ

Σ

oA

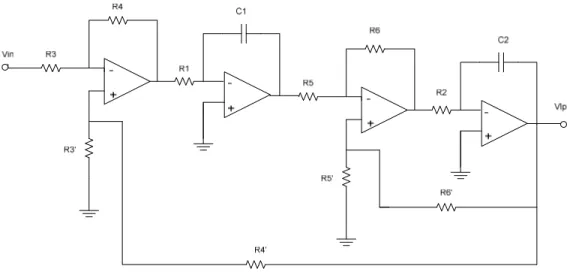

Jika gambar 2.16 dihubungkan ke modul integrator dan penguat beda, maka rangkaian filter pelewat rendah ditunjukkan oleh gambar 2.16.

Gambar 2.16 Rangkaian filter pelewat rendah

Karena ini adalah LPF Butterworth orde 2, maka faktor kualitas untuk LPF ini adalah sebesar 0,707 yang didapat dari 1/α, dimana α adalah faktor redaman untuk Low Pass Filter Butterworth sebesar 1,414.

Jika dilihat dari rangkaian filter pelewat rendah pada gambar 2.17, maka dapat diperoleh faktor penguatan filter pelewat rendah dari feedback Vlp menuju

masukan non inverting penguat beda, sebagai berikut :

+ + = ' ' ' 1 4 3 4 3 4 R R R R R Ao (2.22)

Agar diperoleh penguatan sebesar 1 maka nilai R3=R4=R3’=R4’ dan untuk

memperoleh faktor kualitas sebesar Q = 0,707 maka nilai R6’ dibuat sebesar 1/Q

R2 danC1, C2 yang identik. Nilai R1 dan R2 dibuat bernilai sama. Nilai C1 danC2

diperoleh berdasarkan persamaan :

RC fo π 2 1 = (2.23)

Berdasarkan hal diatas, maka rangkaian ternormalisasi, filter pelewat rendah ditunjukkan oleh gambar 2.17.

Gambar 2.17. Rangkaian ternormalisasi filter pelewat rendah

2.5 Digital to Analog Converter (DAC)

Konversi digital to analog merupakan proses pengubahan kode digital menjadi keluaran analog yang berupa arus atau tegangan. Sedangkan rangkaian yang digunakan untuk mengkonversi disebut Digital to Analog Converter.

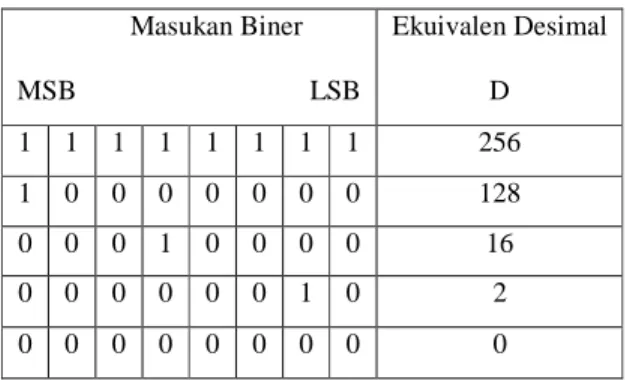

2.5.1. Kode Digital

Suatu kode digital dapat dikembangkan sebagai D yang terdiri dari n

merupakan Least Significant Bit (LSB). Jika diubah ke dalam bentuk desimal, nilai aktual dari D dapat diekspresikan sebagai berikut :

D=bn-12n-1 + ... +b222+ b121 + b020

Sebagai contoh, tabel 2.1 memperlihatkan masukan biner 8 bit serta ekuivalen dalam bentuk desimal.

Tabel 2.1 Masukan biner dan ekuivalen dalam desimal

Masukan Biner MSB LSB Ekuivalen Desimal D 1 1 1 1 1 1 1 1 256 1 0 0 0 0 0 0 0 128 0 0 0 1 0 0 0 0 16 0 0 0 0 0 0 1 0 2 0 0 0 0 0 0 0 0 0

2.5.2. DAC 0832

DAC 0832 merupakan conveter 8 bit yang dapat mengubah masukan

biner menjadi keluaran yang berupa arus. Simbol DAC 0832 ditunjukkan oleh gambar 2.18.

Gambar 2.18 Simbol DAC 0832

Nilai arus diperoleh berdasarkan R-2R Ladder yang ditunjukkan oleh gambar 2.19

Gambar 2.19 Rangkaian R-2R Ladder pada DAC

Berdasarkan gambar diatas, nilai arus keluaran yang diperoleh, yaitu :

256 ) ( 10 1 ut digitalinp R V I fb ref out = × (2.24) dan 256 ) ( 255 10 2 ut digitalinp R V I fb ref out − × = (2.25)

Masukan digital terdiri dari 8 bit kode biner yang mempunyai rentang 0 sampai 255 jika diekuivalenkan dalam bilangan desimal. Sedangkan Vref adalah

tegangan referensi dan Rfb merupakan hambatan dalam.

2.5.3 Akurasi dan Resolusi

Pengubahan sinyal digital ke sinyal analog memerlukan 2 hal penting yang saling berkaitan, yaitu akurasi/ketelitian dan resolusi. Akurasi adalah seberapa dekat nilai keluaran sebenarnya dari pengubah digital ke analog terhadap nilai keluaran secara teoritis. Semakin kecil presentase ketelitian, maka semakin dekat dengan nilai secara teoritis. Sedangkan resolusi adalah pertambahan terkecil pada tegangan yang diamati. Pertambahan terkecil pada tegangan keluaran terutama ditentukan oleh tegangan masukan bit terkecil

(LSB). Pada DAC 0832, masukan yang dimiliki terdiri dari 8 bit sehingga

mempunyai 28 atau 256 step. Jika keluaran maksimum dibagi dengan banyaknya

step maka setiap kenaikan atau penurunan per bit mengalami perubahan yang tetap.

2.6. Pengali (Multiplier)

Untuk menghasilkan tegangan keluaran yang merupakan fungsi perkalian antara suatu konstanta (kode kendali digital) dengan tegangan masukan, maka sebagai pengali digunakan pengali yang menggunakan DAC. Simbol pengali ditunjukkan oleh gambar 2.20.

Gambar 2.20 Simbol pengali

Jika k menyatakan konstanta, maka persamaan pada keluaran pengali dapat dituliskan sebagai :

Vout =k.Vin (2.26)

DAC yang digunakan pada pengali adalah DAC 0832 sebab berdasarkan

datasheet, DAC jenis ini sangat cocok diaplikasikan untuk mengendalikan

frekuensi cut-off Filter Pelewat Rendah yang terdiri dari modul integrator. Jika

hambatan dalam (Rfb) dari DAC ini tidak dihubungkan atau dalam arti diabaikan,

dari DAC dapat diubah menjadi tegangan, maka Iout1 dan Iout2 dihubungkan ke

sebuah Op-Amp, yaitu Iout1 dihubungkan ke terminal negatif (-) sedangkan Iout2

dihubungkan ke terminal positif (+) dan digroundkan, sedangkan Rfb dihubungkan

ke keluaran Op-Amp. Untuk lebih jelas, gambar 2.21 memperlihatkan DAC dihubungkan ke sebuah Op-Amp sehingga menghasilkan tegangan keluaran.

Gambar 2.21 DAC yang dihubungkan ke sebuah Op-Amp

Vin pada gambar 2.21 merupakan suatu tegangan referensi (Vref) dari DAC dan Rfb

merupakan hambatan dalam, yang mempunyai nilai nominal sebesar 15 KΩ. Tegangan keluaran dari Op-Amp dapat dirumuskan sebagai berikut :

fb out

out I R

V =− . (2.27)

Disamping itu, agar DAC 0832 dapat berfungsi sebagai pengali, maka perlu diperhatikan pin-pin yang berfungsi sebagai control signal, yaitu pin CS diberi logika 0, pin ILE diberi logika 1, pin WR dan 1 WR diberi logika 0,serta 2 pin XFER diberi logika 0. Jika persamaan (2.24) dimasukkan ke persamaan

(2.27), maka diperoleh : in out V ut Digitalinp V 256 ) ( 10 − = (2.28)

Agar tegangan keluaran (Vout) yang dihasilkan mempunyai polaritas positif, maka

Vout dihubungkan ke sebuah penguat inverting. Rangkaian pengali menggunakan

DAC ditunjukkan oleh gambar 2.22.

Gambar 2.22 Rangkaian pengali menggunakan DAC

Berdasarkan datasheet, nilai R yang digunakan 10 KΩ.

Vout yang diperoleh, yaitu :

1 256 ) ( 10 − × − = in out V ut Digitalinp V Sehingga : in out V ut Digitalinp V 256 ) ( 10 = (2.29)

Jika persamaan (2.29) dibandingkan dengan persamaan (2.26), maka :

256 ) (Digitalinput 10

k = (2.30)

2.7. Saklar Mekanik

Saklar merupakan suatu komponen yang berfungsi untuk menghubungkan dan memutuskan arus listrik yang dapat terkunci pada posisi terakhir. Pada bagian

ini dibahas mengenai saklar mekanik yang digunakan sebagai masukan ke rangkaian. Rangkaian saklar mekanik ditunjukkan oleh gambar 2.23.

R R SW SPST 1 2 VCC SW SPST 1 2 VCC

Gambar 2.23 Rangkaian saklar mekanik

Berdasarkan gambar 2.23 logika rendah dihasilkan jika saklar ditekan, sedangkan jika saklar tidak ditekan maka akan menghasilkan logika tinggi.

2.8. Saklar Transistor

Rangkaian saklar transistor ditunjukkan oleh gambar 2.24.

3 2 1 RC VBB VCC RB IC

Gambar 2.24 Rangkaian saklar transistor

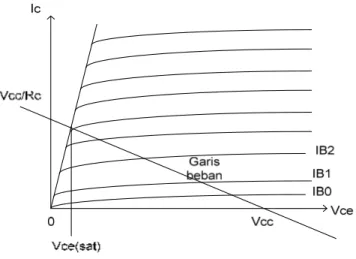

Gambar 2.25 Karakteristik keluaran transistor

Transistor berada dalam kadaan saturasi/jenuh saat IB = IB0. Pada keadaan

ini, beda potensial antara kolektor dan emitter (Vce) adalah sangat kecil, yaitu

sama dengan Vce(sat), sedangkan arus kolektor IC yang mengalir hampir sama

dengan Vcc dan IC tidak mengalami perubahan. Nilai Vcc = Vce(sat) dan nilai IC =

Vcc/Rc. Hal inilah yang disebut dengan keadaan saturasi sebab nilai IC dan Vce

tidak berubah walaupun arus basis bertambah besar.

Nilai arus basis tergantung dari tegangan VBB dan hambatan Rb yang

dihubungkan seri dengan basis. Arus basis IB diperoleh berdasarkan persamaan :

b be BB B R V V I = − (2.31)

Jika arus basis lebih dari 0 atau semakin besar maka transistor menjadi on sehingga dapat berfungsi sebagai saklar penutup. Transistor sebagai saklar penutup ditunjukkan oleh gambar 2.26.

VCC VCC RC RB VBB 3 2 1 IC IB>0 RC

Gambar 2.26 Transistor sebagai saklar tertutup

Sedangkan jika arus basis sama dengan 0, maka dapat dikatakan transistor bekerja di daerah cut-off sehingga transistor menjadi off dan berfungsi sebagai saklar terbuka. Transistor sebagai saklar terbuka ditunjukkan oleh gambar 2.27.

3 2 1 RC VCC VBB VCC IB=0 RB IC RC

BAB III

RANCANGAN PENELITIAN

3.1 Diagram Blok Filter Pelewat Rendah Terkendali Digital

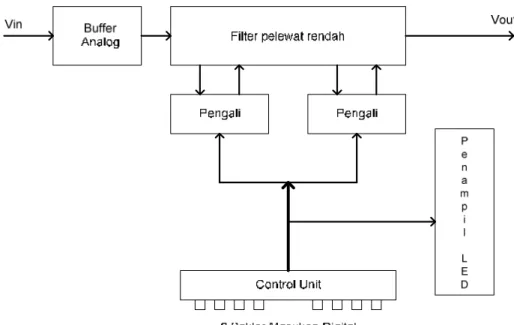

Untuk membentuk suatu filter pelewat rendah terkendali digital, diperlukan beberapa rangkaian pendukung sehingga memungkinkan diperoleh keluaran yang diinginkan sesuai dengan kondisi masukan, baik berasal dari masukan filter maupun dari pengendali. Diagram blok filter pelewat rendah terkendali digital ditunjukkan oleh gambar 3.1 :

Gambar 3.1 Diagram blok filter pelewat rendah terkendali digital

Berdasarkan gambar 3.1, buffer analog digunakan untuk menghasilkan sinyal masukan ke filter maupun ke pengali. Delapan saklar pada control unit berfungsi untuk mengontrol masukan digital ke pengali. Tegangan keluaran dari pengali dihubungkan ke masukan integrator sehingga frekuensi cut-off Filter

Pelewat Rendah dapat diubah-ubah. Pengali berfungsi untuk menghasilkan tegangan keluaran sebagai fungsi perkalian antara suatu konstanta dengan tegangan masukan.

3.2. Buffer Analog

Sebagai buffer analog, digunakan rangkaian pengikut tegangan. Dengan adanya pengikut tegangan, maka tegangan keluaran yang dihasilkan untuk dihubungkan ke masukan filter pelewat rendah, mengikuti/menyamai tegangan sumber/masukan dalam hal besarnya maupun tundanya. Rangkaian pengikut tegangan menggunakan IC LF347 ditunjukkan oleh gambar 3.2.

Gambar 3.2 Rangkaian pengikut tegangan menggunakan IC LF347

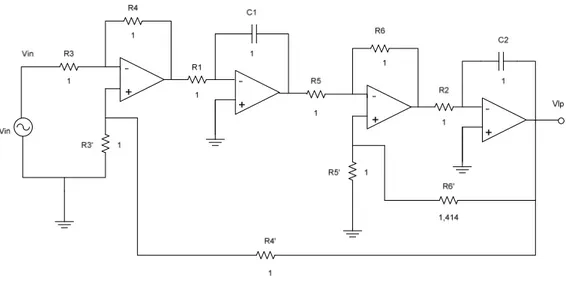

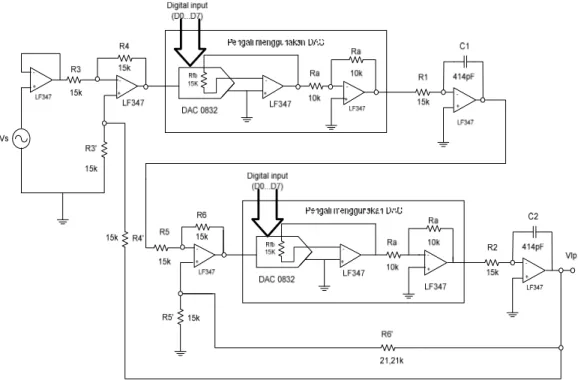

3.3. Filter Pelewat Rendah Terkendali Digital

Filter pelewat rendah dapat dikendalikan secara digital untuk memperoleh frekuensi cut-off yang berubah-ubah. Mengacu pada persamaan (2.19), realisasi dilakukan dengan memodifikasi fungsi alih filter pelewat rendah sehingga frekuensi cut-off yang baru merupakan perkalian antara konsanta k

dengan frekuensi cut-off semula (ωo). Pernyataan ini ditunjukkan oleh persamaan (3.6) :

( )

2 0 0 2 2 0 0( ) ω ω ω k s Q k s k A V V i lp + + = (3.6)Diagram blok untuk mengimplementasikan persamaan diatas adalah :

s o ω − s o ω − Q 1

Σ

Σ

oA

Gambar 3.3 Diagram blok yang mempresentasikan persamaan (3.6)

Berdasarkan gambar 3.3, untuk memperoleh perubahan frekuensi cut-off, rangkaian pengali dihubungkan sebelum integrator pada rangkaian filter. Karena dikendalikan secara digital, maka pada pengali ditambahkan komponen yang dapat mengubah sinyal digital menjadi sinyal analog, yaitu Digital to Analog

Converter (DAC). Frekuensi cut-off filter pelewat rendah dapat ditala secara

digital tergantung pada besar nilai konstanta k yang merupakan kode kendali digital, dengan nilai k tergantung dari bit-bit masukan. Modul integrator mempunyai karakteristik transfer sebesar –k ωo/s. Frekuensi cut-off yang baru

adalah sebesar ωo’= k. ωo. Semakin besar nilai bit yang dimasukkan ke pengali,

Pada perancangan ini, jangkauan frekuensi cut-off yang digunakan mulai dari frekuensi 100 Hz dengan step 100. Untuk memperoleh nilai frekuensi cut-off yang berubah-ubah, besaran-besaran yang perlu ditentukan adalah sebagai berikut: a. Frekuensi cut-off yang baru, fo’ pada setiap masukan digital tertentu. Dalam

hal ini fo’ ditentukan pada nilai minimum saat masukan digital dari DAC yang

juga bernilai minimum.

b. Faktor kualitas, Q = 0,707 (Butterworth orde 2).

c. Penguatan tegangan, A =1.

Komponen yang menentukan konstanta integrasi dari suatu integrator adalah resistor dan kapasitor. Jika R1 = R2 dan C1 = C2, serta mengacu pada point a, yaitu

dengan menguraikan ωo’ min= kmin. ωo min, diperoleh persamaan sebagai berikut :

1 1 10 min 1 256 ) ( ' 2 C R ut Digitalinp fo = π Sehingga : 1 1 10 min 2 1 256 ) ( ' C R ut Digitalinp fo π = (3.8)

Penentuan perolehan nilai komponen untuk mendapatkan frekuensi

cut-off pada jangkauan frekuensi yang sesuai dengan perancangan. Nilai R1 yang

digunakan = 15 KΩ, masukan digital = 1 dan fo’min = 100 Hz. Dengan

menggunakan persamaan (3.8) diperoleh nilai C1 dan C2 sebesar :

100 . 15 . 2 . 256 1 2 1 K C C π = = = = 2 1 C C 0.414 nF = 414 pF

Nilai 414 pF diperoleh dengan mempararel kapasitor standar, yaitu 390 pF, 10 pF

dan 4 pF (390 pF + 10 pF + 4 pF = 414 pF). Karena nilai R1 = R2 =15 KΩ, maka

nilai R3, R4, R3’, R4’,R5, R6, dan R5’ juga menjadi 15 KΩ. Pada komponen

ternormalisasi, penguatan sebesar 1 diperoleh jika R4, R3, R3’ dan R4’ bernilai

sama sehingga pada perhitungan persamaan (2.22) maka akan didapatkan penguatan sebesar 1. Untuk memperoleh faktor kualitas sebesar 0,707, maka nilai R6’ = 28,28 KΩ Nilai yang digunakan R6 adalah 21,21 KΩ yang diperoleh dengan

menghubungkan resistor 10 KΩ, 5,6 KΩ dan 5,6 KΩ secara seri. Agar dapat bekerja dengan baik jika diaplikasikan dengan DAC, Op-Amp yang digunakan LF 347. Untai filter pelewat rendah dengan pengali menggunakan DAC untuk memperoleh frekuensi cut-off pada jangkauan frekuensi tertentu ditunjukkan oleh gambar 3.4.

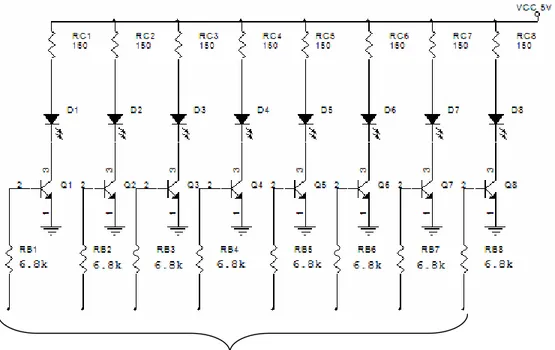

3.4. Penampil LED

Rangkaian penampil sangat penting untuk memvisualisasikan dan untuk mengetahui data-data yang dimasukan ke rangkaian DAC. Agar dapat diketahui masukan digital ke DAC, sebagai penampil digunakan rangkaian penampil LED.

LED akan menyala cukup terang bila dialiri arus sebesar 10 mA sampai 20 mA. Bila dialiri arus yang lebih besar lagi, maka LED akan menyala lebih terang. Arus maksimal yang diperbolehkan adalah antara 25 mA sampai 100 mA, yang tergantung dari tipe dan warna LED. Untuk dapat mengetahui kondisi LED, digunakan saklar transistor. Kondisi transistor (aktif atau tidak aktif) sangat dipengaruhi oleh arus IB dan besarnya arus IB tergantung dari Vcc yang

dihubungkan dari saklar. Gambar 3.5 menunjukkan rangkaian saklar transistor untuk menyalakan LED.

LED VCC VCC DARI SAKLAR RB Q 3 2 1 RC

Gambar 3.5 Rangkaian saklar transistor untuk menyalakan LED

VCC dari saklar adalah sebesar 5 V dan VCC adalah sebesar 5 V. Sedangkan

transistor yang digunakan mempunyai penguatan arus (β) yang besar, yaitu transistor BC109. Agar LED dapat menyala cukup terang dan transistor dalam

keadaan jenuh/saturasi maka berdasarkan data sheet, dipilih nilai IC sebesar 20

mA. Nilai Rc diperoleh berdasarkan persamaan :

Vcc =Ic

(

Rc +Rd)

+Vd +Vce( sat) d C sat ce d cc c R I V V V R = − − ( ) −Vd adalah tegangan potong (cut-in voltage) LED yang mempunyai nilai sekitar 2

V, sedangkan Rd adalah hambatan ekuivalen dc. Karena nilai Rd dan VCE(sat)

sangat kecil, sehingga dapat diabaikan, maka diperoleh :

C d cc c I V V R = − mA V V 20 2 5 − = Rc =150Ω

Nilai Rc standar yang dipilih juga bernilai 150 Ω.

Transistor yang digunakan berfungsi sebagai saklar tertutup saat masukan digital saklar ON dan saklar terbuka saat masukan digital saklar OFF.

Saat masukan digital saklar ON (logika tinggi), maka kolektor terhubung ke

emitter sehingga arus akan mengalir dari Vcc ke ground dan LED menjadi

menyala. Sedangkan saat masukan digital saklar OFF (logika rendah), maka

kolektor menjadi terbuka terhadap emitter sehingga arus dari Vcc tidak dapat

mengalir ke ground dan LED menjadi padam.

Transistor yang digunakan berfungsi sebagai saklar tertutup saat VOH

dan saklar terbuka saat VOL. Saat VOH (logika tinggi), maka kolektor terhubung ke

menyala. Sedangkan saat VOL (logika rendah), maka kolektor menjadi terbuka

terhadap emitter sehingga arus dari Vcc tidak dapat mengalir ke ground dan LED

menjadi padam. Berdasarkan data sheet, β yang dipilih adalah sebesar 350. β

dapat digunakan untuk mendapatkan nilai IB0, yaitu berdasarkan persamaan :

β ) ( 0 sat C B I I = Sehingga : A mA IB 57,14µ 350 20 0 = =

IB0 merupakan besaran arus yang menyebabkan transistor menjadi saturasi. Besar

IB yang digunakan untuk mengaktifkan transistor dipilih sebesar 10.IB0, yaitu

0,5714 mA. Agar diperoleh nilai IB yang diinginkan, maka diperlukan hambatan

Rb, yang didapat dari persamaan :

B be OH b I V V R = −

VOH ditentukan sebesar 4,3 V dan Vbe transistor jenis silikon adalah sebesar 0,7

V, sehingga : Ω = − = K mA V V Rb 7,08 5714 , 0 7 , 0 75 , 4

Nilai Rb standar yang dipilih adalah 6,8 KΩ.

Masukan digital dari saklar kendali

Gambar 3.6 Gambar rangkaian penampil LED

3.5. Saklar Sebagai Kendali Masukan Digital

Sebagai masukan digital berupa binary code 8 bit digunakan delapan

saklar yang dihubungkan dengan Vcc 5 Volt. Saklar yang digunakan adalah switch

SPDT.

Pada rangkaian yang ditunjukkan pada gambar 3.7, pada saat saklar terhubung pada pin 1 pada saklar SPDT, maka akan menghasilkan logika rendah (VOL)

karena Vcc akan terhubung dengan ground dan pada saat saklar terhubung pada pin 3 pada saklar SPDT maka menghasilkan logika tinggi (VOH) pada masukan

digital karena VCC akan langsung memberikan masukan tegangan pada masukan

digital.

Karena VOH ditentukan sebesar 4,75 V dan IB pada rangkaian penampil

LED yaitu sebesar 0,571 mA maka nilai R1 diperoleh melalui perhitungan :

1 R CC B V V V = − V V VR1=5 −4,75 V VR1=0.25 Maka nilai R1 : mA V R 571 , 0 25 , 0 1 = Ω =437.52 1 R

Nilai R1 yang digunakan sebesar 450 Ω.

Rangkaian delapan saklar masukan digital ditunjukkan oleh gambar 3.8.

SW1 2 1 3 R4 450 D6 D1 D7 SW5 2 1 3 R1 450 D0 D3 SW4 2 1 3 SW8 2 1 3 5 V R6 450 R8 450 d i g i t a l i n p u t SW2 2 1 3 R5 450 D2 SW7 2 1 3 D4 ke penampil LED R7 450 R3 450 SW3 2 1 3 SW6 2 1 3 R2 450 D5

BAB IV

HASIL PENGAMATAN DAN PEMBAHASAN

Pada bab ini akan ditunjukkan hasil pengamatan dan pembahasan dari Filter Pelewat Rendah Terkendali Digital. Pengujian dilakukan dengan cara memberikan masukan frekuensi pada masukan blok filter yang berupa gelombang sinus dari AFG (Audio Function Generator) serta masukan pengendali frekuensi berupa bit digital yang berasal dari saklar. Jumlah saklar untuk kendali masukan digital ada 8 saklar, yaitu saklar1 (LSB), saklar2, saklar3, saklar4, saklar5, saklar6,

saklar7 dan saklar8 (MSB). Untuk penampil nilai bit masukan digital, digunakan

LED yang jumlahnya ada 8 LED. Pada saat saklarn tidak terhubung ke ground ,

maka nilai bit masukan digital akan ditampilkan dengan LED ke n yang menyala sebagai bit 1 dan saat saklarn terhubung ke ground, maka nilai bit masukan digital

akan ditampilkan dengan LED ke n yang tidak menyala sebagai bit 0. Tegangan dan frekuensi yang dihasilkan pada keluaran filter digunakan sebagai acuan dalam membuat grafik tanggapan magnitude.

4.1.

Tanggapan Magnitude Sebagai Fungsi Frekuensi

Sub bab ini bertujuan untuk menunjukkan tanggapan magnitude dari keluaran filter pelewat rendah. Jumlah masukan digital ada 255 masukan digital, sehingga jumlah filter pelewat rendah ada 255 dimana frekuensi cut-off nya terkendali oleh masukan digital. Berdasarkan jumlah filter pelewat rendah, maka tanggapan magnitude pada filter pelewat rendah juga ada 255 dimana frekuensi

cut-off nya urut berdasarkan masukan digital dari nilai yang terkecil (urutan ke 1

(fc=100 Hz)) sampai masukan digital yang terbesar (urutan ke 255 (fc 25,5 KHz)). Untuk pengamatan diambil beberapa percobaan, yaitu percobaan pada urutan rendah (urutan ke 1 (fc = 100Hz), urutan ke 2 (fc = 200Hz) dan urutan ke 3 (fc = 300 Hz)), urutan sedang (urutan ke 100 (fc = 10 KHz), urutan ke 101 (fc = 10,1 KHz) dan urutan ke 102 (fc = 10,2 KHz)) dan urutan tinggi (urutan ke 253 (fc = 25,3 KHz), urutan ke 254 (fc = 25,4 KHz) dan urutan ke 255 (fc = 25,5 KHz)) sesuai dengan nilai masukan digital yang dimasukkan ke rangkaian pengali. Pengaturan saklar untuk masukan digital pada percobaan dapat ditunjukkan oleh tabel 4.1.

Tabel 4.1 Konfigurasi saklar masukan digital saat pengamatan tanggapan magnitude

Masukan Digital (MSB) (LSB) Urutan S8 S7 S6 S5 S4 S3 S2 S1 ke 1 0 0 0 0 0 0 0 1 ke 2 0 0 0 0 0 0 1 0 Urutan Rendah ke 3 0 0 0 0 0 0 1 1 ke 100 0 1 1 0 0 1 0 0 ke 101 0 1 1 0 0 1 0 1 Urutan Sedang ke 102 0 1 1 0 0 1 1 0 ke 253 1 1 1 1 1 1 0 1 ke 254 1 1 1 1 1 1 1 0 Urutan Tinggi ke 255 1 1 1 1 1 1 1 1

Untuk memperoleh grafik tanggapan magnitude, penguatan amplitudo hasil pengamatan dihitung dengan menggunakan persamaan (4.1) :

I O dB V V M (ω)=20log10 (4.1)

Sedangkan secara teoritis, penguatan amplitudo dihitung berdasarkan persamaan (2.13). Dari tanggapan magnitude tersebut, dapat ditunjukkan frekuensi cut-off yang berubah dari nilai masukan digital yang rendah ke nilai masukan digital yang lebih tinggi. Jika hasil pengamatan tegangan (Vpp) keluaran dan tegangan

masukan (Vpp) untuk frekuensi tertentu pada percobaan pada urutan rendah

(urutan ke 1 (fc = 100Hz), urutan ke 2 (fc = 200Hz) dan urutan ke 3 (fc = 300 Hz)), urutan sedang (urutan ke 100 (fc = 10 KHz), urutan ke 101 (fc = 10,1 KHz) dan urutan ke 102 (fc = 10,2 KHz)) dan urutan tinggi (urutan ke 253 (fc = 25,3 KHz), urutan ke 254 (fc = 25,4 KHz) dan urutan ke 255 (fc = 25,5 KHz))

dimasukkan ke persamaan (4.1) maka diperoleh tanggapan amplitudo relatif MdB

(ω) yang terdapat pada tabel 4.2, 4.3, 4.4, dan untuk tanggapan amplitudo relatif MdB (ω) secara teoritis nilai frekuensi hasil pengamatan dan nilai frekuensi cut-off

dimasukkan ke persamaan (2.13).

Tanggapan amplitudo relatif MdB (ω) hasil pengamatan untuk urutan

rendah dapat ditunjukkan oleh tabel 4.2.

Tabel 4.2 Tanggapan amplitudo relatif MdB (ω) pengamatan untuk urutan rendah Tanggapan Amplitudo (dB) Frekuensi (Hz) urutan ke 1 (fc =100 Hz) urutan ke 2 (fc =200 Hz) urutan ke 3 (fc =300 Hz) 10 -0,211 -0,211 -0,211 40 -0,069 0 0 60,2 -0,5 0 0

Tanggapan Amplitudo (dB) Frekuensi (Hz) urutan ke 1 (fc =100 Hz) urutan ke 2 (fc =200 Hz) urutan ke 3 (fc =300 Hz) 80,2 -1,432 0,069 0,069 85,1 -1,597 0 0,137 90,7 -2,475 0 0,069 95,2 -2,853 -0,211 0 100,4 -3,248 -0,211 0 105 -3,876 -0,354 0 110,3 -4,321 -0,5 0 120,6 -5,288 -0,649 -0,211 130,5 -6,375 -0,953 -0,211 140,4 -7,618 -1,269 -0,354 150,3 -8,313 -1,597 -0,5 160,2 -9,268 -1,938 -0,649 170,5 -10,116 -2,383 -0,8 180,6 -10,812 -2,662 -0,8 190,5 -11,835 -3,147 -0,953 200,4 -12,995 -3,248 -1,11 210,5 -13,638 -4,096 -1,269 220,4 -13,979 -4,553 -1,432 240,2 -15,089 -5,547 -1,938 260,2 -16,832 -6,375 -2,568 281,7 -17,855 -7,618 -2,757 290,3 -18,416 -8,313 -3,048 295 -18,861 -8,496 -3,248 300 -19,172 -8,873 -3,556 310,3 -9,168 -3,985 320 -9,473 -4,321 340,2 -10,116 -4,913 360,2 -10,812 -5,547 380,2 -11,835 -6,231 400,5 -12,69 -7,13 440,5 -14,333 -8,313 481,5 -15,493 -9,682 500,2 -15,917 -10,342 550,4 -17,855 -11,835 600,4 -19,015 -12,995 650,7 -20,354 -14,333 700 -15,089

Berdasarkan data hasil pengamatan untuk urutan rendah pada tabel 4.2, dapat dibuat grafik tanggapan magnitude untuk hasil pengamatan urutan rendah.

Gambar 4.1 menunjukkan tanggapan magnitude hasil pengamatan urutan rendah (dari urutan 1sampai urutan 3).

-21 -18 -15 -12 -9 -6 -3 0 3 10 100 1000 Frekuensi (Hz) P e n g u a ta n A m p li tu d o ( d B ) fc = 100 Hz fc = 200 Hz fc = 300 Hz

Gambar 4.1. Tanggapan magnitude hasil pengamatan dari urutan 1 sampai urutan 3

Berdasarkan tanggapan magnitude hasil pengamatan pada gambar 4.1 terlihat bahwa frekuensi cut-off adalah sebesar 95 Hz saat urutan ke 1, sebesar 187,5 Hz saat urutan ke 2 dan 280,4 Hz saat urutan ke 3.

Tanggapan amplitudo relatif MdB (ω) secara teoritis untuk urutan rendah dapat

ditunjukkan oleh tabel 4.3.

Tabel 4.3 Tanggapan amplitudo relatif MdB (ω) teoritis untuk urutan rendah Tanggapan Amplitudo (dB) Frekuensi (Hz) urutan ke 1 (fc =100 Hz) urutan ke 2 (fc =200 Hz) urutan ke 3 (fc =300 Hz) 10 0 0 0 40 -0,109 -0,006 -0,001 60,2 -0,535 -0,035 -0,007 80,2 -1,503 -0,11 -0,022 85,1 -1,831 -0,14 -0,028

Tanggapan Amplitudo (dB) Frekuensi (Hz) urutan ke 1 (fc =100 Hz) urutan ke 2 (fc =200 Hz) urutan ke 3 (fc =300 Hz) 90,7 -2,244 -0,179 -0,036 95,2 -2,604 -0,217 -0,043 100,4 -3,045 -0,267 -0,054 105 -3,454 -0,317 -0,064 110,3 -3,944 -0,384 -0,078 120,6 -4,935 -0,539 -0,111 130,5 -5,91 -0,723 -0,152 140,4 -6,889 -0,944 -0,203 150,3 -7,855 -1,202 -0,265 160,2 -8,8 -1,497 -0,339 170,5 -9,754 -1,841 -0,43 180,6 -10,658 -2,213 -0,535 190,5 -11,513 -2,608 -0,654 200,4 -12,337 -3,027 -0,788 210,5 -13,145 -3,477 -0,942 220,4 -13,908 -3,935 -1,11 240,2 -15,351 -4,886 -1,495 260,2 -16,706 -5,871 -1,947 281,7 -18,059 -6,933 -2,497 290,3 -18,574 -7,355 -2,734 295 -18,849 -7,584 -2,866 300 -19,138 -7,826 -3,01 310,3 -8,321 -3,313 320 -8,781 -3,606 340,2 -9,718 -4,238 360,2 -10,614 -4,882 380,2 -11,479 -5,538 400,5 -12,324 -6,207 440,5 -13,897 -7,519 481,5 -15,39 -8,828 500,2 -16,034 -9,409 550,4 -17,654 -10,909 600,4 -19,149 -12,315 650,7 -20,532 -13,642 700 -14,863

Berdasarkan tabel 4.3, dapat dibuat grafik tanggapan magnitude untuk urutan rendah untuk hasil secara teoritis. Gambar 4.2 menunjukkan tanggapan magnitude secara teoritis dari urutan ke 1 sampai urutan ke 3.

-21 -18 -15 -12 -9 -6 -3 0 10 100 1000 Frekuens i (Hz) P en g u at an A m p li tu d o ( d B ) fc = 100 Hz fc = 200 Hz fc = 300 Hz

Gambar 4.2 Tanggapan magnitude secara teoritis dari urutan ke 1 sampai urutan ke 3

Secara teoritis, untuk urutan ke 1 frekuensi cut-off adalah sebesar 100 Hz, sebesar 200 Hz saat urutan ke 2 dan sebesar 300 saat urutan ke 3. Berdasarkan data hasil pengamatan pada tabel 4.2 dan data secara teoritis pada tabel 4.3, dapat diketahui bahwa ada perbedaan nilai frekuensi cut-off pengamatan dan nilai secara teoritis. Adapun besarnya kesalahannya adalah sebagai berikut :

1) untuk urutan ke 1 (fc = 100 Hz) % 5 % 100 Hz 100 Hz 95 -Hz 100 = × 2) untuk urutan ke 2 (fc = 200 Hz) % 25 , 6 % 100 Hz 200 Hz 187,5 -Hz 200 = × 3) untuk urutan ke 3 (fc = 300 Hz) % 53 , 6 % 100 Hz 300 Hz 280,4 -Hz 300 = ×

Tanggapan amplitudo relatif MdB (ω) hasil pengamatan untuk urutan sedang

Tabel 4.4 Tanggapan amplitudo relatif MdB (ω) pengamatan untuk urutan sedang Tanggapan Amplitudo (dB) Frekuensi (Hz) urutan ke 100 (fc = 10 KHz) urutan ke 101 (fc = 10,1 KHz) urutan ke 102 (fc = 10,2 KHz) 50,4 0,137 0 0,137 100,3 0,34 0,34 0,34 200,7 0,205 0 0,205 400,2 0 0 0,137 600,6 0 0 0 800,9 0 0 0 1003 0 0 0 1506 0 0 0 1826 0 0 0 2052 0 0 0 3028 0 0 0 3534 0 0 0 4026 0 0 0 4512 -0,069 -0,069 0 5015 -0,354 -0,354 -0,211 5508 -0,5 -0,5 -0,354 6054 -0,649 -0,649 -0,5 6551 -0,915 -0,915 -0,8 7030 -1,26 -1,26 -1,11 7504 -1,43 -1,43 -1,26 8016 -1,93 -1,93 -1,76 8504 -2,29 -2,113 -2,113 9060 -2,66 -2,568 -2,47 9513 -2,95 -3,14 -2,8 10032 -3,248 -3,248 -2,95 10088 -3,34 -3,298 -3,248 10100 -3,452 -3,248 -3,452 10210 -3,715 -3,248 -3,452 10508 -4,32 -4,09 -3,66 11007 -4,43 -4,32 -4,09 11530 -5,03 -4,79 -4,67 12090 -5,67 -5,41 -5,28 13520 -7,13 -6,82 -6,82 14032 -7,61 -7,29 -7,29 15070 -8,49 -8,31 -8,13 15504 -8,87 -8,49 -8,49 16118 -9,26 -9,06 -9,06 17070 -10,22 -9,89 -9,68 18050 -11,05 -10,57 -10,34 19040 -11,56 -11,56 -11,3 20064 -12,69 -12,395 -12,11 20210 -12,841 -12,841 -12,541

Tanggapan Amplitudo (dB) Frekuensi (Hz) urutan ke 100 (fc = 10 KHz) urutan ke 101 (fc = 10,1 KHz) urutan ke 102 (fc = 10,2 KHz) 20410 -12,995 -12,995 -12,841 21030 -13,473 -13,31 -12,995 23075 -14,703 -14,516 -13,979 24020 -15,08 -14,89 -14,7 26040 -16,59 -16,13 -16,13 28060 -17,58 -17,32 -17,07 30111 -18,13 -18,13 -17,85 28060 -17,58 -17,32 -17,07 30111 -18,13 -18,13 -17,85

Berdasarkan data hasil pengamatan untuk urutan rendah pada tabel 4.4, dapat

dibuat grafik tanggapan magnitude untuk hasil pengamatan urutan sedang.

Gambar 4.3 menunjukkan tanggapan magnitude hasil pengamatan urutan sedang

(dari urutan 100sampai urutan 102).

-21 -18 -15 -12 -9 -6 -3 0 3 100 1000 10000 100000 Frekuensi (Hz) P e n g u a ta n A m p li tu d o ( d B ) fc = 10000 Hz fc = 10100 Hz fc = 10200 Hz

Gambar 4.3 Tanggapan magnitude hasil pengamatan untuk dari urutan ke 100 sampai urutan ke

102

Berdasarkan tanggapan magnitude hasil pengamatan pada gambar 4.3 terlihat

bahwa frekuensi cut-off adalah sebesar 9800 Hz saat urutan ke 100, sebesar 9950