Fakultas Pendidikan MIPA dan Teknologi IKIP PGRI Pontianak 254

MODUL TRAINER DIGITAL YANG DIGUNAKAN SEBAGAI

MODUL PEMBELAJARAN PENDIDIKAN VOKASI

BIDANG ELEKTRONIKA

Eko Mardianto1, Mohd. Ilyas Hadikusuma2

1,2Program Studi Teknik Elektronika Jurusan Teknik Elektro Politeknik Negeri Pontianak

Jl. Jenderal Ahmad Yani, Pontianak 78124

1e-mail: emardianto74@gmail.com

Abstrak

Modul trainer digital banyak sekali dijumpai saat ini, namun trainer yang bisa mewakili semua komponen dasar yang berhubungan dengan teknik digital amatlah sulit diperoleh karena membutuhkan banyak komponen yang harus disediakan dalam satu modul. Dalam penelitian ini, dibuat suatu modul trainer digital yang dapat mewakili semua komponen utama dalam teknik digital dasar yang dirancang dan direalisasikan menjadi sebuah modul berbasis FPGA. Modul trainer ini menyediakan tiga buah rangkaian utama yaitu rangkaian 1, 2 dan 3. Rangkaian 1 berisi tiga terminal gerbang dasar.Rangkaian 2 dan 3 berisi masing-masing dua terminal yang didalamnya mengandung rangkaian gerbang dasar, kombinasional dan sekuensial. Masing-masing terminal baik itu rangkaian 1, 2 ataupun 3 dapat dipilih secara fleksibel disetiap terminal sesuai dengan yang diinginkan. Modul trainer ini dibangun menggunakan FPGA Spartan 6 dengan memanfaatkan bahasa VHDL. Hasil uji tiap materi praktik dari modul trainer ini memperlihatkan keberhasilan yang baik sehingga layak dalam kegiatan praktikum digital.

Kata Kunci: FPGA, VHDL, trainer digital, modul trainer.

Abstract

The digital trainer modules are numerously found at present days, however, the trainer that could represent all basic components of digital engineering is very hard to be obtained because it requires many components to be provided in one module. In this research, a digital trainer module which represents all the main components in basic digital engineering will be designed and realized into an FPGA-based module. This trainer module provides three main circuits, those are circuit 1, circuit 2 and circuit 3. The circuit 1 contains three basic gate terminals. Each of circuit 2 and circuit 3 contains two terminals which consist of circuits of basic, combinational and sequential gates. Each terminal in circuit 1, circuit 2 or circuit 3 can be flexibly selected as ones desired. This trainer module is built by using FPGA Spartan 6 and utilizes the VHDL language. The test results of each practical subject of this trainer show great success so it is worthy for digital practice activity.

Keyword: FPGA, VHDL, digital trainer, trainer module.

PENDAHULUAN

Trainer digital banyak sekali dijumpai dipasaran dalam bentuk beberapa

modul gerbang dasar, rangkaian kombinasional dan rangkaian sequensial menggunakan jenis IC TTL ataupun CMOS. Namun modul trainer yang tersedia secara lengkap dalam satu modul menggunakan IC TTL tersebut sangat sulit ditemukan dikarenakan terlalu banyak komponen yang harus disediakan. Bila siswa atau mahasiswa ingin mempraktekkan suatu rangkaian yang terdiri dari rangkaian

Fakultas Pendidikan MIPA dan Teknologi IKIP PGRI Pontianak 255

gerbang, kombinasional dan sekuensial maka dibutuhkan beberapa modul dan tentunya membutuhkan juga meja yang cukup lebar untuk meletakkan modul tersebut.

Dalam penelitian ini penulis merancang dan merealisasikan sebuah modul yang dapat mewakili semua komponen dalam teknik digital dasar ke sebuah modul

trainer berbasis FPGA (Field Programmable Gate Array). Melalui modul ini

nantinya akan dapat dipraktikkan materi-materi teknik digital berupa gerbang logika dasar, rangkaian kombinasional dan rangkaian sekuensial yang telah diperoleh dalam pelajaran teori di kelas.

Gerbang logika dasar merupakan basis pembentukan sistem digital. Gerbang logika dasar ini meliputi gerbang And, Or, Nand, Nor, Ex-Or dan Ex-Nor. Melalui gerbang ini, sinyal analog sebesar 0 volt dan 5 volt (khusus IC jenis TTL) secara berturut-turut dikondisikan menjadi sinyal digital biner ‘0’ dan ‘1’.

Rangkaian kombinasional dapat dibuat dengan mengkonfigurasi beberapa gerbang logika dasar. Beberapa rangkaian kombinasional diantaranya meliputi

decoder, encoder, multiplexer, demultiplexer, adder, buffer, comparator. Kondisi

logika keluaran dari rangkaian kombinasional bergantung pada kombinasi kondisi logika masukannya.

Rangkaian sekuensial adalah rangkaian logika yang kondisi keluarannya dipengaruhi oleh masukan dan keadaan keluaran sebelumnya atau dapat dikatakan rangkaian yang bekerja berdasarkan urutan waktu. Ciri rangkaian logika sekuensial yang utama adalah adanya jalur umpan balik (feedback) di dalam rangkaiannya. Contoh dari Rangkaian sekuensial diantaranya adalah flip-flop, counter, dan

register.

Field Programming Gate Array (FPGA) adalah sebuah piranti logika yang

terdiri atas dimensi array CLB (Configurable Logic Block), interkoneksi pemograman dan blok I/O (Input/Output). Di dalam piranti ini terkandung gerbang logika biasa maupun fungsi matematis dan kombinasional yang lebih kompleks. Sebagian FPGA juga memiliki elemen memori (register) mulai dari flip-flop sampai pada RAM (Random Acces Memory). Gambar 1 menunjukkan salah satu contoh piranti FPGA tipe Xilinx Spartan 6. Tipe FPGA tersebut dapat

Fakultas Pendidikan MIPA dan Teknologi IKIP PGRI Pontianak 256

dikelompokkan menjadi 13 subfamily. Setiap subfamily Spartan 6 memiliki batasan kemampuan maksimum penggunaan logic cell, slices, penggunaan flip-flop dan kemampuan distribusi RAM-nya.

Gambar 1 Xilinx Spartan-6 XC6SLX-TQG144

METODE

Penelitian yang berkenaan dengan pembuatan trainer pernah dilakukan oleh Muhammad Irmansyah tahun 2009 yang merancang dan membuat multiplekser 4 input 1 output dan 2 selektor berbasis Programmable Logic Device (PLD) menggunakan IC PAL 22V10. PLD yang digunakan sebagai pengganti dari IC 74153.

Tahun 2013 Muhammad Irmansyah juga telah berhasil mengaplikasikan teknologi Programmable Logic Device (PLD) menggunakan IC PAL 22V10 untuk merancang rangkaian encoder desimal ke biner sebagai pengganti IC 74922. IC 74922 nantinya digunakan sebagai scanning pada keypad.

Rizky D.F dan Lusia Rahmawati telah berhasil membangun trainer digital yang berfungsi sebagai rangkaian register dan counter yang berdimensi 30 cm x 30 cm berbentuk kotak bewarna putih. Trainer ini dibangun menggunakan mikrokontroller ATmega 16, dimana I/O nya terdiri atas 12 buah saklar toggle, 2 buah project board, 3 terminal untuk terminal seven segment, terminal led output dan terminal input mikrokontroller, 8 buah led output, 1 LCD karakter 2 x 16, 2 LED untuk indikator clock dan indikator power. Berdasarkan hasil survei yang

Fakultas Pendidikan MIPA dan Teknologi IKIP PGRI Pontianak 257

telah mereka lakukan terhadap sejumlah mahasiswa yang telah menggunakan

trainer ini, 80 % mahasiswa menyatakan sangat baik.

Eko Mardianto dan Sy. Agus Salim di tahun 2015 melakukan penelitian dengan judul “Implementasi Modul Trainer Digital Berbasis Field Programmable Gate Array” yang dibiayai oleh DIPA Politeknik Negeri Pontianak dalam pelaksanaan Penelitian Terapan. Penelitian ini menghasilkan modul trainer digital gerbang dasar (And, Or, Nand, Nor, Xor, Ex Nor dan Inverter) yang terdiri atas 6 terminal gerbang 2 input, 4 terminal gerbang 3 input dan 3 terminal gerbang 4 input serta rangkaian kombinasional dengan fungsi adder. Masing-masing terminal gerbang dapat difungsikan sebagai gerbang And, Or, Nor, Nand, Xor, Ex Or ataupun Inverter secara fleksibel sesuai dengan keinginan user.

Pada Penelitian ini merupakan kelanjutan dari penelitian sebelumnya yaitu membuat sebuah modul trainer digital lengkap yang meliputi rangkaian gerbang dasar, rangkaian kombinasional dan rangkaian sekuensial dengan penambahan

clock yang digunakan sebagai masukan khusus pada rangkaian sekuensial yaitu counter. Trainer ini menyediakan input/output untuk gerbang dasar, rangkaian

kombinasi dan rangkaian sekuensial.

Penelitian yang dilakukan meliputi beberapa tahapan penelitian, yaitu sebagai berikut: (1) Penelitian pendahuluan. Penelitian diawali dengan penelitian pendahuluan, mencakup penelusuran literatur berkenaan dengan teori-teori dan cara melakukan pemogramman dengan FPGA, penelusuran produk sejenis di pasaran beserta karakteristiknya, serta penelusuran peralatan yang akan digunakan dalam penelitian; (2) Perancangan rangkaian logika. Tahap berikutnya adalah melakukan perancangan rangkaian logika dari sistem yang direncanakan, yaitu merancang rangkaian I/O untuk Rangkaian 1, Rangkaian 2, Rangkaian 3 dan Pulsa. Rangkaian 1 terdiri atas gerbang And, Or, Nand, Nor, Ex Or, dan Ex Nor. Rangkaian 2 dan 3 terdiri atas rangkaian gerbang dasar, Inverter, Buffer, Decoder

2 to 4, Decoder 3 to 8, BCD 7 segment, Encoder 8 to 3, Adder, Multiplexer, RS_Flip-Flop, JK_Flip-Flop, Latch 4 bit, Counter 4 bit, Shift Register, Demultiplexer atau Comparator. Rangkaian pulsa memiliki 3 keluaran yaitu 1 Hz,

Fakultas Pendidikan MIPA dan Teknologi IKIP PGRI Pontianak 258

Setelah itu merancang rangkaian pemilih untuk menentukan komponen yang akan difungsikan. Dalam pelaksanaan perancangan akan dilakukan per blok; (3) Pemogramman VHDL dan simulasi. Bila konsep rancangan rangkaian logika telah dilakukan selanjutnya desain diterjemahkan menggunakan bahasa VHDL. Setiap blok perancangan diuji dengan simulasi, bila hasil simulasi belum sesuai dengan kriteria yang diinginkan, maka proses pemogramman dengan VHDL diulangi (diperbaiki). Jika hasilnya sudah sesuai, proses dapat dilanjutkan ke tahap berikutnya. Simulasi program menggunakan software Modelsim 6.5. Bila program yang disimulasikan telah sukses dilakukan, selanjutnya program di download agar dapat dilihat unjuk kerjanya; (4) Pembuatan alat/realisasi trainer. Setelah dilakukan simulasi dan diperoleh hasil yang diinginkan selanjutnya dilakukan realisasi trainer dengan menempatkan bagian-bagian tertentu dari system sesuai dengan lay out yang sudah dirancang; (5) Pengujian sistem. Pengujian sistem dilakukan dengan cara melakukan pengetesan di masing-masing blok rangkaian. Setiap blok rangkaian diuji unjuk kerjanya, dimulai dari blok rangkaian 1, rangkaian 2 dan rangkaian 3. Selanjutnya melihat fungsi dari rangkaian pulsa, apakah pulsa keluaran sudah sesuai dengan yang dirancang. Pengujian berikutnya yaitu dengan memadukan keseluruhan rangkaian dengan membuat aplikasi percobaan yang tersedia dalam modul. Bila semua langkah telah dilakukan dan hasilnya sesuai dengan logika standar, maka trainer sudah bisa dikatakan layak untuk digunakan; dan (6) Produk. Produk akhir meghasilkan sebuah modul trainer digital yang digunakan sebagai pembelajaran dibidang teknik digital.

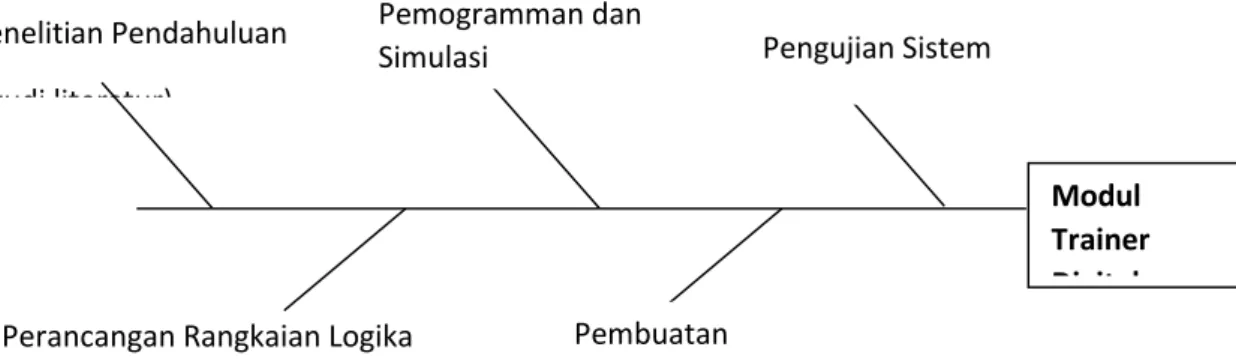

Tahapan penelitian berupa diagram alir ditunjukkan gambar berikut.

Gambar 2 Fishbone Diagam

Modul Trainer Digital Pengujian Sistem Pemogramman dan Simulasi Pembuatan Alat Penelitian Pendahuluan (studi literatur)

Fakultas Pendidikan MIPA dan Teknologi IKIP PGRI Pontianak 259

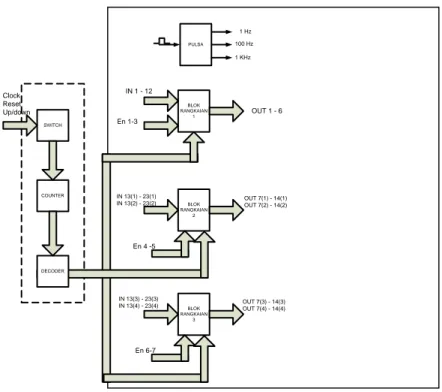

Gambar 3 menunjukkan blok diagram keseluruhan sistem yang terdiri atas tiga blok rangkaian besar yang dinamai dengan rangkaian 1, 2 dan 3. Blok switch, counter dan decoder merupakan rangkaian pemilih untuk menentukan komponen yang ingin difungsikan.

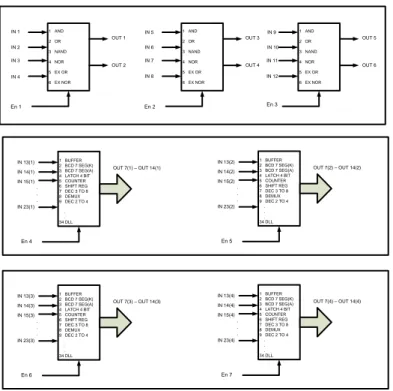

Isi masing-masing rangkaian ini ditunjukkan pada Gambar 4. Rangkaian 1 terdiri dari 3 terminal yang dapat digunakan. Setiap terminal hanya bisa difungsikan 1 komponen saja dengan pilihan gerbang And, Or,

Nand, Nor, Ex Or, dan Ex Nor. Masing-masing terminal terdiri atas 4 input

dan setiap gerbang hanya bisa diberi gerbang 2 input sampai gerbang 4 input saja. En 1 sampai 3 berguna untuk memastikan pilihan komponen yang akan difungsikan di masing-masing terminalnya yaitu dengan menekan tombol clock terlebih dahulu. Out 1 sampai 3 merupakan keluaran dari komponen yang telah dipilih.

BLOK RANGKAIAN 1 BLOK RANGKAIAN 2 BLOK RANGKAIAN 3 OUT 1 - 6 IN 1 - 12 En 4 -5 IN 13(1) - 23(1) IN 13(2) - 23(2) En 6-7 PULSA 1 Hz 1 KHz 100 Hz SWITCH COUNTER DECODER En 1-3 IN 13(3) - 23(3) IN 13(4) - 23(4) OUT 7(3) - 14(3)OUT 7(4) - 14(4) OUT 7(1) - 14(1) OUT 7(2) - 14(2) Clock Reset Up/down

Gambar 3 Blok Diagram Keseluruhan Sistem

Rangkaian 2 dan 3 terdiri dari rangkaian kombinasional dan rangkaian sekuensial diantaranya adalah inverter, buffer, decoder to 7

Fakultas Pendidikan MIPA dan Teknologi IKIP PGRI Pontianak 260 counter, register, comparator dan termasuk gerbang logika. Untuk memilih

komponen-komponen tersebut, terlebih dahulu menekan tombol clock. Tombol clock berfungsi untuk mencari komponen yang diinginkan.Setiap penekanan tombol clock menyebabkan indikator led akan menyala. Setelah

led berhenti pada komponen yang akan digunakan selanjutnya menekan

tombol enable yang terdapat pada setiap terminal.

Gambar 4 Blok Diagram Rangkaian 1 (atas), Rangkaian 2 (tengah) dan Rangkaian 3 (atas)

1 BUFFER 2 BCD 7 SEG(K) 3 BCD 7 SEG(A) 4 LATCH 4 BIT 5 COUNTER 6 SHIFT REG 7 DEC 3 TO 8 8 DEMUX 9 DEC 2 TO 4 . . . 34 DLL OUT 7(1) – OUT 14(1) IN 13(1) En 4 . . . IN 14(1) IN 23(1) IN 15(1) 1 BUFFER 2 BCD 7 SEG(K) 3 BCD 7 SEG(A) 4 LATCH 4 BIT 5 COUNTER 6 SHIFT REG 7 DEC 3 TO 8 8 DEMUX 9 DEC 2 TO 4 . . . 34 DLL OUT 7(2) – OUT 14(2) IN 13(2) En 5 . . . IN 14(2) IN 23(2) IN 15(2) 1 BUFFER 2 BCD 7 SEG(K) 3 BCD 7 SEG(A) 4 LATCH 4 BIT 5 COUNTER 6 SHIFT REG 7 DEC 3 TO 8 8 DEMUX 9 DEC 2 TO 4 . . . 34 DLL OUT 7(3) – OUT 14(3) IN 13(3) En 6 . . . IN 14(3) IN 23(3) IN 15(3) 1 BUFFER 2 BCD 7 SEG(K) 3 BCD 7 SEG(A) 4 LATCH 4 BIT 5 COUNTER 6 SHIFT REG 7 DEC 3 TO 8 8 DEMUX 9 DEC 2 TO 4 . . . 34 DLL OUT 7(4) – OUT 14(4) IN 13(4) En 7 . . . IN 14(4) IN 23(4) IN 15(4) 1 AND 2 OR 3 NAND 4 NOR 5 EX OR 6 EX NOR OUT 1 IN 1 En 1 IN 2 IN 4 IN 3 OUT 2 1 AND 2 OR 3 NAND 4 NOR 5 EX OR 6 EX NOR OUT 3 IN 5 En 2 IN 6 IN 8 IN 7 OUT 4 1 AND 2 OR 3 NAND 4 NOR 5 EX OR 6 EX NOR OUT 5 IN 10 IN 12 IN 11 OUT 6 IN 9 En 3

Fakultas Pendidikan MIPA dan Teknologi IKIP PGRI Pontianak 261

HASIL DAN PEMBAHASAN Rancangan Modul

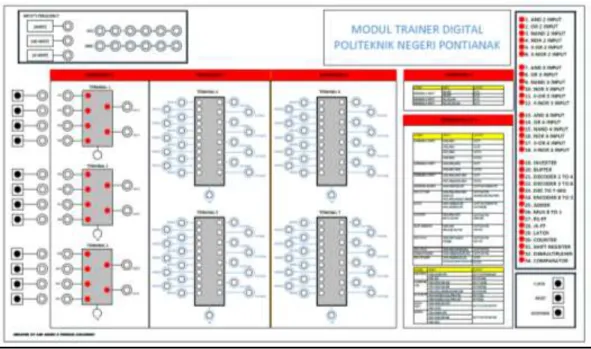

Gambar 5 Rancangan Modul Trainer Digital

Gambar 5 menunjukkan hasil rancangan modul trainer digital yang dapat digunakan sebagai media pembelajaran bagi siswa ataupun mahasiswa. Modul trainer digital ini memiliki supply tetap yaitu supply untuk kodisi logika ‘0’ dengan tegangan 0 volt dan supply untuk kondisi logika ‘1’ dengan tegangan sebesar 5 volt.

Supply ini digunakan sebagai masukan pada rangkaian, baik itu rangkaian 1, 2

maupun rangkaian 3 pada modul trainer. Selain supply terdapat juga masukan berupa frekuensi yang digunakan untuk masukan pada rangkaian counter. Frekuensi yang disediakan terdiri dari 1 Hz, 100 Hz dan 1 kHz.

Disediakan pula 12 tombol on/off yang digunakan sebagai masukan pada rangkaian 1,2 dan 3. Tombol ini akan berlogika ‘1’ apabila ditekan dan akan berlogika ‘0’ bila ditekan kembali. Gambar 6 menunjukkan rangkaian yang tersedia pada modul.

Fakultas Pendidikan MIPA dan Teknologi IKIP PGRI Pontianak 262

Gambar 6 Rangkain Pada Modul

Terdapat tiga buah rangkaian pada modul yaitu rangkaian 1, 2, dan 3. Rangkaian 1 terdiri atas gerbang-gerbang 2 input, 3 input dan 4 input. Masing-masing gerbang terdiri dari gerbang and, or, nand, nor, xor dan xnor. Untuk gerbang 2 input tersedia 2 buah gerbang, sedangkan untuk gerbang 3 input dan gerbang 4 input hanya tersedia 1 gerbang saja. Rangkaian 2 terdiri atas rangkaian gerbang-gerbang dasar, inverter, buffer, decoder 2 to 4, decoder 3 to 8, bcd 7

segment, encoder 8 to 3, adder, multiplexer, RS_flip-flop, JK_flip-flop, latch 4 bit, counter 4 bit, shift register, demultiplexer atau comparator. Isi modul yang terdapat

pada rangkaian 3 ini sama seperti pada rangkaian 2.

Pada rangkaian pulsa ini hanya menyediakan pulsa dengan frekuensi 1 Hz, 100 Hz dan 1 kHz. Rangkaian pulsa ini dapat digunakan pada rangkaian counter.

Fakultas Pendidikan MIPA dan Teknologi IKIP PGRI Pontianak 263

Gambar 7 menunjukkan petunjuk dari rangkaian 1. Rangkaian 1 terdiri atas: (1) gerbang 2 input (and, or, nand, nor, xor, xnor). Gerbang 2 input yang dapat digunakan hanya dua buah gerbang dengan IN1 dan IN2 sebagai input gerbang pertama dan OUT1 sebagai outputnya. IN3 dan IN4 berfungsi sebagai input Gerbang kedua dan OUT2 sebagai outputnya. (2) gerbang 3 input (and, or, nand,

nor, xor, xnor). Gerbang 3 input hanya tersedia satu gerbang disetiap terminal pada

rangkaian 1, dengan input IN1, IN2 dan IN3. Output gerbang 3 input berada pada Out 1. (3) gerbang 4 input (and, or, nand, nor, xor, xnor). Sebagaimana di gerbang 3 input, gerbang 4 input juga hanya memiliki satu gerbang disetiap terminal pada rangkaian 1 ini. Inputnya adalah IN1, IN2, IN3 dan IN4 sedangkan outputya adalah OUT1

Gambar 5 yang berada pada sisi kanan gambar merupakan indikator modul trainer yang akan dioperasikan oleh pengguna. Bila pengguna mengaktifkan rangkaian decoder 2 to 4 maka led nomor 21 akan menyala sedangkan led lainnya tidak akan menyala. Sementara Gambar 8 digunakan sebagai tombol operasi clock,

reset dan saklar up/down. Tombol clock berfungsi untuk melakukan pemilihan

rangkaian yang akan difungsikan. Reset digunakan untuk mengembalikan ke posisi pemiihan awal yaitu di nomor 1 yaitu gerbang AND 2 input. Saklar Up digunakan untuk menghitung naik bila tombol clock ditekan dan Down digunakan untuk hitung mundur bila tombol clock ditekan.

Gambar 8 Tombol Operasi

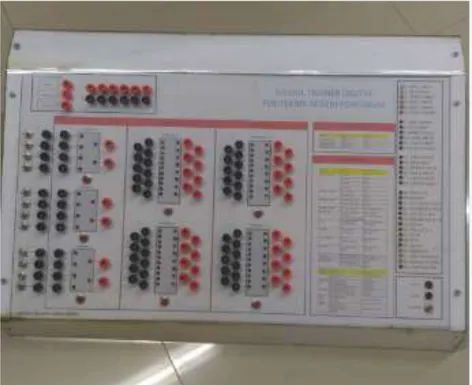

Untuk melihat bentuk fisik dari trainer yang telah dibuat ditunjukkan pada Gambar 9.

Fakultas Pendidikan MIPA dan Teknologi IKIP PGRI Pontianak 264

Gambar 9 Bentuk fisik Modul Trainer Digital

Hasil Simulasi

Gambar 10 merupakan gambar contoh program gerbang dasar memanfaatkan software Xilinx ise 7.1.

Gambar 10. Contoh Program Gerbang Dasar

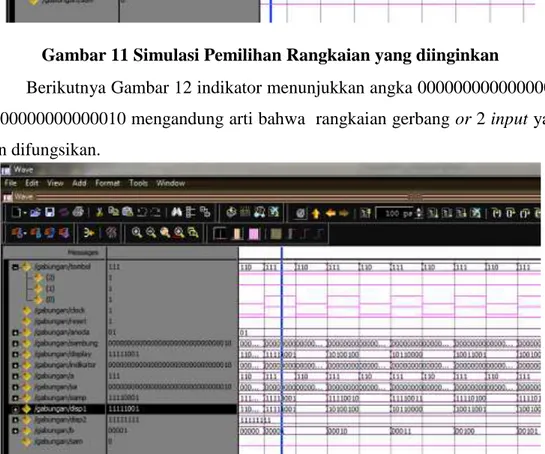

Dari listing program tersebut diperoleh hasil simulasi yang ditunjukkan gambar 11. Pada gambar 11 menunjukkan pemilihan rangkaian yang ingin difungsikan. Indikator menunjukkan angka

000000000000000000000000000000-Fakultas Pendidikan MIPA dan Teknologi IKIP PGRI Pontianak 265

001 mengandung arti bahwa rangkain gerbang and 2 input yang siap untuk difungsikan.

Gambar 11 Simulasi Pemilihan Rangkaian yang diinginkan

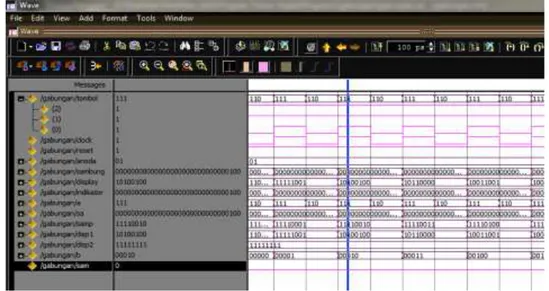

Berikutnya Gambar 12 indikator menunjukkan angka 0000000000000000-00000000000000010 mengandung arti bahwa rangkaian gerbang or 2 input yang akan difungsikan.

Gambar 12 Simulasi Pemilih Rangkaian yang diinginkan 2 Sementara Gambar 13 akan memfungsikan gerbang nand 2 input.

Fakultas Pendidikan MIPA dan Teknologi IKIP PGRI Pontianak 266

Gambar 13 Simulasi Pemilihan rangkaian yang diinginkan 3

Gambar 14 merupakan gambar yang menunjukkan simulasi pemilihan rangkaian gerbang 2 input.

Gambar 14 Simulasi Pemilihan Rangkaian Gerbang 2 Input

Dat 000001 mengandung arti bahwa gerbang and 2 input yang akan difungsikan. Pada gerbang and tersebut, input yang diberikan adalah aya1 = 1 dan baya 1 = 0 akan menghasilkan output y1 = 0. Gerbang berikutnya aya2 = 1 dan baya2 = 1 akan menghasilkan output y2 = 1.

Fakultas Pendidikan MIPA dan Teknologi IKIP PGRI Pontianak 267

Gambar 15. Simulasi Pemilihan Rangkaian Gerbang 2 Input (2) Untuk gambar 15 adalah gambar yang memfungsikan gerbang or 2 input, yang ditandai dengan keterangan dat 000010.

Keterangan :

dat 000001 artinya memfungsikan gerbang and dat 000010 artinya memfungsikan gerbang or dat 000100 artinya memfungsikan gerbang nand dat 001000 artinya memfungsikan gerbang nor dat 010000 artinya memfungsikan gerbang xor dat 100000 artinya memfungsikan gerbang exor

SIMPULAN

Dari hasil eksperimen yang telah dilakukan menunjukkan bahwa modul

trainer ini dapat digunakan sebagai modul pembelajaran. Bentuk fisik atau hardware dari modul trainer layak dan mudah digunakan sebagai media

pembelajaran dan memiliki kecenderungan lebih lengkap dibanding modul digital yang ada.

UCAPAN TERIMA KASIH

Ucapan terima kasih diucapkan kepada Direktorat Riset dan Pengabdian Masyarakat, Kementerian Riset, Teknologi, dan Pendidikan Tinggi RI yang telah mendanai penelitian ini. Terima kasih juga disampaikan kepada Unit Penelitian

Fakultas Pendidikan MIPA dan Teknologi IKIP PGRI Pontianak 268

dan Pengabdian Masyarakat Politeknik Negeri Pontianak, Jurusan Teknik Elektro, serta semua pihak yang tidak dapat disebutkan satu persatu sehingga penelitian ini dapat diselesaikan.

DAFTAR PUSTAKA

Floyd. 2006. Digital Fundamentals. New Jersey: Prentice Hall, Ninth Edition Irmansyah, M. 2009. Multiplekser Berbasis Programmable Logic Device (PLD).

Jurnal Elektron, 1(2): 13.

Irmansyah, M. 2013. Pengimplementasian Teknologi Programmable Logic Device (PLD) Sebagai Biner Code Decimal (BCD) Untuk Scanning Keypad. Jurnal

Elektron, 5(1): 9.

Mardianto, E. & Salim, A. 2015. Implementasi Modul Trainer Digital Berbasis

Field Programmable Gate Array. Makalah dalam Seminar Nasional Forum

Pendidikan Tinggi Teknik Elektro Indonesia di Pontianak 6 Oktober 2015. Tema: Peran Pendidikan Tinggi Teknik Elektro Dalam Mewujudkan Ketahanan dan Keberlajutan Energi Nasional.

Rizky D.W. & Lusia, R. 2014. Trainer Digital Register dan Counter Sebagai Media Pembelajaran Untuk Mahasiswa Elektronika Komunikasi di Jurusan Teknik Elektro Universitas Negeri Surabaya, Jurnal Unesa halaman 553.

Xilinx. 2008. Spartan 3 FPGA Starter Kit Board. USA: User Guide. Xilinx. 2010. FPGA Spartan 6 tipe XC6SLX9.