DASAR-DASAR

TEKNIK DIGITAL

SEMESTER III

PROGRAM STUDI TEKNIK LISTRIK

JURUSAN ELEKTRO

POLITEKNIK NEGERI MALANG

OLEH :

ANANG DASA NOVFOWAN NIP : 131 953 231

TUTWURI HANDAYANI

DEPARTEMEN PENDIDIKAN & KEBUDAYAAN POLITEKNIK NEGERI MALANG

JURUSAN TEKNIK ELEKTRO PROGRAM STUDI TEKNIK LISTRIK

KATA PENGANTAR

Puji syukur penulis sampaikan kepada Allah SWT, karena hanya berkat rahmat dan hidayah-Nya penulis dapat menyelesaikan buku ajar untuk mata kuliah TEKNIK DIGITAL Semester III Politeknik Negeri Malang.

Pada kesempatan ini pula, penulis dengan segala kerendahan hati menyampaikan rasa hormat dan terima kasih kepada semua pihak terutama rekan-rekan pengajar Program Studi Teknik Listrik Politeknik Negeri Malang, yang telah banyak memberikan masukan ide, saran, dan kritik demi meningkatkan qualitas penyampaian buku ini.

Akhirnya penulis berharap buku ini berguna bagi setiap orang yang membaca/mempelajarinya.

Penulis Malang, Agustus 2000

DAFTAR ISI

Halaman

Kata Pengantar i

Daftar Isi ii

BABI ELEMEN-ELEMEN RANGKAIAN DIGITAL 1

1.1. Pengertian Umum 1

1.2 Data Analog dan Digital 1

1.3 Logika Biner 2

1.4 Sistem Bilangan 3

1.5 Operasi Aritmatika 8

BAB II OPERASI DATA BINER 18

2.1. Operasi Logika 18

2.2. Logika Dan Statement (Pernyataan) 21

2.3. Truth Table (Tabel Kebenaran) 21

2.4. Aljabar Boolean 22

2.5. Karnough Map 27

BAB III LOGIKA KOMBINASIONAL 35

3.1. Prosedur Design 35

3.2. Konversi Kode 37

BAB IV RANGKAIAN SEQUENSIAL 42

4.1. Pendahuluan 42

BAB V RANGKAIAN KOMBINASIONAL DENGAN MSI (MEDIUM SCALE INTEGRATION) DAN LSI

(LARGE SCALE INTEGRATION) 52

5.1. Penjumlah (Adder) 52

5.2. Empat Bit Full Adder 57

5.3. Decoder 60

5.4. Demultiplexer 63

5.5. Encoder 66

5.6. Multiplexer 67

BAB VI REGISTER DAN COUNTER PADA RANGKAIAN

SEQUENSIAL MSI DAN LSI 73

6.1. Shift Register (Register Geser) 74

6.2. Counter (Pencacah) 78

BAB VII ASSIGNMENT TEST 94

BAB I

ELEMEM-ELEMEN RANGKAIAN DIGITAL

1.1. PENGERTIAN UMUM

Rangkaian digital meliputi setiap aspek kehidupan kita, peralatan ini tidak hanya digunakan pada sistem/peralatan teknik saja, tetapi juga untuk memenuhi kebutuhan komsumen lainnya seperti personal computer, microwave oven, automobile, airline reservation system, telephone exchange, digital voltmeter, calculator, dan lain sebagainya. Semua itu melibatkan rangkaian digital untuk tujuan pemrosesan informasi dan/atau membentuk fungsi kontrolyang diinginkan. Pada hampir semua aktifitas, kita selalu berhubungan dengan quantitas dan pengukuran. Informasi ini diperoses dalam bentuk digital yang dapat diekspresikan dalam bentuk elektronik.

1.2.DATA ANALOG DAN DIGITAL

Langkah pertama dalam operasi pemrosesan data adalah menentukan informasi tentang obyek atau sesuatu yang menarik. Perolehan informasi biasanya melibatkan pengambilan data pengukuran.

Pengukuran dapat dibagi menjadi 2 katagori; Pengukuran analog adalah terus-menerus (continous) dan merupakan fungsi dari para meter yang diukur. Sebaliknya Digital adalah terputus-putus (discrete) dan ini hanya dapat berubah pada satuan yang tetap.

Gambar 1.1. a. Sistem Digital b. Sistem Analog

Gambar diatas menunjukkan 2 gelas kimia yang sedang diisi air , yang satu diisi dari kran (tap) dengan air menetes, sedangkan yang lain dengan kran mengucur. Keadaan air pada gelas kimia (a) mempunyai sifat digital, dimana perubahan volume yang kecil itu sama dengan satu tetes air dan kenaikan volumenya naik menurut step-step. Pada gelas (b), volume air naik secara kontinyu, maka ini merupakan sifat analog.

1.3. LOGIKA BINER

Logika biner mensyaratkan 2 karakteristik yang berbeda : variabel yang mempunyai 2 harga dan tepat untuk operasi logika. Berbeda dengan bilangan-bilangan biasa, harga variabel dalam logika biner hanya memiliki 2 keadaan. Suatu pasangan yang dapat menunjukkan 2 keadaan tersebut dapat diambil contoh sebagai berikut :

Buka dan tutup, tinggi (high) dan rendah (low), panas dan dingin, benar dan salah. Pasangan kondisi tersebut dapat dipresentasikan sebagai variabel biner yaitu ‘0’ dan ‘1’. Jika dua kondisi tersebut dioperasikan berulang-ulang maka akan terjadi

V o lu m e Waktu (t) V o lu m e Waktu (t)

a. Penambahan Volume secara discrete b. Penambahan Volume secara continous

sistem digital, sebagai contoh level tegangan yang berubah dari tinggi ke randah atau rendah ke tinggi.

1.4. SISTEM BILANGAN 1.4.1. Pengertian Umum.

Dalam kehidupan sehari-hari, kita sudah terbiasa menggunakan sistem bilangan desimal yang mempunyai komponen dari 0 sampai 9. Jika bilangan tersebut lebih dari 9 maka harus dituliskan dalam 2 digit atau lebih dengan ketentuan bahwa posisi paling kanan adalah satuan kemudian puluhan, ratusan, ribuan dst.

Untuk mengekspresikan bilangan desimal dapat ditunjukkan seperti contoh berikut : Sebuah bilangan desimal 7392 mewakili suatu persamaan penjumlahan dari :

7 ribuan + 3 Ratusan + 9 puluhan + 2 satuan

Ribuan, ratusan, puluhan dan satuan merupakan pemangkatan dari 10 yang menunjukkan posisi dari koefisien-koefisien. Untuk lebih jelasnya dapat ditulis sebagai berikut :

7392 = 7 x 103 + 3 x 102 + 9 x 101 + 2 x 100

Secara umum posisi koefisien dapat ditulis sebagai berikut : = a 3 a 2 a 1 a 0 , a-1 a-2 a-3

atau dapat diexpresikan sebagai berikut :

= a 3 . 103 + a 2 . 102 + a 1 . 101 + a 0 . 100 + a-1 . 10-1 + a-2 . 10-2 + a-3 . 10-3

Dari penjelasan diatas, maka dapat dituliskan rumus umum dan diekspresikan dengan bilangan R dan koefisien a :

a n . Rn + a n-1 . Rn-1 + … + a 1 . R1 + a 0 . R0 + a-1 . R-1 + … + a-n . R-n ……. 1)

1.4.2. Basis Bilangan

Dalam sistem digital ada beberapa sistem bilangan yang sering dipakai, diantaranya :

- Bil. Oktal , bilangan ini dipakai pada sispemrograman untuk komputer generasi awal.

- Bil Desimal adalah bilangan yang setiap hari kita pakai.

- Bil Hexidesimal adalah bilangan yang dipakai untuk manipulasi data pada software operasi microproccessor saat ini.

No Jenis Bilangan

Basis Bilangan Komponen

1. Biner Bil. Berbasis 2 0, 1

2. Oktal Bil. Berbasis 8 0, 1, 2, 3, 4, 5, 6, 7 3. Desimal Bil. Berbasis 10 0, 1, 2, 3, 4, 5, 6, 7, 8, 9

4. Hexadesimal Bil. Berbasis 16 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F

1.4.3. Conversi Bilangan

Untuk mengetahui hubungan antara jenis bilangan satu dengan yang lain, maka perlu dijelaskan bagaimana sistem konversi bilangan tsb, dengan menggunakan referensi bilangan yang paling kita kenal yaitu Bil. Desimal.

1.4.3.a. Konversi Bilangan Lain ke Bil. Desimal

Sebagai contoh, jika bilangan biner dikonversikan ke desimal akan membentuk suatu penjumlahan dari 2 yang mempunyai komponen 1 .

Contoh :

(1010,011)2 = 1 x 23 + 0 x 22 + 1x 21 + 0 x 20 + 0 x 2-1 + 1 x 2-2 + 1x 2-3

= 8 + 0 + 2 + 0 + 0 + 0,25 + 0,125 = ( 10,375 )10

1.4.3.b. Konversi Bilangan Desimal ke Bilangan Lain

Konversi dari bilangan desimal ke bilangan lain dapat dilakukan dengan menggunakan prinsip : membagi bilangan desimal dengan basis bilangan tujuan secara berulang-ulanghingga mendapatkan hasil pembagian sama dengan 0, dan menuliskan sisanya pada setiap pembagian.

Hal ini dapat dijelaskan dengan contoh berikut ini. Contoh :

Konversikan bilangan desimal 41 ke bil biner (bil. berbasis 2) menggunakan sistem sisa 41 : 2 = 20 sisa 1 a0 20 : 2 = 10 sisa 0 a1 10 : 2 = 5 sisa 0 a2 5 : 2 = 2 sisa 1 a3 2 : 2 = 1 sisa 0 a4 1 : 2 = 0 sisa 1 a5 Maka : ( 41 )10 = (a5 a4 a3 a2 a1 a0 )2 = ( 1 0 1 0 0 1 )2

Untuk konversi dari bil desimal pecahan ke bilangan lain dapat menggunakan metode yang sama dengan bilangan bulat biasa, tetapi disini menggunakan perkalian. Dan lebih jelasnya dapat dijelaskan dengan contoh berikut.

Contoh :

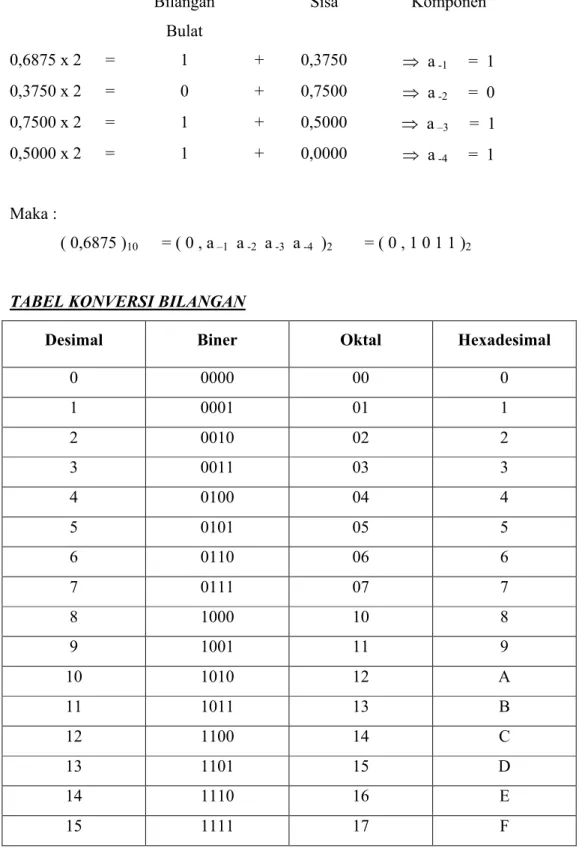

Konversikan bilangan ( 0,6875 )10 ke bilangan biner

Bilangan Bulat Sisa Komponen 0,6875 x 2 = 1 + 0,3750 a-1 = 1 0,3750 x 2 = 0 + 0,7500 a-2 = 0 0,7500 x 2 = 1 + 0,5000 a–3 = 1 0,5000 x 2 = 1 + 0,0000 a-4 = 1 Maka : ( 0,6875 )10 = ( 0 , a–1 a-2 a-3 a-4 )2 = ( 0 , 1 0 1 1 )2 TABEL KONVERSI BILANGAN

Desimal Biner Oktal Hexadesimal

0 0000 00 0 1 0001 01 1 2 0010 02 2 3 0011 03 3 4 0100 04 4 5 0101 05 5 6 0110 06 6 7 0111 07 7 8 1000 10 8 9 1001 11 9 10 1010 12 A 11 1011 13 B 12 1100 14 C 13 1101 15 D 14 1110 16 E 15 1111 17 F

1.4.4. Bilangan OKTAL dan HEXADESIMAL

Konversi dari dan ke bilangan biner, oktal, hexadesimal mempunya peran yang sangat penting dalam komputer digital. Karena ketiga jenis bilangan tersebut memiliki hubungan yang unik 23 = 8 dan 24 = 16 , setiap sati digit bilangan oktal merupakan konversi dari 3 digit biner dan setiap digit dari hexadesimal merupakan konversi dari 4 bilangan biner.

Konversi dari bilangan biner ke bilangan oktal dapat dilakukan dengan mengelompokkan bilangan biner setiap 3 digit , yang dimulai dari titik biner (koma “,”) ke kiri dan ke kanan, contoh dibawah ini menggambarkan prosedur di atas.

Bilangan Biner Ke Oktal

( 10 110 001 101 011 , 111 100 000 110 )2 = ( 2 6 1 5 3 , 7 4 0 6 )8

2 6 1 5 3 7 4 0 6

Bilangan Biner Ke Hexadesimal :

( 0010 1100 0110 1011 , 1111 0010 )2 = ( 2 C 6 B , F 2 )16

2 C 6 B F 2 Bilangan Oktal ke Biner

( 6 1 7 3 4, 3 1 )8 = ( 110 001 111 011 100 , 011 001 )2

Bilangan Hexadesimal ke Biner

1.5. OPERASI ARITMATIKA

Operasi aritmatika dengan bilangan berbasis-R mempunyai aturan yang sama dengan sistem desimal. Seperti halnya desimal, bilangan biner dapat ditambah, dikurangi, dikalikan dan dibagi. Karena bilangan biner ini hanya mempunyai 2 komponen (0 dan 1) maka operasi aritmatika dapat kita lakukan dengan lebih singkat dan sederhana. Dan sebenarnya semua operasi aritmatika didasarkan pada sistem penjumlahan.

1.5.1. PENJUMLAHAN

Sebelum membahas lebih lanjut tentang penjumlahan bilangan biner ini, sebaiknya kita lihat kembali aturan penjumlahan pada bilangan desimal.

Pada penjumlahan desimal, yang pertama dijumlahkan adalah kolom satuan, jika hasil penjumlahan tsb kurang dari sepuluh maka hasil tsb dituliskan pada kolom satuan. Jika hasil penjumlahannya lebih besar dari sepuluh, satuan dituis pada kolom satuan dan satu dilimpahkan masuk ke kolom puluhan. Kemudian, digit-digit pada kolom puluhan dijumlahkan bersama dengan limpahan (yang selanjutnya disebut CARRY) jika ada. Kalau hasilnya kurang dari sepuluh, hasilnya dituliskan pada kolom puluhan, jika hasilnya lebih besar dari sepuluh, maka satuan dituliskan pada kolom puluhan dan satu dilimpahkan ke kolom ratusan, dst. Contoh : A = 273 dan B = 48 maka A + B = 1 1 0 2 7 3 A 4 8 + B 3 2 1 A + B

Aturan diatas digunakan juga untuk menjumlahkan bilangan biner. Untuk penjumlahan 2 buah bilangan biner 1 bit (yang paling sederhana), dapat dilihat

0 + 0 = 0

0 + 1 = 1

1 + 0 = 1

1 + 1 = 102

Atau dapat dituliskan dengan tabel berikut ini : Tabel Penjumlahan 2 buah bil. Biner 1 digit

A B Carry (C) Hasil (S)

0 0 0 0

0 1 0 1

1 0 0 1

1 1 1 0

Untuk penjumlahan biner dengan digit lebih dari satu, dapat dijelaskan dengan contoh-contoh berikut : Contoh : A = 1010 B = 0100 1 0 1 0 0 1 0 0 + S = 1 1 1 0 C = 1 0 0 0 Maka A + B = 1 1 1 0

Contoh : A = 1010 B = 0010 0 1 0 1 0 1 0 0 0 1 0 + S = 1 1 0 0 C = 0 0 1 0 Maka A + B = 1 1 0 0 Contoh : A = 1010 B = 1110 1 1 0 1 0 1 0 1 1 1 0 + S = 1 0 0 0 C = 1 1 1 0 Maka A + B = 1 1 0 0 0

1.5.2. PENGURANGAN

Pada sistem biner, operasi pengurangan dapat dilakukan dengan menggunakan aturan dasar sbb:

0 - 0 = 0

0 - 1 = 1

1 - 0 = 1

102 - 1 = 1

Jika kita mengurangkan bilangan, kadang kita harus meminjam dari bit yang lebih tinggi. Pinjam (borrow) ini dibutuhkan jika kita mengurangkan 0 dengan 1 . Dalam hal ini, jika 1 dipinjam dari bit berikutnya maka akan timbul 102 pada baris

yang dikurangi, contoh-contoh dibawah ini menggambarkan sistem di atas. Contoh : 1 1 A 1 1 A 0 1 - B 1 0 - B 1 0 A - B 0 1 A - B Contoh : 1 0 1 A 0 1 1 - B 0 1 0 A - B

1.5.3. KOMPLEMEN

Komplemen digunakan dalam komputer digital untuk menyederhanakan operasi pengurangan (subtraction) dan untuk manipulasi logika. Ada dua tipe komplemen untuk setiap sistem bilangan basis-r :

a. Komplemen r b. Komplemen r-1

Jika harga tersebut disubstitusikan , dua tipe tsb akan diberinama komplemen 2 dan komplemen 1 untuk bilangan biner, atau komplemen 10 dan komplemen 9 untuk bilangan desimal.

1.5..3.1. Komplemen r

Suatu bilangan positif N dalam basis-r dengan bilangan bulat sebanyak n digit, maka komplemen r dari N dapat didefinisikan sebagai rn - N untuk N 0 dan 0 untuk N = 0. Contoh-contoh berikut ini akan memperjelas definisi diatas :

- Komplemen 10 dari (52520)10 adalah 105– 52520 = 47480

Jumlah digit pada bilangan ini adalah n=5

- Komplemen 10 dari (0,3267)10 adalah 1 – 0,3267 = 0,6733

Tanpa bilangan bulat maka 10n = 100 = 1

- Komplemen 10 dari (25,639)10 adalah 102– 25,639 = 74,361

- Komplemen 2 dari (101100)2 adalah (26)

10– (101100)2 =

(1000000 – 101100)2 = 010100

- Komplemen 2 dari (0,0110)2 adalah ( 1 – 0,0110 )2 = 0,1010

1.5..3.2. Pengurangan dengan Komplemen r

pengurangannya. Jika pengurangan ini dikembangkan pada komponen digital, metode diatas terlihat kurang efisien maka disini dikembangkan dengan metode komplemen dan penjumlahan komplemen.

Pengurangan dua bilangan positif (M – N) yang keduanya mempunyai basis yang sama ( r ) , dapat dilakukan dengan prosedur berikut :

1. Jumlahkan bilangan yang dikurangi (M) dengan komplemen r dari pengurang (N).

2. Lihat hasil dari step 1 untuk sebuah end carry (limpahan akhir) a. Jika terjadi end carry abaikan itu.

b. Jika tidak terjadi end carry maka hasil pengurangannya adalah komplemen dari hasil step 1 dan tambahkan tanda negatif ( - ) didepannya.

Contoh-contoh berikut ini menggambarkan prosedur diatas : Contoh :

Menggunakan komplemen 10 kurangkan 72532 – 3250

M = 7 2 5 3 2 7 2 5 3 2 N = 0 3 2 5 0 Komplemen 10 dari N = 9 6 7 5 0 + 9 6 7 5 0 End Carry 1 6 9 2 8 2 Maka hasilnya = 6 9 2 8 2 Contoh : Kurangkan ( 3250 – 72532)10 M = 0 3 2 5 0 0 3 2 5 0 N = 7 2 5 3 2 Komplemen 10 dari N = 2 7 4 6 8 + 2 7 4 6 8 Tanpa Carry 0 3 0 7 1 8 Hasilnya = - (komplemen 3 0 7 1 8) = - 6 9 2 8 2

Contoh :

Gunakan komplemen 2 untuk menunjukkan pengurangan (M – N) dari bilangan biner: M = 1 0 1 0 1 0 0 1 0 1 0 1 0 0 N = 1 0 0 0 1 0 0 Komplemen 2 dari N = 0 1 1 1 1 0 0 + 0 1 1 1 1 0 0 End Carry 1 0 0 1 0 0 0 0 Hasilnya = 0 0 1 0 0 0 0 M = 1 0 0 0 1 0 0 1 0 1 0 1 0 0 N = 1 0 1 0 1 0 0 Komplemen 2 dari N = 0 1 0 1 1 0 0 + 0 1 0 1 1 0 0 Tanpa Carry 0 1 1 1 0 0 0 0 Hasilnya = - (komplemen 2 dari 1110000)

= - 1 0 0 0 0

1.5..3.3. Komplemen ( r – 1 )

Suatu bilangan N pada basis r dengan bagian bilangan bulat sebanyak n digit dan bagian pecahan m digit, maka komplemen ( r – 1 ) dari N didefinisikan sebagai rn-r-m-N. Contoh-contoh secara numerik dapat diberikan sebagai berikut :

- Komplemen 9 dari (52520)10 adalah 105–1-52520 = 99999-52520 = 47479

Tanpa pecahan maka 10-m = 100 = 1

- Komplemen 9 dari (0,3267)10 adalah 1-10-4–0,3267 = 0,9999-0,3267 = 0,6733

=74,361 - Komplemen 1 dari (101100)2 adalah (26-1)

10– (101100)2 =

(111111 – 101100)2 = 010100

- Komplemen 1 dari (0,0110)2 adalah ( 1 – 2-4)10– (0,0110)2 =

( 0,1111 – 0,0110 )2 = 0,1001

Dari contoh-contoh diatas dapat disimpulkan bahwa komplemen 9 dari bilangan desimal adalah terbentuk dari pengurangan srtiap digitnya dengan 9. Dan komplemen 1 dari bilangan biner lebih mudah dibentuk yaitu dengan merubah 1 ke 0 atau 0 ke 1.

Dari definisi dan perbandingan hasil-hasil yang didapat pada contoh-contoh diatas, dapat diketahui bahwa komplemen r bisa ditentukan dari komplemen ( r – 1 ) dengan penambahan r-m pada digit yang paling rendah (LSB). Sebagai contoh: Komplemen 2 dari 1 0 1 1 0 1 0 0 dapat dihasilkan dari komplemen 1

1.5.3.4. Pengurangan dengan komplemen ( r – 1 )

Prosedur pada pengurangan dengan komplemen (r – 1) adalah sama dengan prosedur yang digunakan pada komplemen r, kecuali satu variasi yaitu end-around-carry (limpahan memutar) seperti terlihat dibawah ini.

Pengurangan M – N, keduanya adalah bilangan positif dengan baisi r, dapat dihitung dengan prosedur berikut:

1. Tanbahkan bilangan yang dikurangi M dengan komplemen (r – 1) dari pengurang N.

2. Lihat hasil dari step 1 untuk end-carry nya.

a. Jika terjadi end-carry, tambahkan 1 ke digit paling rendah (end-around-carry).

b. Jika tidak terjadi end-carry, ambil komplemen (r – 1) dari bilangan yang dihasilkan oleh step 1 dan tuliskan tanda negatif ( - ) didepannya.

Contoh-contoh dibawah ini menggambarkan prosedur tersebut : Contoh :

Menggunakan komplemen 9 kurangkan 72532 – 3250

M = 7 2 5 3 2 7 2 5 3 2 N = 0 3 2 5 0 Komplemen 9 dari N = 9 6 7 4 9 + 9 6 7 4 9 End Carry 1 6 9 2 8 1 + 1 6 9 2 8 2 Maka hasilnya = 6 9 2 8 2 Contoh : Kurangkan ( 3250 – 72532)10

N = 7 2 5 3 2

Komplemen 9 dari N = 2 7 4 6 7 + 2 7 4 6 7 Tanpa Carry 0 3 0 7 1 7 Hasilnya = - (komp. 9 dari 3 0 7 1 7)

= - 6 9 2 8 2 Contoh :

Gunakan komplemen 1 untuk menunjukkan pengurangan (M – N) dari bilangan biner: M = 1 0 1 0 1 0 0 1 0 1 0 1 0 0 N = 1 0 0 0 1 0 0 Komplemen 1 dari N = 0 1 1 1 0 1 1 + 0 1 1 1 0 1 1 End Carry 1 0 0 0 1 1 1 1 End-around-carry + 1 0 0 1 0 0 0 0 Hasilnya = 1 0 0 0 0 M = 1 0 0 0 1 0 0 1 0 1 0 1 0 0 N = 1 0 1 0 1 0 0 Komplemen 1 dari N = 0 1 0 1 0 1 1 + 0 1 0 1 0 1 1 Tanpa Carry 0 1 1 0 1 1 1 1 Hasilnya = - (komplemen 1 dari 1101111)

BAB II

OPERASI DATA BINER

Pada bab yang lalu telah dijelaskan bahwa suatu informasi dapat dikodekan dalam bentuk biner yang hanya mempunyai 2 kemungkinan. Pada bab ini akan dibahas tentang hubungan variabel-variabel biner.

2.1. Operasi Logika

Suatu rangkaian elektronik yang mengoperasikan data biner disebut Sistem Digital Logika (Logic Digital System). Rangkaian-rangkaian dalam suatu sistem yang mengoperasikan logika-logika dasar disebut Logic Gate (Gerbang Logika). Ada 3 (tiga) tipe system logika yang dikenal antara lain :

1. Sistem Logika Kombinasional. 2. Sistem logika Sequential (berurutan). 3. Sistem Storage (Penyimpanan).

Suatu sistem logika dapat digambarkan dengan suatu blok yang mempunyai satu set input yang menerima data biner dan mempunyai satu jalur output atau lebih. Jika sistem itu adalah Kombinasional maka output datanta mempunyai fungsi logika langsung atau dengan kata lain output tidak mempengaruhi input.

Input I1 Z1

I2 Z2 Output

. .

In Z3

SISTEM LOGIKA

Gambar 4.1. Sistem Logika secara Umum.

Jika input diwakili dengan I dan outputnya adalah Z seperti terlihat pada gambar 4.1. maka :

Zt = f ( It)

Rangkaian penjumlah (adder) adalah suatu contoh dari rangkaian Kombinasional. Jika input mewakili 2 bilangan, misalnya 2 dan 3 maka keluaran yang diharapkan adalah 5 dengan kata lain outputnya akan 5 jika inputnya 2 dan 3.

Sebuah rangkaian sequential juga dapat digambarkan seperti gambar 4.1. yang mana mempunyai input dan output. Tapi ada satu hal yang membedakan antara Sequential dan Kombinasional, yaitu pada sequential outputnya tidak hanya tergantung pada inputnya tetapi juga tergantung pada input sebelumnya pada operasi waktu tertentu. Maka :

Zt = f ( I1, I2, …, It )

Dimana It adalah input data pada selang waktu t. Output dari rangkaian ini tergantung pada nilai input saat t dan semua input sebelumnya , oleh karena itu input yang diberikan pada selang waktu t tidak selalu mempunyai output yang sama.

Contoh :

Suatu rangkaian bilangan 1, 4, 2, 5, 2 merupakan contoh dari sistem sequential yang disalurkan sekali setiap selang waktu t. maka urutan output dapat dilihat pada tabel dibawah ini :

Tabel 4-1. Operasi Accumulator (Penjumlah) Waktu Input Output

1 1 1

2 4 5

3 2 7

4 5 12

5 2 14

Tipe ketiga adalah sistem storage (penyimpanan). Sistem ini pempunyai 2 fungsi yang berbeda. Ini dapat menahan suatu informasi dimana data itu dimasukkan dan

disimpan tanpa mengeluarkan apapun, atau dapat mengatur informasi dalam memory dengan mengeluarkan output tanpa membutuhkan input data.

Dalam memory ada beberapa lokasi dimana data dapat disimpan, dan yang mengatur lokasi ini disebut address (alamat). Ada input kontrol lain yang sangat penting untuk mengatur memory ke dalam mode Read (baca) atau mode Write (tulis). Address Data Out Data In MEMORY Control Read/ Write

Gambar 4-2. Sistem Memory

Tiga tipe dari sistem logika ini mempunyai hubungan yang unik. Sebuah rangkaian kombinasional dapat dikonversikan dalam sistem sequential dengan cara menambah feedback dari beberapa outputnya untuk menimbulkan internal input. Sedangkan rangkaian sequential sederhana mempunyai peralatan memory, maka dapat dikatakan bahwa sebuah rangkaian memory dapat dibentuk sebagai fungsi kombinasional.

2.2. LOGIKA DAN STATEMEN (PERNYATAAN)

Analisa dari sistem biner pertama kalinya dilakukan oleh seorang ahli matematika , George Boole (1815 – 1884) beberapa puluh tahun sebelum revolusi elektronik dan komputer. Teori Boole ini sangat relevan dengan operasi yang ditampilkan oleh data biner dalam sistem elektronik.

Contoh :

Marilah kita lihat pernyataan sederhana ini :

“ Hari ini akan turun salju jika temperaturnya rendah dan langit mendung

(berawan)”

disini ada 3 (tiga) variabel : Salju (sebagi Output), temperature rendah dan

Mendung (sebagai Input). Setiap kondisi ini hanya mempunyai 2 kemungkinan “Benar atau Salah” (Benar jika bersalju dan Salah jika tidak).

Keadaan cuaca ini dapat digambarkan dalam persamaan Boole dengan variabel S untuk Salju, R untuk Temperatue Rendah, dan M unutk mendung, maka :

S = R AND M

Fungsi logika antara 2 (dua) variabel input adalah AND (dan) dan symbol dari AND adalah ‘.’ dan persamaan diatas dapat dituliskan :

S = R . M

Persamaan ini menyatakan bahwa S itu benar jika dan hanya jika R benar dan M benar. Pernyataan ini mewakili suatu statemen “ akan terjadi Salju Jika temperatur rendah dan mendung”.

2.3. TRUTH TABLE (TABEL KEBENARAN)

Setiap persamaan boole mempunyai truth table yang berupa daftar nilai output untuk setiap kemungkinan kombinasi input.

- Ada 4 (empat) kemungkinan kombinasi input (R dan M) yaitu (salah, salah), (salah, benar), (Benar salah), dan (benar, banar).

- S akan benar jika R benar dan M benar.

Keadaan ini dapat digambarkan/dijelaskan dalam sebuah tabel kebenaran (Truth Tabel) seperti terlihat pada tabel dibawah ini :

Tabel. Untuk fungsi ‘AND’ (S = R . M)

Input Output Input Output

S M R R M S

Salah Salah Salah 0 0 0

Salah Benar Salah 0 1 0

Benar Salah Salah 1 0 0

Benar Benar Benar 1 1 1

a. Nilai Kebenaran b. Symbol dalam biner

2.4. ALJABAR BOOLEAN

Prinsip logika yang ditemukan George Boole ini dikembangkan lebih lanjut oleh Augusto De Morgan. Dan teori dari Boole ini biasa disebut Aljabar Boolean (Boolean Algebra).

Teori aljabar boolean ini terbagi menjadi 3 group : a. Operasi Logika Konstanta

b. Operasi Logika Satu Variable.

4.4.1. GERBANG LOGIKA DASAR (BASIC LOGIC GATES) A B F 0 0 1 1 0 1 0 1 0 0 0 1 A B F 0 0 1 1 0 1 0 1 0 1 1 1 A F 0 1 1 0 A B F 0 0 1 1 0 1 0 1 1 1 1 0 A B F 0 0 1 1 0 1 0 1 1 0 0 0 A B F 0 0 1 1 0 1 0 1 0 1 1 0 A B F 0 0 1 1 0 1 0 1 1 0 0 1

Name Symbol AljabaricFunction Truth Table

AND GATE F = A . B or F = A B OR GATE F = A + B A B F A F A F B NOT GATE F = A' = A NAND GATE B F = A . B A F B A F NOR GATE F = A + B B A F EX-OR GATE B A F EX-NOR GATE or F = A' B + A B' F = A + B F = A + B

2.4.2. Hukum-Hukum dalam Aljabar Boolean a. Operasi Logika OR satu Variabel

OR AND NOT X + 0 = X X . 0 = 0 X + 1 = 1 X . 1 = X (X’)’ =X X + X = X X . X = X X + X’ = 1 X . X’ = 0 b. Hukum Komutatif 1. X + Y = Y + X (Hukum Komutatif) 2. X . Y = Y . X (Hukum Komutatif) c. Hukum Asosiatif 1. X + (Y + Z) = (X + Y) + Z (Hukum Asosiatif) 2. X (Y.Z) = (X.Y) Z (Hukum Asosiatif) d. Hukum Distributif

1. X (Y + Z) = X Y + X Z (Hukum Distributif) 2. X + YZ = (X + Y)(X + Z) (Hukum Distributif) e. Teori De Morgan

1. (X + Y)’ = X’ Y’ (Teori De Morgan) 2. (X.Y)’ = X’ + Y’ (Teori De Morgan) f. Hukum Absorbsi

1. A + (A.B) = A (Hukum Absorbsi) 2. A (A + B) = A (Hukum Absorbsi)

g. Teori Penyusutan (Minimization)

1. AB + AB’ = A (Teori Penyusutan) 2. (A + B) (A + B’) = A (Teori Penyusutan) 3. A + A’. B = A + B (Teori Penyusutan) 4. A (A’ + B) = A . B (Teori Penyusutan)

Contoh – contoh penyederhanaan menggunakan aljabar Boolean. 1. X + X’ Y = (X + X’)(X + Y) = 1. (X + Y) = X + Y

2. X(X’ + Y) = XX’ + XY = 0 + XY = XY

3. X’Y’Z + X’YZ + XY’ = X’Z (Y’ + Y) + XY’ = X’Z + XY’ 4. XY + X’Z + YZ = XY + X’Z + YZ(X + X’) = XY + X’Z + XYZ + X’YZ = XY(1 + Z) + X’Z(1 + Y) = XY + X’Z 5. (A + B + C)’ = (A + X)’ = A’X’ = A’ . (B + C)’ = A’ . (B’. C’) = A’B’C’

2.4.3. Minterm dan Maxterm

Sebuah variabel biner dapat ditampilkan dalam bentuk normal (x) atau dalam bentuk komplemen (x’). Ini dapat kita lihat jika dua variabel biner x dan y dikombinasikan menggunakan operasi ‘AND’. Karena setiap variabel dapat diekspresikan dalam bentuk tertehtu, maka terdapat 4 kombinasi input : x’y’, x’y, xy’, dan xy. Setiap kemungkinan tersebut mewakili satu kombinasi input yang disebut Minterm atau Standart Product. Hal ini dapat diperjelas bahwa n variabel mewakili 2n kombinasi input (Minterm).

Begitu juga, n variabel yang diekspresikan dalam operasi ‘OR’ dimana kombinasi inputnya biasa disebut Maxterm atau Standart Sum. Hal diatas dapat digambarkan pada tabel dibawah ini.

Tabel Minterm dan Maxterm untuk 3 (tiga) Variabel Input.

Minterm Maxterm

x y z Term Tanda Term Tanda

0 0 0 x’y’z’ m0 x + y + z M0 0 0 1 x’y’z m1 x + y + z’ M1 0 1 0 x’yz’ m2 x + y’ + z M2 0 1 1 x’yz m3 x + y’ + z’ M3 1 0 0 xy’z’ m4 x’ + y + z M4 1 0 1 xy’z m5 x’ + y + z’ M5 1 1 0 xyz’ m6 x’ + y’ + z M6 1 1 1 xyz m7 x’ + y’ + z’ M7

Penulisan persamaan aljabar pada bentuk normal (x) dilakukan berdasarkan logika ‘1’ pada fungsi yang ada.

Sebagai contoh fungsi f1 dan f2 pada tabel dibawah ini.

x y z f1 f2 0 0 0 0 0 0 0 1 1 0 0 1 0 0 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1

f1 = x’y’z + xy’z’ + xyz = m1 + m4 + m7 (Minterm/Sum Of Product)

Komplemen dari fungsi diatas diambil berdasarkan logika ‘0’, komplemen dari f1 dapat dibaca sebagi berikut :

f1’ = x’y’z’ + x’yz’ + x’yz + xy’z + xyz’ = m0 + m2 + m3 + m5 + m6

dan komplemen dari f1’ adalah

f1 = (x + y + z)(x +y’ + z’)(x + y’ + z’)(x’ + y + z’)(x’ + y’ + z) = M0 . M2 . M3 . M5 . M6 (Maxterm/Product Of Sum) Demikian juga untuk f2 :

f2 = x’yz + xy’z + xyz’ + xyz = m3 + m5 + m6 + m7 f2’ = m0 + m1 + m2 + m4

f2 = M0 . M1 . M2 . M4

Pada prinsipnya, minterm diekspresikan dalam bentuk Sum Of Product (SOP), dan Maxterm diekspresikan dalam bentuk Product Of Sum POS).

2.5. KARNOUGH MAP

Pada bab yang lalu telah dibahas tentang aljabar boolean yang mana dapat digunakan untuk menyederhanakan suatu rangkaian digital.

Akan tetapi jika rangkaian itu mencapai tingkat kesulitan (complexity) tertentu, maka persamaan aljabar yang didapat akan sangat rumit, dan mungkin akan timbul berbagai macam bentuk persamaan. Karena dengan metode boolean itu tidak mempunyai prosedur/step-step yang khusus dalam proses manipulasi.

Metode map (pemetaan) menyediakan/mempunyai prosedur sederhana dan langsung untuk menyederhanakan fungsi boolean.

Metode ini pertama kalinya diciptakan oleh Veitch dan dikembangkan lebih lanjut oleh Karnough, oleh karena itu metode ini biasa disebut Diagram Veitch atau

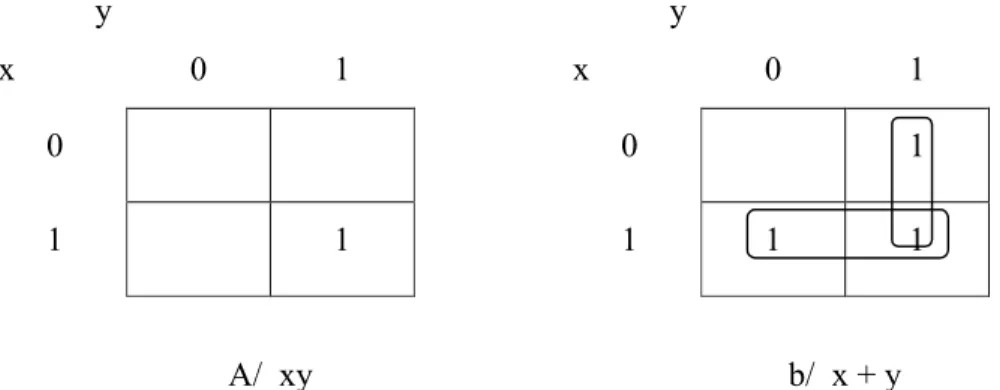

Map ini adalah sebuah diagram yang terdiri dari beberapa kotak dimana setiap kotaknya mewakili 1 (satu) kombinasi input, dimana map ini menunjukkan bahwa semua kemungkinan yang timbul dapat diexpresikan dalam bentuk yang standar. Kita dapat membuktikan beberapa alternatif dari persamaan yang paling sederhana. Hasil akhir dari pemetaan adalah persamaan ajlabar yang paling sederhana dalam bentuk penjumlahan dari suatu perkalian (Sum Of Product). 2.5.1. MAP BERVARIABEL DUA DAN TIGA

Gambar 2.5-1 menunjukkan suatu contoh map dengan 2 (dua) variabel input. Ada 4 (empat) kombinasi input untuk 2 (dua) variabel input, maka map itu berisi 4 (empat) kotak.

Satu untuk setiap kombinasi input . Gambar 5-1 (b) digunakan untuk menunjukkan hubungan antara kotak-kotak itu dengan dua variabel input.

y

x 0 1

m0 m1 0 x’ y’ x’ y

m2 m4 1 x y’ x y

Gambar 2.5-1. Map dengan 2 Variabel Input

Penggunaan dari map ini dapat digambarkan dalam suatu contoh berikut. Contoh 1 :

Fungsi xy (seperti ditunjukkan gambar 5-2 (a) adalah sama dengan m3 maka ‘1’ dituliskan pada kotak m3.

F(xy) = (m3) = xy

Sama halnya dengan fungsi x + y (gambar 5-2 b) ada 3 kotak dengan tanda ‘1’ F = (x + y) = x’y + xy’ + xy = m1 + m2 + m3

Ketiga kotak tersebut dapat ditemtukan dari perpotongan variabel x pada baris ke dua dan variabel y pada kolom 2 dimana kotak tsb memiliki variabel x atau y.

y y

x 0 1 x 0 1

0 0 1

1 1 1 1 1

A/ xy b/ x + y

Gambar 2.5-2. Penulisan Fungsi ke dalam Map.

Prosedure Pemetaan (Mapping)

1. Ubahlah Persamaan aljabar yang akan disederhanakan kedalam bentuk minterm berdasarkan output yang berlogika ‘1’.

2. Lakukan transfer data ke dalam tabel pemetaan sesuai dengan mintermnya. 3. Lakukan pemetaan dengan cara pengelompokan data yang berlogika ‘1’ dan

diberi batas kotak (pengkotakan/pemetaan), dengan syarat : a. Didalam satu kotak tidak boleh mengandung logika ‘0’. b. Tidak boleh dilakukan pemetaan secara diagonal.

c. Jumlah logika ‘1’ dalam satu kotak yang diperbolehkan adalah : 1, 2, 4, 8, 16, … (pemangkatan dari 2).

4. Pembacaan hasil pemetaan, setiap koyak yang muncul menghasilkan 1 (satu) product.

5. Penulisan hasil penyederhanaan, dengan cara menjumlahkan product-product hasil pemetaan, sehingga hasil pemetaan merupakan persamaan yang paling sederhana dalam bentuk Sum Of Product.

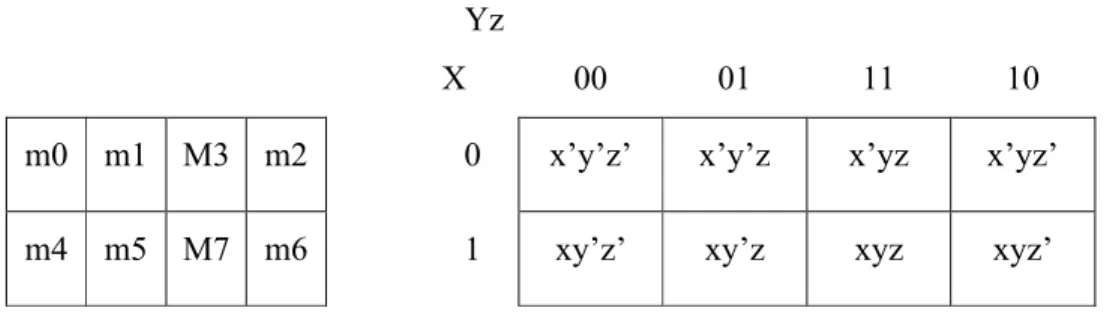

Pada gambar 2.5-3 menunjukkan sebuah map dengan 3 (tiga) variabel input. Untuk 3 (tiga) variabel input mempunyai 8 kombinasi input (23 = 8), maka map

Dalam hal ini input kombinasi tidak disusun berdasarkan urutannya, tetapi disusun seperti terlihat pada gambar 5-3.

Yz

X 00 01 11 10

m0 m1 M3 m2 0 x’y’z’ x’y’z x’yz x’yz’

m4 m5 M7 m6 1 xy’z’ xy’z xyz xyz’

Gambar 2.5-3. Map dengan tiga variabel Input Penggunaan dari map ini dapat dijelaskan dalam suatu contoh berikut. Contoh 2 :

Hanya m5 dan m7 yang mempunyai logika ‘1’, maka dapat dituliskan/ disederhanakan dengan cara berikut :

yz

x 00 01 11 10

0

1 1 1

xz F (x,y) = m5 + m7 = xy’z + xyz = xz

Contoh 3 :

Sederhanakan fungsi boolean dibawah ini : F = x’yz + x’yz’ + xy’z’ + xy’z

Langkah pertama ‘1’ dituliskan pada setiap kotak yang diperlukan untuk mewakili fungsi tersebut (seperti gambar dibawah ini )

yz

x 00 01 11 10

0 1 1 x’y

1 1 1 xy’

Maka fungsi diatas dapat langsung kita sederhanakan dengan hasil sebagai berikut:

F = x’y + xy’ Contoh 4 :

Sederhanakan F = x’yz + xy’z’ + xyz + xyz’ Penyelesaian :

yz

x 00 01 11 10

0 1 yz

1 1 1 1 xz

Maka fungsi hasil :

F = yz + xz Contoh 5 :

Sederhanakan fungsi boolean ini

F = A’ C + A’ B + AB’ C + BC

Jika satu persamaan memiliki kurang dari 3 (tiga) variabel input maka ini mempunyai ‘1’ lebih dari satu kotak.

Untuk mencari kotak yang berhubungan dengan A’ C, kita harus memperhitungkan satu persatu A’ (baris pertama) dan C dua kolom tengah), maka A’ C ada pada posisi kotak 001 dan 011 maka pemetaan dapat diperlihatkan pada gambar berikut :

BC

A 00 01 11 10

0 1 1 1 A’ B

1 1 1 C

Maka hasil penyederhanaannya adalah : F = A’ B + C Contoh 6 : F (x,y,z) = ( 0, 2, 4, 5, 6 ) Yz X 00 01 11 10 0 1 1 z 1 1 1 1 xy’ F (x,y,z) = ( 0, 2, 4, 5, 6 ) = xy’ + z’

2.5.2. MAP DENGAN EMPAT VARIABEL INPUT

Map untuk fung boolean dengan 4 (empat) variabel input dapat ditunjukkan pada gambar 2.5-4. Pada gambar (a) menunjukkan daftar dari 16 kombinasi input, dan gambar (b) menunjukkan hubungan dari setiap kombinasi input.

yz

wx 00 01 11 10

00 w’x’y’z’ w’x’y’z w’x’yz w’x’yz’ 01 w’xy’z’ w’xy’z w’xyz w’xyz’ 11 wxy’z’ wxy’z wxyz wxyz’ 10 wx’y’z’ wx’y’z wx’yz wx’yz’

Gambar 2.5-4. Map dengan 4 Variabel Input Contoh 7 :

Sederhanakan fungsi boolean dibawah ini :

F (w,x,y,z) = ( 0, 1, 2, 4, 5, 6, 8, 9, 12, 13, 14 ) Penyelesaian : yz wx 00 01 11 10 00 1 1 1 w’z’ 01 1 1 1 11 1 1 1 xz’ 10 1 1 y’ F (w,x,y,z) = ( 0, 1, 2, 4, 5, 6, 8, 9, 12, 13, 14 ) = y’ + w’z’ + xz’

Contoh 8 :

Sederhanakan fungsi boolean dibawah ini :

F = A’ B’ C’ + B’ C D’ + A’ B C D’ + A B’ C’ Penyelesaian : CD AB 00 01 11 10 00 1 1 1 A’ C D’ 01 1 11 10 1 1 1 B’ D’ B’ C’ F = B’ D’ + B’ C’ + A’ C D’ Tugas :

Desain rangkaian perubah BCD ke 7-Segment Display - Jelaskan Kerja dan rangkaian dari 7-Segment Display

- Gambarkan blok diagram dari system ini, identifikasi Input dan Outputnya. - Buatlah tabel kebenaran dari rangkaian perubah tersebut.

- Lakukan penyederhanaan dari tabel kebenaran diatas. - Tuliskan hasil penyederhanaan dari masing-masing output. - Gambar rangkaian perubah tersebut.

BAB III

LOGIKA KOMBINASIONAL

Rangkaian logika untuk suatu sistem digital mungkin merupakan rangkaian kombinasional atau sequential. Rangkaian kombinasional terdiri dari beberapa gate (gerbang logika) yang mana outputnya ditentukan langsung oleh kombinasi input saat itu tanpa memperhitungkan input sebelumnya. Pada bab ini akan kita bahas contoh rangkaian kombinasi sederhana yaitu Adder (penjumlah).

3.1. PROSEDUR DESAIN

Sebelum kita membahas pokok permasalahannya, perlu kita perjelas dahulu bahwa desain dari rangkaian kombinasional dimulai dari layout permasalahan dan diakhiri dengan rangkaian logika.

Prosedur ini melibatkan step-step sebagai berikut : 1. Pemahaman permasalahan.

2. Penentuan jumlah variabel Input dan variabel output yang dibutuhkan. 3. Penandaan (symbol) Input dan output.

4. Truth table (tabel kebenaran) yang menyatakan hubungan antara input dan output yang dibutuhkan.

5. Penyederhanaan dengan fungsi boolen untuk setiap output yang ada. 6. Penulisan hasil penyederhanaan ke dalam persamaan aljabar.

7. Penggambaran rangkaian logika.

Truth table untuk rangkaian kombinasional terdiri dari kolom input. Jumlah dari

kombinasi input ditentukan oleh 2n dimana n adalah jumlah variabel input. Harga

biner dari output ditentukan dari analisa pernyataan masalah. Dan output mungkin berharga ‘0’ atau ‘1’ untuk setiap kombinasi input yang valid. Tetapi spesifikasinya mungkin menunjukkan bahwa beberapa kombinasi input yang tidak

mungkin terjadi. Kombinasi ini disebut kondisi tak menentu (Don’t Care Condition).

Fungsi output yang ditunjukkan dalam truth table memberikan definisi yang pasti dari rangkaian kombinasi. Tapi kadang-kadang seorang desainer harus menggunakan intuisi dan pengalamannya untuk menginterpretasikan masalah yang biasanya dinyatakan dalam bentuk kalimat. Jika interpretasi itu salah maka rangkaian logika yang dihasilkan akan salah. Persamaan fungsi boolean yang dihasilkan dari truth table disederhanakan menggunakan metode-metode yang tersedia seperti manipulasi aljabar Boolean, metode map dll.

Pada prakteknya desain ini harus memperhatikan ketentuan-ketentuan sbb : 1. Jumlah gate minimum.

2. Jumlah input minimum.

3. Waktu penundaan signal (propagation delay) melalui rangkaian yang minim. 4. Jumlah interkoneksi yang minim.

3.2. KONVERSI KODE

Sebagai contoh permasalahan disini dapat diterapkan sistem pnyederhanaan yang dimaksud di atas. Suatu ragkaian konversi harus diselipkan diantara dua system yang menggunakan kode berbeda tetapi mempunyai informasi yang sama. Maka konversi kode adalah suatu rangkaian yang membuat dua sistem kompatibel meskipun kedua sistem itu menggunakan kode biner yang berbeda.

Untuk konversi dari kode biner A ke kode biner B, jalur input harus mensupply kombinasi bit dari elemen-elemen seperti ketentuan kode A dan jalur output harus membangkitkan kombinasi bit yang sesuai dengan kode B.

Kode-kode biner untuk digit desimal itu sendiri memiliki bermacam-macam kemungkinan kombinasi . Disini dapat ditunjukkan beberapa kemungkinan kombinasi seperti yang terlihat pada tabel dibawah ini :

Tabel 3.1. Kode biner untuk digit desimal.

Digit Desimal BCD (8 4 2 1) Excess -3

0 0 0 0 0 0 0 1 1 1 0 0 0 1 0 1 0 0 2 0 0 1 0 0 1 0 1 3 0 0 1 1 0 1 1 0 4 0 1 0 0 0 1 1 1 5 0 1 0 1 1 0 0 0 6 0 1 1 0 1 0 0 1 7 0 1 1 1 1 0 1 0 8 1 0 0 0 1 0 1 1 9 1 0 0 1 1 1 0 0

BCD (8 4 2 1) merupakan konversi langsung dari sedimal ke kode biner. Kode biner yang pernah digunakan dalam beberapa komputer generasi awal adalah EXCESS-3 dimana kode ini dibentuk sesuai dengan harga BCD setelah ditambah dengan 3.

Contoh :

Desimal 3 --- 2 + 3 = 5 Kode Excess-3 adalah 0 1 0 1

Prosedur desain untuk konversi kode dapat digambarkan dengan mengambil contoh Konversi BCD ke kode Excess-3. Kombinasi bit untuk BCD dan kode Excess-3 dapat dilihat pada tabel 6.1.

Karena kedua kode tersebut menggunakan 4 bit untuk mewakili digit desimal, maka terdapat 4 variabel input dan 4 variabel output.

Keempat variabel input disimbolkan A B C D dan outputnya disimbolkan w x y z. Dan didapatkan tabel kebenaran (truth table) seperti pada tabel 6.2. dibawah ini.

Tabel 3.2. Truth Table untuk contoh Konversi Kode

DEC Input BCD Output Kode Excess-3

A B C D W X Y Z 0 0 0 0 0 0 0 1 1 1 0 0 0 1 0 1 0 0 2 0 0 1 0 0 1 0 1 3 0 0 1 1 0 1 1 0 4 0 1 0 0 0 1 1 1 5 0 1 0 1 1 0 0 0 6 0 1 1 0 1 0 0 1 7 0 1 1 1 1 0 1 0 8 1 0 0 0 1 0 1 1 9 1 0 0 1 1 1 0 0 10 1 0 1 0 X X X X 11 1 0 1 1 X X X X 12 1 1 0 0 X X X X 13 1 1 0 1 X X X X 14 1 1 1 0 X X X X

X = don’t care condition

Jika kita analisa, bila terdapat 4 variabel input maka akan terdapat 16 kombinasi input tetapi pada tabel 3.1. hanya ada 10. Maka 6 kombinasi input yang tidak tercantum pada tabel tersebut disebut kondisi tak menentu atau don’t care combination. Seperti terlahat pada tabel 3.2.

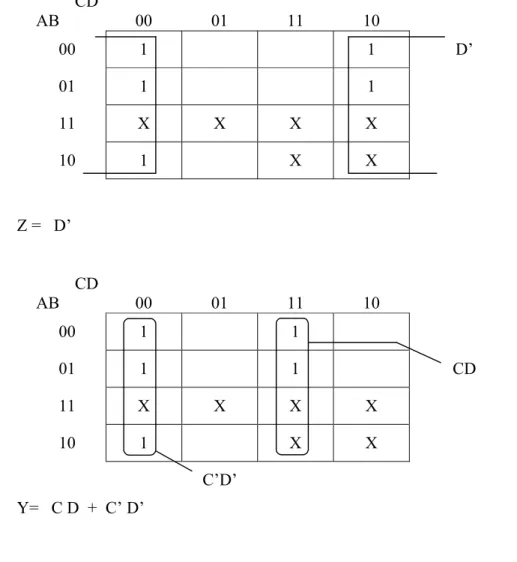

Tabel siatas dimanipulasi dengan menggunakan karnough map untuk mendapatkan persamaan Sum Of Product yang paling sederhana.

Untuk mendapatkan output yang dikehendaki, maka kita harus memperoleh 4 fungsi boolean sesuai dengan jumlah variabel output. Hal ini dapat dijelaskan seperti dibawah ini.

CD AB 00 01 11 10 00 1 1 D’ 01 1 1 11 X X X X 10 1 X X Z = D’ CD AB 00 01 11 10 00 1 1 01 1 1 CD 11 X X X X 10 1 X X C’D’ Y= C D + C’ D’

CD AB 00 01 11 10 00 1 1 1 B’C 01 1 11 X X X X 10 1 X X BC’D’ B’D X = B’C + B’D + BC’D’ CD AB 00 01 11 10 00 BD 01 1 1 1 11 X X X X BC 10 1 1 X X A W = A + BC + BD

Hasil diatas dapat dimanipulasi dengan metode aljabar boolean :

Z = D’ Y = CD + C’D’ = CD + (C + D)’ X = B’C + B’D + BC’D’ = B’(C + D) + BC’D’ = B’(C + D) + B(C + D)’ W = A + BC + BD

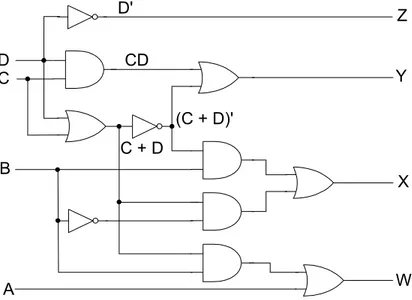

Rangkaian logika dari persamaan dapat digambarkan seperti gambar 6.1.

Didalamnya dapat kita lihat bahwa gerbang OR yang memiliki output C + D telah digunakan secara parsial oleh 3 output.

Gambar 3.1. Rangkaian Logika untuk Konverter BCD ke Excess-3

D C B A Z Y X W D' CD C + D (C + D)'

BAB IV

RANGKAIAN SEQUENSIAL

4.1. PENDAHULUAN

Pada rangkaian digital kombinasional yang telah dibahas pada bab terdahulu, dikatakan bahwa output rangkaian kombinasional adalah sepenuhnya tergantung dari input yang ada untuk segala keadaan.

Meskipun setiap rangkaian digital mempunyai rangkaian kombinasional, tetapi sistem-sistem yang digunakan pada prakteknya juga memiliki elemen memory yang mana membutuhkan sistem yang disebut logika sequensial.

Gambar 4.1.1 Blok Diagram Rangkaian Sequensial

Blok diagram untuk rangkain sequensial dapat dilihat pada gambar diatas. Sistem ini terdiri dari rangkaian kombinasionaldengan elemen memory yang membentuk jalur feed-back (umpan balik).

Elemen memory adalah peralatan yang mampu menyimpan informasi biner didalamnya. Informasi biner yang disimpan dalam elemen memory pada suatu waktu disebut State (keadaan) dari rangkaian sequensial.

Rangkaian sequensial menerima informasi biner dari input eksternal. Input biner ini digabungkan dengan state (keadaan) ekemen memory saat itu, akan menentukan nilai output biner. Keadaan itu juga menentukan kondisi untuk

Rangkaian

Kombinasional

Elemen

Memory

Input Eksternal Output

menunjukkan bahwa output eksternal dari rangkaian sequensial bukan hanya merupakan fungsi dari input eksternal tetapi juga state (keadaan) elemen memory saat itu. Rangkaian sequensial mengikuti urutan dari input, output dan state internal.

Pada prakteknya, sistem digital sequensial menggunakan pulsa atau clock (pemicu) untuk bekerja, yang mana pulsa atau clock ini merupakan level tegangan yang dikonversikan dalam signal biner. Dimana amplitudo pulsa mewakili logika ‘1’ dan tegangan nol (tanpa pulsa) mewakili logika ‘0’. Biasanya clock ini bekerja secara sinkron dengan pulse train (rentetan pulsa) dengan periode T seperti ditunjukkan pada gambar dibawah ini.

Gambar 4.1.2. Keluaran Osilator master untuk pulse train.

Lebar pulsa tp dimisalkan kecil dibandingkan dengan T. Perpindahan satu keadaan ke keadaan lain dari sistem hanya terjadi dengan adanya pulsa atau clock. Qn adalah keadaan output saat itu (sebelum adanya clock) dan Qn+1 keadaan output setelah adanya clock.

Adapun perpindahan keadaan tegangan pada pulsa akan digunakan oleh sistem sequensial untuk mentrigger (memicu) untuk bekerja, gambaran detail dari perpindahan ini dapat dilihat pada diagram dibawah ini.

Amplitudo 0 0 T 2T (n - 1)T nT (n + 1)T tp tp << T waktu

bit n bit n+1waktu

Gambar 4.1.3. Diagram sebuah clock

Diagram diatas yang menunjukkan posisi perpindahan level tegangan terbagi menjadi 3 (tiga) keadaan yang menunjukkan jenis-jenis pentriggeran yang dapat dipakai :

1. Pentriggeran Level (Level Triggering)

: Sistem pentriggeran yang didasarkan pada level tegangan , jika level tegangan pada +5 volt maka clock akan bekerja mentrigger sistem, jika level tegangan pada 0 volt maka clock tidak bekerja. 2. Pentriggeran Tebing Naik

(Positive Edge Triggering)

: Sistem pentriggeran yang didasarkan pada perubahan dari logika ‘0’ ke logika ‘1’, atau pada tebing naik.

3. Pentriggeran Tebing Turun (Negative Edge Triggering)

: Sistem pentriggeran yang didasarkan pada perubahan dari logika ‘1’ ke logika ‘0’, atau pada tebing turun.

Contoh-contoh rangkaian sequensial adalah rangkaian flip-flop, Shift Register, Counter, RAM dlsb. LEVEL PO SIT IVE ED GE (TE BIN G N AIK ) NEG AT IV E E D G E (TE B IN G TU R U N ) tr tf tr = rise Time tf = falling time +5 Volt Logika '1' 0 volt (GND) Logika '0'

4.2.

FLIP – FLOP (FF)

Elemen memory yang digunakan dalam rangkaian sequensial disebut Flip-flop. Rangkaian ini merupakan sel-sel biner yang mampu menyimpan informasi satu-bit. Sebuah flip-flop mempunyai dua output, satu untuk harga normal dan yang lain untuk harga kebalikan (komplemen) dari informasi yang disimpan didalamnya. Informasi biner dapat dimasukkan dalam flip-flop dengan berbagai cara, yang menyebabkan timbulnya beberapa tipe flip-flop.

Gambar 4.2.1. Blok Output Flip-flop

4.2.1 S-R FLIP-FLOP (Set – Reset)

Rangkaian flip-flop dapat dibentuk dari 2 (dua) NAND Gate atau 2 (dua) NOR Gate. Dan rangkaian tersebut adalah dasar dari flip-flop yang dapat digunakan untuk membentuk rangkaian yang lebih compleks. Hubungan silang dari output satu gerbang ke input gerbang yang lain merupakan jalur feed-back. Setiap flip-flop ini mempunyai 2 (dua) output (Q dan Q’) dan dua input Set (S) dan Reset (R). Flip-flop tipe ini biasa disebut flip-flop S-R sambungan langsung atau (Latch).

Q

Q

flip-flopGambar 4.2.2. Rangkaian Flip-flop S-R.

Truth table (tabel kebenaran) dari rangkaian diatas dapat ditunjukkan pada tabel dibawah ini. S R Q Q’ KONDISI 1 0 0 1 1 1 0 1 Setelah S=1, R= 0 0 1 1 0 1 1 1 0 Setelah S= 0, R = 1

0 0 1 1 Undeterminate (tak terdefinisi)

Rangkaian S-R flip-flop ini akan menunjukkan kondisi output flip-flop yang tetap jika kedua inputnya berlogika ‘1’. Pada aplikasinya, input Set (S) diberikan logika ‘0’ menyebabkan output Q menjadi logika ‘1’ dan Q’ akan berlogika ‘0’, maka akan membuat flip-flop ini pada keadaan SET.

Setelah input set kembali ke logika ‘1’ dan input Reset ( R ) berlogika ‘0’ menyebabkan perubahan ke keadaan clear (Reset). Jika kedua inputnya diberikan logika ‘0’ maka kedua outputnya menjadi berlogika ‘1’ dan kondisi ini disebut kondisi tak terdefinisi (Undeterminate), keadaan ini harus dihindari untuk dapat

S

R

Q

Q

beroperasi secara normal. Maka rangkain ini diklasifikasikan sebagai rangkaian Sequensial Asinkron.

4.2.3. FLIP-FLOP S-R dengan CLOCK

Dengan menambahkan beberapa gerbang ke input rangkaian dasar (S-R Flip-flop), flip-flop akan memberikan respon terhadap level input saat adanya pulsa clock. Flip-flop S-r dengan clock, seperti terlahat pada gambar 9.3.1. terdiri dari flip-flop dasar NAND Gate dan ditambah dengan 2 (dua) NAND Gate.

Gambar 4.2.3. Rangkaian Flip-flop S-R dengan Clock

Sebelum adanya clock, output dari dua NAND gate terdekat dengan input adalah berlogika ‘1’. Apapun keadaan input S-R nya, saat seperti ini flip-flop dalam keadaan tidak bekerja atau disable.

Saat diberikan clock, flip-flop akan bekerja , output A dan B serta output Q dan Q’ tergantung dari input S-r. Operasi dari rangkaian dapat dilihat pada tabel kebenaran, dan hal ini dapat dicek perbaris menggunakan rangkaian pada gambar 4.2.3.

Waktu kondisi input S = R = berlogika ‘1’ maka Q = Q’ = 1 , hal ini menyimpang dari ketentuan bahwa Q’ merupakan komplemen dari Q. maka keadaan ini disebut keadaan tak terdefinisi (Undeterminate).

S

R

Clk

Q

Q

Q

Q

S

Clk

R

A BTabel 4.2.1. Truth Table Flip-flop S-R dengan Clock

INPUT Sebelum Clock Setelah Clock

S R Qt Q’t Q t+1 Q’ t+1 Kondisi 0 0 0 1 0 1 Tidak berubah 0 0 1 0 1 0 0 1 0 1 0 1 Reset 0 1 1 0 0 1 Q = 0, Q’ = 1 1 0 0 1 1 0 Set 1 0 1 0 1 0 Q = 1, Q’ = 0 1 1 0 1 1 1 Tak terdefinisi 1 1 1 0 1 1 (Undeterminate)

IC (Integrated Circuit) untuk flip-flop S-R ini jarang dipakai karena masih terdapat kondisi tak terdefinisi saat S = R = ‘1’, sedangkan ada tipe-tipe flip-flop lain yang lebih handal untuk mengerjakan sistem yang sama.

4.2.4. D-TYPE FLIP-FLOP ( Data Transfer )

D-Type Flip-flop atau flip-flop tipe-D ini merupakan modifikasi dari flip-flop S-R dengan Clock yang hanya mempunyai 1 (satu) input D. Modifikasi itu dilakukan dengan menambahkan Not Gate yang dihubungkan dengan kedua (S dan R) pada flip-flop S-R, sehingga R merupakan komplemen dari S. Maka operasi dari tipe-D

Gambar 4.2.4. Rangkaian Flip-flop Tipe-D

Setelah input clock (Clk) berubah dari logika ‘0’ ke logika ‘1’ , bit biner data pada input D dipindahkan ke output Q, maka output Q setelah clock akan sama dengan input D. Oleh karena itu flip-flop tipe-D disebut juga Data transfer.

Tabel 4.2.2. Tabel Kebenaran D-Flip-flop

Input Sebelum Clock Setelah Clock

D Qt Q’t Q t+1 Q’ t+1 0 0 1 0 1 0 1 0 0 1 1 0 1 1 0 1 1 0 1 0

Q

Q

S

Clk

R

Clk

D

Q

Q

D

Clk

4.2.5. J-K FLIP-FLOP

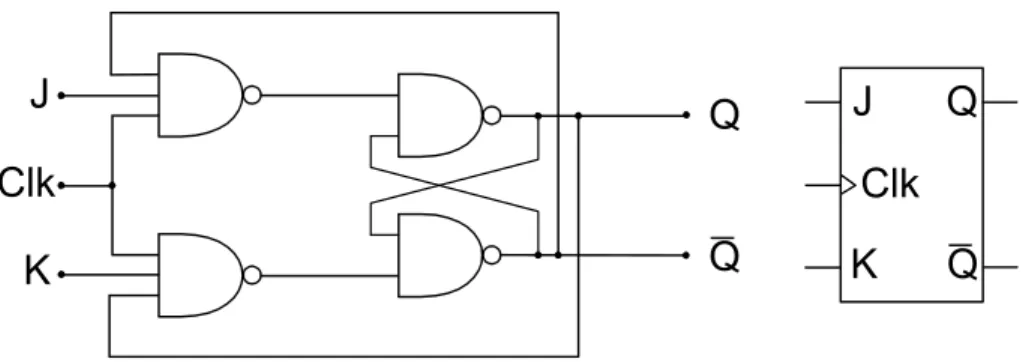

J-K flip-flop merupakan versi lain dari modifiksi flip-flop S-R. Flip-flop ini mempunyai daya guna yang tinggi, karena dapat menghindari kondisi undeterminate.

Flip-flop ini mempunyai 2 input yang disebut J dan K, dan data set hubungan feedback yaitu output komplemen Q’ dikombinasikan dengan input J dan clock melalui gerbang NAND, sedangkan output Q dikombinasikan dengan terminal K dan clockmelalui gerbang NAND juga.

Gambar 4.2.5. Rangkaian J-K Flip-flop

Q

Q

J

Clk

K

J

K

Clk

Q

Q

Tabel 4.2.3.. Truth Table J-K flip-flop

Sebelum Clock Setelah Clock

J K Qt t Qt+1 t+1 Keterangan 0 0 0 1 0 1 0 0 1 0 1 0 Tetap 0 1 0 1 0 1 0 1 1 0 0 1 Reset 1 0 0 1 1 0 1 0 1 0 1 0 Set 1 1 0 1 1 0 1 1 1 0 0 1 Toggle

BAB V

RANGKAIAN KOMBINASIONAL DENGAN

MSI (MEDIUM SCALE INTEGRATION) DAN

LSI (LARGE SCALE INTEGRATION)

Komponen yang digunakan untuk membentuk sistem digital dibuat dalam paket-paket IC (Integrated Circuit) . Rangkaian SSI (Small Scale Integration) berisi hanya beberapa gate atau flip-flop dalam satu paket. MSI (Medium Scale Integration) adalah berupa suatu peralatan yang mempunyai fungsi khusus (specific), contoh : decoder, multiplexer, ROM, dll. Dan LSI (Large Scale Integration) berupa peralatan modul komputer mikro yang cukup lengkap.

Ada beberapa rangkaian MSI dan LSI yang dapat diaplikasikan langsung ke desain dan pengembangan dari rangkaian kombinasional. Teknik-teknik ini menggunakan prinsip-prinsip umum dari decoder, multiplexer, Read Only Memory (ROM), programmable logic array (PLA). Keempat IC tersebut memiliki aplikasi yang sangat luas.

5.1. PENJUMLAH (ADDER)

Digital komputer menampilkan bermacam-macam pemrosesan informasi. Fungsi dasar yang ada diantaranya adalah macam-macam operasi aritmatika. Operasi aritmatika yang paling dasar adalah penjumlahan dua digit biner.

Penjumlahan sederhana terdiri dari 4 kemungkinan :

0 + 0 = 0 --- 1 digit

0 + 1 = 1 --- 1 digit

1 + 0 = 1 --- 1 digit

Rangakaian kombinasi yang menampilkan penjumlahan dari 2 bit disebut

penjumlah setengah (Half Adder). Dan yang menampilkan penjumlahan 3 bit disebut penjumlah penuh (Full Adder).

Kenyataannya full adder dapat dibentuk dari 2 half adder dan 1 OR Gate.

5.1.1. HALF ADDER

Dari keterangan global tentang half adder diatas, kita dapat melihat bahwa rangkaian ini membutuhkan 2 input biner dan 2 output biner. Variabel input terdiri dari bit yang akan dijumlahkan (AUGEND), dan bit yang penjumlah (ADDEN). Dan variabel output terdiri dari hasil penjumlahan / SUM (S) dan carry (C).

Jika 2 bit input kita beri simbol x dan y, sedangkan outputnya adalah S (hasil penjumlahan) dan C (carry). Kemudian kita buat truth table seperti dibawah ini :

x y C S

0 0 0 0

0 1 0 1

1 0 0 1

1 1 1 0

Persamaan fungsi boolean untuk 2 output dapat ditentukan daru truth table : S = x’y + xy’ = x y

Dan rangkaian logikanya dapat ditunjukkan pada diagram dibawah ini :

Gambar 5.1.1. Rangkaian Half Adder Dan disimbolkan :

Gambar 5.1.2. Simbol Half Adder

5.1.2. FULL ADDER

Full Adder adalah suatu rangkaian kombinasi yang membentuk penjumlahan aritmatik dari 3 bit input. Ini terdiri dari 3 Input dan 2 Output. Kedua outputnya disimbolkan dengan S untuk hasil penjumlahan (Sum) dan C untuk Carry.

x

y

S

C

H A x y C SMaka truth table untuk full adder adalah sebagai berikut : x y Z C S 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1

Hubungan input output dari rangkaian full adder dapat diekspresikan dalam 2 fungsi boolean (satu untuk setiap fungsi membutuhkan metode map untuk penyederhanaan). Untuk Output S = yz x 00 01 11 10 0 1 1 x’y 1 1 1 xy’

S = xy’z + x’yz’ + xy’z’ + xyz

Untuk Output C = yz x 00 01 11 10 0 1 yz 1 1 1 1 xy xz C = xy + xz + yz

Dari hasil penyederhanaan dengan menggunakan mapping ini yang berupa persamaan dalam bentuk Sum Of Product (SOP) sudah tidak dapat disederhanakan lagi, hal ini menyebabkan jumlah gerbang yang digunakan menjadi relatif banyak sehingga kurang effisien.

Bentuk konfigurasi yang lain dari full adder dapat dikembangkan dengan pendekatan prosedur matematis (penjumlahan 3 buah bilangan 1 bit), sehingga didapatkan full adder dapat dibentuk dari 2 (dua) half Adder dan 1 (satu) OR gate seperti gambar dibawah ini.

Gambar. 5.1.3. Rangkaian Full Adder

Sehingga didapat persamaan dari rangkaian (gambar 5.1.3) full adder adalah sebagai berikut :

S = z ( x y )

C = z(xy’ + x’y) + xy

Dan disimbolkan seperti gambar dibawah ini : x y S z C F A x y S Cout Cin

Persamaan yang dihasilkan dari 2 pendekatan tersebut yaitu dengan mapping dan prosedur matematis adalah sama, hal ini dapat dibuktikan dibawah ini :

Hasil Penjumlahan S :

S = z (x y)

= z’ ( x’y + xy’ ) + z ( x’y + xy’) = z’ ( x’y + xy’ ) + z [ (x’y)’ . (xy’)’ ] = z’ ( x’y + xy’ ) + z [ (x + y’) . (x’ + y) ] = z’ ( x’y + xy’ ) + z ( xx’ + xy + x’y’ + yy’ ) = z’ ( x’y + xy’ ) + z ( xy + x’y’ )

= x’yz’ + xy’z’ + x’y’ z + xyz dan Output Carry ( C ) :

C = z ( x’y + xy’ ) + xy = xy’z + x’yz + xy

5.2. EMPAT BIT FULL ADDER

Pada sub-bab diatas telah dibahas maslah full adder yang membentuk penjumlah 2 bit dan carry yang timbul sebelumnya. Dua bilangan biner dari n-bit, setiap bitnya dapat ditambahkan dengan menggunakan rangkaian tersebut. Untuk memperlihatkan sistem penjumlahan ini, marilah kita lihat contoh berikut :

Misalnya :

A = 1 0 1 1

B = 0 0 1 1 , maka

Metode penjumlahan ini dapat ditunjukkan dibawah ini :

Subscript i 4 3 2 1 Simbol Full Adder

- Carry Input (Cin) 0 1 1 0 Ci z

- Yang dijumlahkan 1 0 1 1 Ai x

- Penjumlah 0 0 1 1 Bi + y

- Hasil Penjumlahan (S) 1 1 1 0 Si S

- Carry Output (Cout) 0 0 1 1 Ci+1 C

Rangkaian dari penjumlah ini dapat dibentuk dengan beberapa Full Adder (sesuai dengan jumlah bit yang dijumlahkan) yang dihubungkan secara cascade, dengan carry output dari suatu full adder dihubungkan ke carry input dari full adder berikutnya :

Gambar 5.2.1. Rangakaian 4 bit Full Adder

Jika rangkaian 4-bit Full Adder ini dikemas dalam paket IC, maka IC ini mempunyai 4 (empat) terminal untuk bit yang dijumlahkan dan 4 (empat) terminal untuk bit-bit penjumlah, dan 2 terminal untuk carry input dan carry output. Dan 4-bit Full Adder telah dibentuk dalam IC TTL 74283.

Cout F A Cin S3 x3 y3 F A S2 x2 y2 F A S1 x1 y1 F A S0 x0 y0

Gambar 5.2.2. Blok Diagram 4-bit Full Adder (IC TTL 74283) Cout F A Cin S3 x3 y3 F A S2 x2 y2 F A S1 x1 y1 F A S0 x0 y0

5.3. DECODER

Decoder adalah suatu rangkaian kombinasional yang mengkonversikan informasi biner dari n jalur input ke maksimum 2n terminal output.

Decoder yang dimaksud adalah biasa disebut decoder n ke m jalur dimana m 2n , dan ini bertujuan untuk membangkitkan output 2n (atau kurang) dari n variabel input. Decoder ini juga banyak digunakan pada konversi kode seperti decoder BCD to 7-Segment. x y z D0 = x'y'z' D1 = x'y'z D2 = x'yz' D3 = x'yz D4 = xy'z' D5 = xy'z D6 = xyz' D7 = xyz Enable

Sebagai contoh, amati rangkaian decoder 3 ke 8 jalur seperti terlihat pada gambar 5.3.1. Untuk 3 buah input yang dikodekan dalam 8 output, setiap output mewakili satu kombinasi input.

Ada 3 gerbang not yang berfungsi sebagai inverter dan 8 gerbang NAND untuk membangkitkan setiap kombinasi input. Aplikasi khusus dari rangkaian ini adalah untuk mengkonversikan BCD ke Oktal. Variabel input mewakili sebuah bilangan biner dan outputnya akan mewakili 8 digit dalam sistem oktal. Dekoder 3 ke 8 jalur ini telah dibuat dalam satu paket IC TTL tipe 74 138, dengan tabel kebenaran seperti dibawah ini.

TABEL 5.3.1. Truth Tabel dari Decoder 3 ke 8 Jalur

Input Output x Y z D0 D1 D2 D3 D4 D5 D6 D7 0 0 0 0 1 1 1 1 1 1 1 0 0 1 1 0 1 1 1 1 1 1 0 1 0 1 1 0 1 1 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 0 0 1 1 1 1 0 1 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 0

Latihan 5.1.

Desain sebuah decoder dari BCD ke Desimal , dalam hal ini adalah 10 digit desimal yang diekspresikan dalam BCD (4 bit).

Maka Decoder tersebut akan membentuk 4 ke 10 jalur ( Decoder BCD ke Desimal).

Dengan ketentuan menggunakan tabel kebenaran berikut ini.

TABEL 5.3.2. Truth Tabel Decoder 4 ke 10 Jalur Input W X Y Z Output 0 0 0 0 D0 0 0 0 1 D1 0 0 1 0 D2 0 0 1 1 D3 0 1 0 0 D4 0 1 0 1 D5 0 1 1 0 D6 0 1 1 1 D7 1 0 0 0 D8 1 0 0 1 D9 1 0 1 0 Don’t Care 1 0 1 1 Don’t Care 1 1 0 0 Don’t Care 1 1 0 1 Don’t Care 1 1 1 0 Don’t Care 1 1 1 1 Don’t Care

Untuk memudahkan penggambaran perlu dilakukan penyederhanaan dengan metode mapping. YZ WX 00 01 11 10 00 D0 D1 D3 D2 01 D4 D5 D7 D6 11 X X X X 10 D8 D9 X X Contoh penyederhanaan : D3 = X’ YZ D8 = WZ’ D9 = WZ

Sedangkan Decoder BCD ke Desimal ini sudah dikemas dalam IC TTL dengan tipe 74 42.

5.4. DEMULTIPLEXER (DEMUX)

Beberapa IC decoder disusun dari beberapa gerbang NAND karena gerbang NAND memiliki 2 (dua) operasi yaitu operasi AND dan operasi NOT (pembalikan), ini membuat semakin murahnya harga IC.

Kebanyakan IC decoder mempunyai 1 (satu) Enable input (mengaktifkan rangkaian) atau untuk mengontrol operasi dari rangkaian tersebut.

Sebuah decoder 3 ke 8 jalur dengan sebuah enable input yang dibentuk dari gerbang NAND dapat diperlihatkan pada gambar 8.1. dengan truth table yang ada pada TABEL 5.4.1. dibawah ini.

TABEL 5.4.1. Truth Tabel Decoder 3 ke 8 jalur dengan Enable

Input Output Enable (En) x y z D0 D1 D2 D3 D4 D5 D6 D7 1 x x x 1 1 1 1 1 1 1 1 0 0 0 0 0 1 1 1 1 1 1 1 0 0 0 1 1 0 1 1 1 1 1 1 0 0 1 0 1 1 0 1 1 1 1 1 0 0 1 1 1 1 1 0 1 1 1 1 0 1 0 0 1 1 1 1 0 1 1 1 0 1 0 1 1 1 1 1 1 0 1 1 0 1 1 0 1 1 1 1 1 1 0 1 0 1 1 1 1 1 1 1 1 1 1 0

Semua output akan berlogika ‘1’ jika Enable input (En) berlogika ‘1’ untuk semua kombinasi input (x, y, ,dan z). Jika Enable (En) berlogika ‘0’ maka rangkaian ini beroperasi seperti decoder biasa. Ini menunjukkan bahwa Enable input tersebut adalh aktif rendah (low) atau akan aktif apabila diberikan logika ‘0’.

Decoder dengan 1 (satu) Enable input dapat berfungsi sebagai DEMULTIPLEXER (DEMUX).

kemungkinan jalur output. Perubahan fungsi dari Decoder menjadi Demultiplexer dapat dilihat pada blok diagram dibawah ini menggunakan Decoder 2 ke 4 jalur.

Gambar 5.4.1. Blok Diagram Perubahan fungsi Decoder ke Demultiplexer Decoder 2 ke 4 jalur dapat berfungsi sebagai Demultiplexer jika Enable input digunakan sebagai jalur input dan terminal input x dan y digunakan sebagai jalur seleksi.

Rangkaian Decoder / Demultiplexer dapat dihubungkan bersama untuk membentuk rangkaian Decoder yang lebih besar. Gambar dibawah ini menunjukkan dua buah Decoder 2 ke 4 jalur dengan enable input yang dihubungkan bersama untuk membentuk Decoder 3 ke 8 jalur.

Gambar 5.4.2. Decoder 3 ke 8 yang terbentuk dari 2 buah decoder 2 ke 4 jalur.

x y En D0 D1 D2 D3 DECODER

2 TO 4 LINE DEMULTIPLEXER1 TO 4 LINE

D0 D1 D2 D3 x y En

DECODER DENGAN ENABLE DEMULTIPLEXER

DECODER 2 TO 4 LINE D0 D1 D2 D3 En x y DECODER 2 TO 4 LINE x y En A B C MSB D4 D5 D6 D7

5.5. ENCODER

Encoder adalah suatu fungsi digital yang mempunyai operasi kebalikan dari Decoder. Encoder mempunyai 2n (atau kurang) jalur input dan n jalur output membangkitkan kode biner untuk 2n variable input.

Satu contoh Encoder dapat dilihat pada gambar 8.4, yaitu Encoder oktal ke biner memiliki 8 input dan 3 output yang membangkitkan bilangan biner tertentu. Rangkaian ini dibentuk dengan menggunakan gerbang OR yang outputnya ditentukan dari truth table pada Tabel 5.5.1.

Gambar 5.5.1. Encoder Oktal ke Biner

D0

D1

D2

D3

D4

D5

D6

D7

X = D4 + D5 + D6 + D7 Y = D2 + D3 + D6 + D7 Z = D1 + D3 + D5 + D7Tabel 5.5.1. Truth Table dari Encoder Oktal ke Biner. INPUT OUTPUT D0 D1 D2 D3 D4 D5 D6 D7 X Y Z 1 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 1 1 0 0 0 0 1 0 0 0 1 0 0 0 0 0 0 0 1 0 0 1 0 1 0 0 0 0 0 0 1 0 1 1 0 0 0 0 0 0 0 0 1 1 1 1

Encoder dalam gambar 5.5.1. ini mengasumsikan bahwa hanya satu jalur input sama dengan ‘1’1 pada setiap waktu. Jika ada dua atau lebih logika ‘1’ maka rangkaian ini tidak berarti.

Karena jika suatu rangkaian mempunyai 8 variabel input, maka akan mempunyai 28 = 256 kombinasi input. Sedangkan disini yang mempunyai arti hanya 8 kombinasi input, kombinasi yang laian adalah pada kondisi diabaikan (don’t care).

5.6. MULTIPLEXER

Multiplexing berarti pengiriman (transmisi) satu unit informasi dalam jumlah besar melalui jumlah chanel/jalur yang lebih sedikit.

Digital Multiplexer adalah suatu rangkaian kombinasional yang memilih informasi biner dari beberapa jalur input dan mengeluarkan satu jalur output.

Seleksi untuk jalur input tertentu dikontrol oleh satu set jalur seleksi. Multiplexer 4 jalur ke 1 jalur adalah ditunjukan pada gambar 5.6.1.

Gambar 5.6.1. Rangkaian Logika dari Multiplexer 4 – 1 jalur.

Gambar 5.6.2. Simbol Multiplexer 4 x 1.

MULTIPLEXER 4 x 1

I0

I1

I2

I3

S1

S0

Y

I0 I1 I2 I3 S0 S1 YMUX

4 X 1

I N P U T OUTPUT JALUR SELEKSITabel 5.6.1. Truth Table Multiplexer 4 x 1 S0 S1 Y 0 0 I0 0 1 I1 1 0 I2 1 1 I3

Setiap jalur input (I0 sampai dengan I3) dihubungkan ke salah satu input AND gate. Jalur seleksi S0 dan S1 digunakan untuk memilih AND gate tertentu (lihat gambar 5.6.1.). Tabel kebenaran (truth table) 9.1. menunjukkan daftar input output untuk setiap kombinasi input dari jalur seleksi.

Multiplexer juga bisa disebut pen-seleksi data (atau data selektor) karena rangkaian ini memilih salah satu dari beberapa input dan mengontrol informasi biner ke jalur output.

Pada umumnya, Multiplexer 2n ke 1 jalur disusun dari sebuah decoder n ke 2n dan ditambah dengan 2n jalur input untuk setiap input AND gate. Keluaran dari AND gate itu dihubungkan ke input OR gate untuk membentuk satu jalur output. Multiplexer biasa disebut dengan MUX.

5.6.2. Implementasi Aljabar Boolean

Pada aplikasinya, multiplexer juga dapat digunakan untuk meng-implementasi-kan aljabar Boolean dari n variabel dengan menggunameng-implementasi-kan 2n ke 1 Multiplexer.

Jika kita memiliki suatu fungsi boolean dengan n+1 variabel, maka kita pilih salah satu variabel sebagai input multiplexer dari I0, I1, …,In-1, sedangkan sisanya dihubungkan dengan jalur seleksi. Dengan demikian , akan membentuk fungsi n variabel dengan 2n ke 1 multiplexer (2n x 1 MUX).

Sebagai contoh :

Kita memiliki fungsi boolean F (A,B,C) = (1, 3, 5, 6) Untuk meng-implementasi-kan fungsi diatas, ikuti prosedur dibawah ini :

1. Fungsi diatas memiliki 3 variabel (A, B, dan C) dengan tabel kebenaran sebagai berikut : Minterm A B C F 0 0 0 0 0 1 0 0 1 1 2 0 1 0 0 3 0 1 1 1 4 1 0 0 0 5 1 0 1 1 6 1 1 0 1 7 1 1 1 0

2. Pilih salah satu variabel sebagai input multiplexer, misalnya kita pilih variabel A sebagai input multiplexer.

3. Maka variabel yang tersisa adalah 2 variabel yaitu variabel B (msb) dan C (lsb), yang akan kita hubungkan ke jalur seleksi Multiplexer. Dari variabel yang tersisa maka multiplexer yang tepat untuk dipakai adalah 2n ke 1 dimana n = 2 (jumlah variabel tersisa), maka multiplexer yang dipilih adalah 22 ke 1 MUX atau 4 x 1 MUX, dengan hubungan jalur seleksi S1 hihubungkan