TRANSFORMASI WAVELET DAUBECHIES

DENGAN MENGGUNAKAN SYSTEMC

AWAL DARI DSP ENGINE

Akhmad Mulyanto 23203097

Abstrak. Desain VLSI DSP dalam VHDL mempunyai kendala nilai floating

point yang tidak friendly, mengakibatkan proses debug sulit dan lama. SystemC menawarkan solusi atas masalah ini dan juga mempunyai kemampuan untuk melakukan test numeric dalam usaha memenuhi suatu standard. Desain sistem pada level RTL dengan SystemC juga menghasilkan “VHDL RTL design look like”, sehingga desain dalam System dan desain dalam VHDL mudah saling dikonversikan. Transformasi Wavelet menawarkan kinerja yang tinggi dalam kompresi baik dalam ratio kompresi maupun dalam kecepatan kompresinya.

1 Pendahuluan

Pada saat paper ini dibuat, DSP Engine dengan kemampuan Wavelet Transform, DCT Transform, Motion Estimator, dan Image Processing belum menjadi tujuan utama dari desain. Tujuan dari desain adalah membuat platform DSP engine dengan salah satu fungsinya adalah Wavelet Transform. Fungsi-fungsi dan algoritma-algoritma lainnya dapat ditambahkan dan dikembangkan dikemudian hari. Fitur dari fungsi Wavelet Transform pun masih terbatas pada satu dimensi panjang filter sama dengan 4 (Daubechies 4). Idealnya suatu Wavelet Transform pada DSP Engine mempunyai parameter dimensi dan panjang filter yang proggrammable.

2 Kecepatan Transformasi Wavelet Daubechies Empat

Wavelet transform menawarkan kecepatan komputasi yang menarik. Untuk mentransformasikan n data, hanya diperlukan n akses ke n alamat memory. Selama proses pembacaan data, secara simultan data yang telah dibaca ditransformasikan. Sehingga hanya dibutuhkan n + m latency clock untuk menyelesaikan proses transformasi. Perhitungan komputasi lebih lanjut untuk melaksanakan suatu wavelet transform untuk suatu filter dengan panjang L dan suatu sinyal dengan panjang N=2k adalah sebagai berikut:

Pada tingkat pertama, seluruh N data dilewatkan pada filter bank pertama.

Pada tingkat kedua, separuh N data hasil filter bank pertama dilewatkan pada filter bank kedua.

Pada tingkat berikutnya, seperempat N data hasil filter bank kedua dilewatkan pada filter bank berikutnya.

) 1 ... 2 1 2 1 ( ) ... 2 2 ( cos 2 log N NL N N N N L tlowpass N

Kalkulasi untuk filter high pass adalah sama, sehingga :

LN NL NL NL NL NL t t t t k k k M k m k pass high pass low 2 2 1 1 2 2 1 1 2 1 1 1 2 1 1 2 1 2 1 ) 2 1 ... 2 1 2 1 1 ( cos cos cos cos 1 0 1

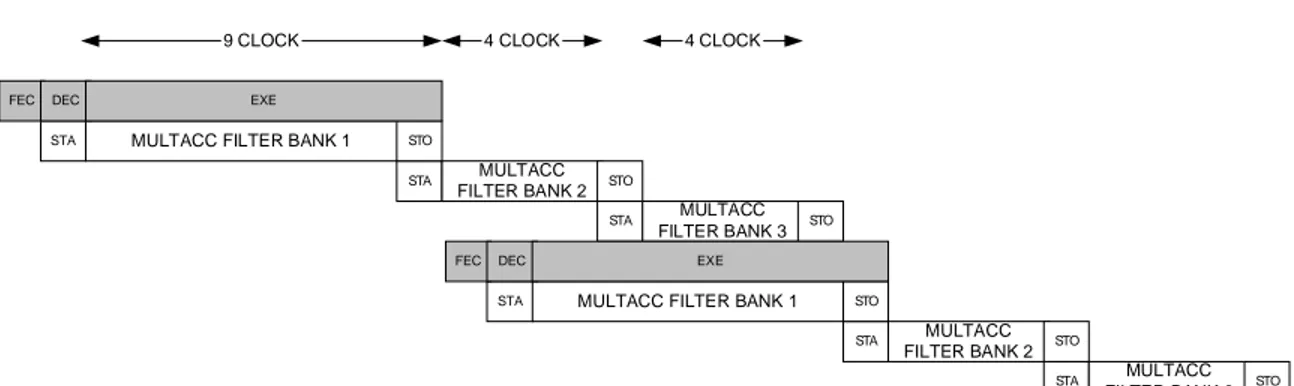

Untuk L = 4 dan N = 8 dapat diharapkan selesai kurang dari 64 clock. Untuk L = 4 dan N = 64 dapat diharapkan selesai kurang dari 512 clock Yang menarik adalah dengan membuat masing-masing filter bank terpisah dan suatu arsitektur yang effisien maka 8 x 8 data bahkan bisa diselesaikan dalam 64 clock + n clock seperti pada gambar 1 berikut :

STA MULTACC FILTER BANK 1

STA MULTACC

FILTER BANK 2 STO

STO

STA MULTACC

FILTER BANK 3 STO

STA MULTACC FILTER BANK 1

STA MULTACC

FILTER BANK 2 STO

STO

STA MULTACC

FILTER BANK 3 STO

8 CLOCK 4 CLOCK 4 CLOCK

Gambar 1. Diagram Timing Untuk Hardware Control Daubechies 4

Implementasi yang sudah dilakukan adalah seperti pada gambar 2. Dengan L = 4 dan N = 64, menghasilkan 8 data hasil pertama pada clock ke 42 dan 8 data hasil terakhir pada clock 120. Dapat disimpulkan nilai latency clock adalah 32. Memory data diakses dalam 8 clock pada 8 clock terakhir fasa EXECUTE, membuat memory available selama 3 clock berturut-turut pada fasa FETCH, DECODE dan EXECUTE clock pertama. Sehingga pada saat itu memory dapat digunakan untuk proses lain dengan suatu sistem perwasitan bus. Misalkan arsitektur didesain untuk dapat meload 64 data secara berurutan dalam 64 clock maka dapat diperkirakan waktu komputasi 64 data adalah 3 + 64 + 32 = 99 clock jauh lebih cepat dari DCT transform untuk 64 bit yang diperkirakan mempunyai

waktu komputasi tercepat 3 + 64 + 64 = 131 clock. Apalagi bila setiap filter bank pada transformasi wavelet daubechies menggunakan parallel multiplier, maka waktu komputasinya (estimasi) menjadi 3 + 64 + 15 = 82 clock!.

FEC

STA MULTACC FILTER BANK 1

STA MULTACC FILTER BANK 2 STO STO

STA MULTACC FILTER BANK 3 STO

DEC EXE

STA MULTACC FILTER BANK 1

STA MULTACC FILTER BANK 2 STO STO

STA MULTACC FILTER BANK 3 STO FEC DEC EXE

9 CLOCK 4 CLOCK 4 CLOCK

Gambar 2. Diagram Timing Untuk Software Control Daubechies 4

3. Transformasi Wavelet Daubechies Empat

Transformasi wavelet Daubechies Empat menggunakan FIR empat tap dengan koefisien ternormalisasi : 22551260 -0.1294095 2 4 3 1 ] 3 [ 8042013 0.22414386 2 4 3 3 ] 2 [ 3737808 0.83651630 2 4 3 3 ] 1 [ 3144534 0.48296291 2 4 3 1 ] 0 [ c c c c

sebagai low pass filter (LPF) dan FIR empat tap dengan koefisien ternormalisasi:

3144534 0.48296291 2 4 3 1 ] 0 [ ] 3 [ 3737808 0.83651630 2 4 3 3 ] 1 [ ] 2 [ 8042013 0.22414386 2 4 3 3 ] 2 [ ] 1 [ 22551260 -0.1294095 2 4 3 1 ] 3 [ ] 0 [ c d c d c d c d

sebagai suatu high pass filter (HPF) untuk menguraikan sinyal. Kombinasi LPF dan HPF inilah yang disebut filter bank. Komputasi dalam filter bank pertama untuk input data f0 ={ f(0),f(1),f(2), f(3),f(4),f(5),f(6),f(7)}=(2,5,8,9,7,4,-1,1) adalah:

) 7 ( ) 3 ( ) 6 ( ) 2 ( ) 5 ( ) 1 ( ) 4 ( ) 0 ( ) 5 ( ) 3 ( ) 4 ( ) 2 ( ) 3 ( ) 1 ( ) 2 ( ) 0 ( ) 3 ( ) 3 ( ) 2 ( ) 2 ( ) 1 ( ) 1 ( ) 0 ( ) 0 ( ) 1 ( ) 3 ( ) 0 ( ) 2 ( ) 7 ( ) 1 ( ) 6 ( ) 0 ( ) 7 ( ) 3 ( ) 6 ( ) 2 ( ) 5 ( ) 1 ( ) 4 ( ) 0 ( ) 5 ( ) 3 ( ) 4 ( ) 2 ( ) 3 ( ) 1 ( ) 2 ( ) 0 ( ) 3 ( ) 3 ( ) 2 ( ) 2 ( ) 1 ( ) 1 ( ) 0 ( ) 0 ( ) 1 ( ) 3 ( ) 0 ( ) 2 ( ) 7 ( ) 1 ( ) 6 ( ) 0 ( 1 f d f d f d f d f d f d f d f d f d f d f d f d f d f d f d f d f c f c f c f c f c f c f c f c f c f c f c f c f c f c f c f c f = (0.155, 5.78, 12.4, 6.37, -0.837, 0.966, 0.871, -3.12)

Output f1 selanjutnya menjadi input filter bank kedua. Komputasi dalam filter bank kedua untuk input data f1 ={ f1(0),f1(1),f1(2), f1(3),f1(4),f1(5),f1(6),f1(7)}= (0.155, 5.78, 12.4, 6.37, -0.837, 0.966, 0.871, -3.12) adalah: ) 7 ( ) 6 ( ) 5 ( ) 4 ( ) 3 ( ) 3 ( ) 2 ( ) 2 ( ) 1 ( ) 1 ( ) 0 ( ) 0 ( ) 1 ( ) 3 ( ) 0 ( ) 2 ( ) 3 ( ) 1 ( ) 2 ( ) 0 ( ) 3 ( ) 3 ( ) 2 ( ) 2 ( ) 1 ( ) 1 ( ) 0 ( ) 0 ( ) 1 ( ) 3 ( ) 0 ( ) 2 ( ) 3 ( ) 1 ( ) 2 ( ) 0 ( 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 2 f f f f f d f d f d f d f d f d f d f d f c f c f c f c f c f c f c f c f = (10.6, 6.87, -5.7, 6.02, -0.837, 0.966, 0.871, -3.12)

Output f2 selanjutnya menjadi input filter bank ketiga. Komputasi dalam filter bank ketiga untuk input data f2 ={ f1(0),f1(1),f1(2), f1(3),f1(4),f1(5),f1(6),f1(7)}= (10.6, 6.87, -5.7, 6.02, -0.837, 0.966, 0.871, -3.12) adalah: ) 7 ( ) 6 ( ) 5 ( ) 4 ( ) 3 ( ) 2 ( ) 3 ( ) 3 ( ) 2 ( ) 2 ( ) 1 ( ) 1 ( ) 0 ( ) 0 ( ) 1 ( ) 3 ( ) 0 ( ) 2 ( ) 1 ( ) 1 ( ) 0 ( ) 0 ( 2 2 2 2 2 2 2 2 2 2 2 2 2 2 3 f f f f f f f d f d f d f d f c f c f c f c f = (12.4, 2.66, -5.7, 6.02, -0.837, 0.966, 0.871, -3.12)

4. Implementasi Transformasi Wavelet Daubechies Empat

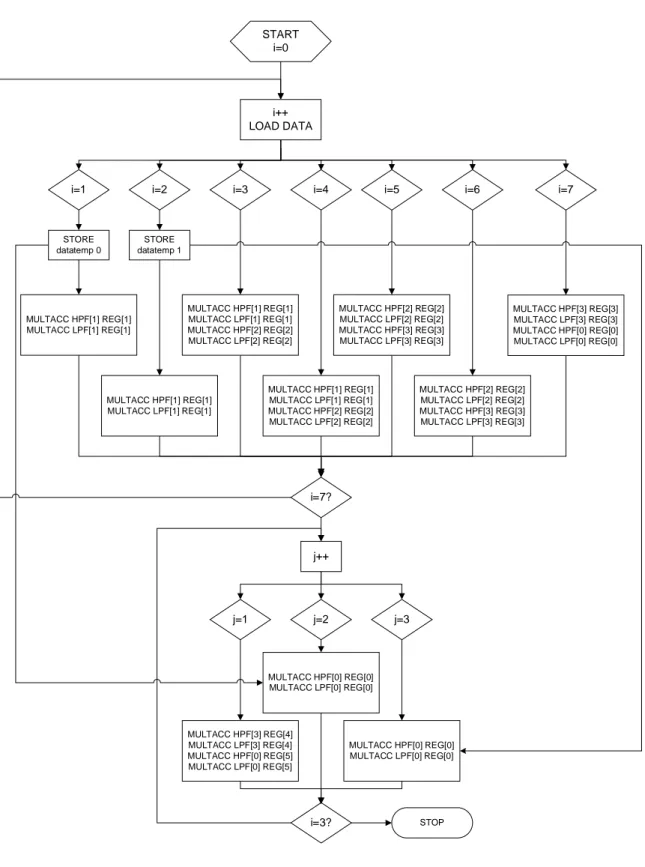

Diagram flowchart dari filter bank pertama dari Transformasi wavelet Daubechies Empat dengan menggunakan 8 multiplier dan 8 accumulator, dapat digambarkan pada gambar 3 sebagai berikut: START i=0 LOAD DATA MULTACC HPF[1] REG[1] MULTACC LPF[1] REG[1] i=0 STORE datatemp 0

i=1 i=2 i=3 i=4 i=5 i=6 i=7

MULTACC HPF[1] REG[1] MULTACC LPF[1] REG[1] MULTACC HPF[1] REG[1] MULTACC LPF[1] REG[1] MULTACC HPF[2] REG[2] MULTACC LPF[2] REG[2] MULTACC HPF[1] REG[1] MULTACC LPF[1] REG[1] MULTACC HPF[2] REG[2] MULTACC LPF[2] REG[2] MULTACC HPF[2] REG[2] MULTACC LPF[2] REG[2] MULTACC HPF[3] REG[3] MULTACC LPF[3] REG[3] MULTACC HPF[2] REG[2] MULTACC LPF[2] REG[2] MULTACC HPF[3] REG[3] MULTACC LPF[3] REG[3] MULTACC HPF[3] REG[3] MULTACC LPF[3] REG[3] MULTACC HPF[0] REG[0] MULTACC LPF[0] REG[0] MULTACC HPF[3] REG[3] MULTACC LPF[3] REG[3] MULTACC HPF[0] REG[0] MULTACC LPF[0] REG[0] STORE datatemp 1 MULTACC HPF[0] REG[0] MULTACC LPF[0] REG[0] MULTACC HPF[0] REG[0] MULTACC LPF[0] REG[0] i=8 i=9 i=9? i++ STOP

Gambar 3. Filter Bank Pertama Dengan Sebuah Proses Tunggal

Diperlukan minimal 10 clock untuk menyelesaikan proses komputasi. Ditambah dengan 2 clock sinkronisasi maka dibutuhkan 12 clock. Hal ini tentu saja tidak memenuhi spesifikasi desain pada gambar 2. Untuk itu dibuat perubahan seperti pada gambar 4. Pada gambar 4, filter bank dibagi dalam dua proses sekuensial. Proses pertama memerlukan 8 clock untuk menyelesaikan prosesnya. Setelah proses pertama selesai, kerja filter bank dilanjutkan oleh proses kedua. Sementara proses pertama kembali pada posisi tunggu siap untuk melakukan filter pada 8 data berikutnya. Harga yang harus dibayar adalah penambahan sebuah state machine, empat multiplier dan sebuah accumulator.

START i=0 MULTACC HPF[1] REG[1] MULTACC LPF[1] REG[1] i=1 STORE datatemp 0

i=2 i=3 i=4 i=5 i=6

MULTACC HPF[1] REG[1] MULTACC LPF[1] REG[1] MULTACC HPF[1] REG[1] MULTACC LPF[1] REG[1] MULTACC HPF[2] REG[2] MULTACC LPF[2] REG[2] MULTACC HPF[1] REG[1] MULTACC LPF[1] REG[1] MULTACC HPF[2] REG[2] MULTACC LPF[2] REG[2] MULTACC HPF[2] REG[2] MULTACC LPF[2] REG[2] MULTACC HPF[3] REG[3] MULTACC LPF[3] REG[3] MULTACC HPF[2] REG[2] MULTACC LPF[2] REG[2] MULTACC HPF[3] REG[3] MULTACC LPF[3] REG[3] STORE datatemp 1 i=7? STOP i=7 j=1 MULTACC HPF[3] REG[3] MULTACC LPF[3] REG[3] MULTACC HPF[0] REG[0] MULTACC LPF[0] REG[0] MULTACC HPF[3] REG[4] MULTACC LPF[3] REG[4] MULTACC HPF[0] REG[5] MULTACC LPF[0] REG[5] MULTACC HPF[0] REG[0] MULTACC LPF[0] REG[0] MULTACC HPF[0] REG[0] MULTACC LPF[0] REG[0] j=2 j=3 j++ i=3? i++ LOAD DATA

Diagram flowchart dari filter bank kedua dari Transformasi wavelet Daubechies Empat dengan menggunakan 4 multiplier dan 4 accumulator, dapat digambarkan pada gambar 5 sebagai berikut: START i=0 i++ LOAD DATA MULTACC HPF[1] REG[1] MULTACC LPF[1] REG[1] i=1 STORE datatemp 0

i=2 i=3 i=4 i=5 i=6

MULTACC HPF[1] REG[1] MULTACC LPF[1] REG[1] MULTACC HPF[1] REG[1] MULTACC LPF[1] REG[1] MULTACC HPF[0] REG[0] MULTACC LPF[0] REG[0] MULTACC HPF[1] REG[1] MULTACC LPF[1] REG[1] MULTACC HPF[0] REG[0] MULTACC LPF[0] REG[0] MULTACC HPF[0] REG[0] MULTACC LPF[0] REG[0] MULTACC HPF[0] REG[0] MULTACC LPF[0] REG[0] STORE datatemp 1 i=6? i++ STOP

Gambar 5. Filter Bank Kedua Dengan Sebuah Proses Sekuensial Sesuai dengan gambar 2, maka fungsi filter bank kedua dan fungsi filter bank ketiga dapat dilaksanakan oleh filter bank yang sama. Hasilnya adalah arsitektur yang lebih effisien.

Diagram flowchart dari filter bank ketiga dari Transformasi wavelet Daubechies Empat dengan menggunakan 2 multiplier dan 2 accumulator, dapat digambarkan pada gambar 6 sebagai berikut: START i=0 i++ LOAD DATA MULTACC HPF[0] REG[0] MULTACC LPF[0] REG[0] i=1 STORE datatemp 0

i=2 i=3 i=4

MULTACC HPF[0] REG[0] MULTACC LPF[0] REG[0] MULTACC HPF[0] REG[0] MULTACC LPF[0] REG[0] MULTACC HPF[0] REG[0] MULTACC LPF[0] REG[0] STORE datatemp 1 i=4? STOP

5. Arsitektur DSP Engine Dengan Fitur Transformasi Wavelet

Daubechies Empat

Walau tujuan utama dari desain adalah hanya membuat transformasi wavelet Daubechies empat, terdapat banyak aspek yang memaksa pembuatan platform DSP Engine terlebih dahulu. Aspek-aspek tersebut adalah:

1. Performance, berkaitan dengan jumlah cycle/clock.

2. I/O interface, berkaitan dengan bagaimana data input dibaca dan data output ditulis.

3. Sinkronisasi sistem, berkaitan dengan timing kerja.

Sehingga dirancanglah platform DSP Engine. DSP Engine mempunyai arsitektur microprocessor dengan software code-nya berfungsi untuk mengatur kerja dari DSP Engine keseluruhan. Instruction untuk melaksanakan wavelet 64 data pada memory data yang dimulai dengan address 0 didefinisikan sebagai berikut:

prog[1] = 0x05080001; /* WAVEA */ prog[2] = 0x05080002; /* WAVEB */ prog[3] = 0x05080001; /* WAVEA */ prog[4] = 0x05080002; /* WAVEB */ prog[5] = 0x05080001; /* WAVEA */ prog[6] = 0x05080002; /* WAVEB */ prog[7] = 0x05080001; /* WAVEA */ prog[8] = 0x05080002; /* WAVEB */

OPCODE NUM DATA ADDRESS REGISTER

NAMA NILAI BIT NAMA BIT NAMA BIT BIT

WAVE 5 16 - 8 - 12 ACCA,

ACCB 4

Instruction 0x05080001 menyatakan “Lakukan wavelet transform dari 8 data dimulai pada memory dengan offset alamat = 0 dan simpan data dari memory pada register A”. Instruction 0x05080002 menyatakan “Lakukan wavelet transform dari 8 data dimulai pada memory dengan offset alamat = 0 dan simpan data dari memory pada register B”. Dua perintah WAVE yang berurutan tidak bisa menyimpan hasilnya pada register yang sama, karena setelah suatu register menyimpan data yang diload dari memory, register itu dipergunakan sebagai source data untuk filter bank 1.

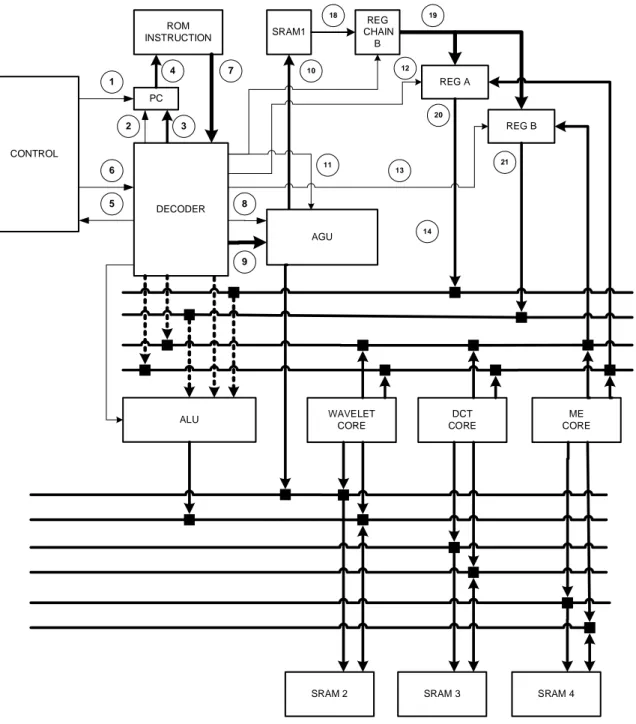

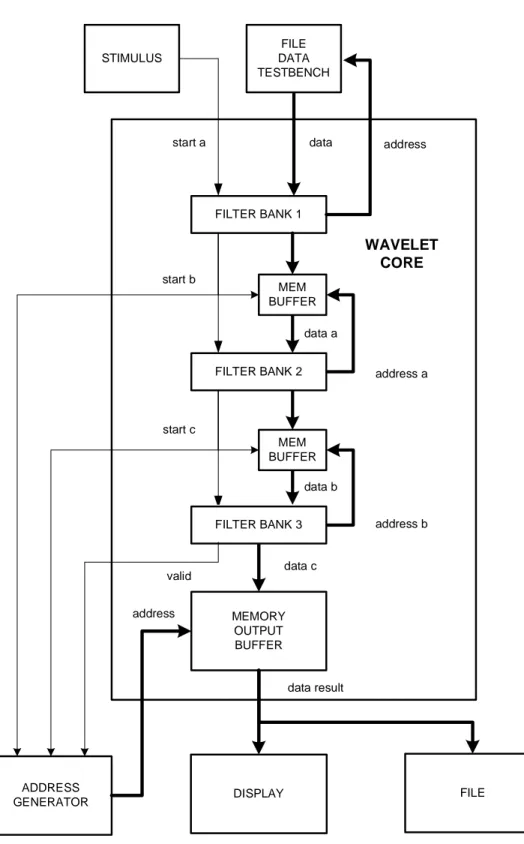

Arsitektur DSP Engine dengan fitur Wavelet Transform diperlihatkan pada gambar 7. Arsitektur ini bisa dikembangkan menjadi arsitektur DSP Engine dengan fitur Wavelet Transform, DCT Transform, dan Motion Estimator seperti pada gambar 8.

PC CONTROL REG A REG B AGU MUX FILTER BANK 1 MEM BUFFER SRAM 2 4 5 1 2 6 8 9 SRAM1 REG CHAIN B ROM INSTRUCTION 3 10 11 12 13 14 15 16 18 19 20 21 22 25 23 24 27 28 31 32 26 30 29 33 DECODER ALU FILTER BANK 2 FILTER BANK 3 MEM BUFFER 7

PC CONTROL REG A REG B AGU 4 5 1 2 6 8 9 SRAM1 REG CHAIN B ROM INSTRUCTION 3 10 11 12 13 14 18 19 20 21 DECODER ALU 7 WAVELET CORE DCT CORE ME CORE

SRAM 2 SRAM 3 SRAM 4

Gambar 8. Arsitektur DSP Engine dengan fitur Wavelet Transform, DCT Transform, dan Motion Estimator

Arsitektur Fast Wavelet Core

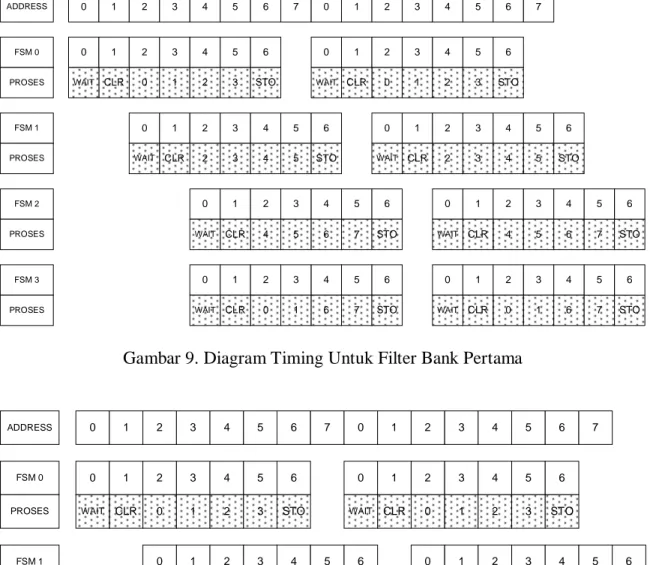

Desain Fast Wavelet Core dicapai dengan pembagian state machine dan timing. State machine dan timing dari Filter Bank Pertama :

0 1 2 3 4 5 6 0 1 2 3 0 1 2 3 4 5 6 2 3 4 5 0 1 2 3 4 5 6 4 5 6 7 0 1 2 3 4 5 6 0 1 6 7 STO STO STO STO CLR WAIT CLR WAIT CLR WAIT CLR WAIT 0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 0 1 2 3 0 1 2 3 4 5 6 2 3 4 5 0 1 2 3 4 5 6 4 5 6 7 0 1 2 3 4 5 6 0 1 6 7 STO STO STO STO CLR WAIT CLR WAIT CLR WAIT CLR WAIT 0 1 2 3 4 5 6 7 ADDRESS FSM 0 PROSES FSM 1 PROSES FSM 2 PROSES FSM 3 PROSES

Gambar 9. Diagram Timing Untuk Filter Bank Pertama

0 1 2 3 4 5 6 0 1 2 3 0 1 2 3 4 5 6 2 3 4 5 STO STO CLR WAIT CLR WAIT 0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 0 1 2 3 0 1 2 3 4 5 6 2 3 4 5 STO STO CLR WAIT CLR WAIT 0 1 2 3 4 5 6 7 ADDRESS FSM 0 PROSES FSM 1 PROSES

Gambar 10. Diagram Timing Untuk Filter Bank Kedua

0 1 2 3 4 5 6 0 1 2 3 STO CLR WAIT 0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 0 1 2 3 STO CLR WAIT 0 1 2 3 4 5 6 7 ADDRESS FSM 0 PROSES

Dari gambar 9-11 nampak bahwa arsitektur tiap Filter Bank dapat memfilter data 8 bit yang data berurutan.

FILTER BANK 1 MEM BUFFER FILTER BANK 2 FILTER BANK 3 MEM BUFFER MEMORY OUTPUT BUFFER start a start b start c valid data data a data b data c ADDRESS GENERATOR address data result address a address b FILE DATA TESTBENCH STIMULUS DISPLAY address WAVELET CORE FILE

0 1 2 3 4 5 6 0 1 2 3 0 1 2 3 4 5 6 2 3 4 5 0 1 2 3 4 5 6 4 5 6 7 0 1 2 3 4 5 6 0 1 6 7 S T O S T O S T O S T O C L R W A IT C L R W A IT C L R W A IT C L R W A IT 0 1 2 3 4 5 6 7 0 1 2 3 4 5 6 0 1 2 3 0 1 2 3 4 5 6 2 3 4 5 0 1 2 3 4 5 6 4 5 6 7 0 1 2 3 4 5 6 0 1 6 7 S T O S T O S T O S T O C L R W A IT C L R W A IT C L R W A IT C L R W A IT 8 9 1 0 1 1 1 2 1 3 1 4 1 5 C L O C K F S M 0 a P R O S E S F S M 1 a P R O S E S F S M 2 a P R O S E S F S M 3 a P R O S E S 0 1 2 3 4 5 6 0 1 2 3 0 1 2 3 4 5 6 2 3 4 5 0 1 2 3 4 5 6 0 1 6 7 S T O S T O S T O C L R W A IT C L R W A IT C L R W A IT 0 1 2 3 4 5 6 0 1 2 3 0 1 2 3 4 5 6 2 3 4 5 0 1 2 3 4 5 6 0 1 6 7 S T O S T O S T O C L R W A IT C L R W A IT C L R W A IT F S M 0 b P R O S E S F S M 1 b P R O S E S F S M c P R O S E S 1 6 1 7 1 8 1 9 2 0 2 1 2 2 2 3 2 4 2 5 2 6 2 7 2 8 2 9 3 0 3 1 3 2 3 3 3 4 3 5 3 6

0 4 0 5 0 6 0 7 0 8 0 9 1 0 1 1 1 2 1 3 1 4 1 5 1 6 1 7 1 8 1 9 2 0 2 1 2 2 2 3 2 4 2 5 2 6 2 7 2 8 2 9 3 0 3 1 3 2 3 3 3 4 3 5 3 6 3 7 3 8 3 9 4 0 4 1 4 2 4 3 F D D E C 1 D E C 2 F D E X E C U T E E X E C U T E F D E X E C U T E S T O A S T O B S T O C 0 W A IT N C 2 C L R 3 4 5 6 M U X 1 M U X 2 S T 1 E N A B L E S H IF T D A T A S H IF T E D E N A B L E S H IF T D A T A S H IF T E D E N A B L E S H IF T D A T A S H IF T E D R E G IS T E R A V A L ID T O R E A D R E G IS T E R B V A L ID T O R E A D 0 W A IT N C 2 C L R 3 4 5 6 0 W A IT N C 2 C L R 3 4 5 6 0 W A IT 1 C L R 2 3 4 5 0 W A IT N C 2 C L R 3 4 5 6 0 W A IT 1 C L R 2 3 4 5 0 W A IT 1 C L R 2 3 4 5 6 S T O 7 S T O 7 S T O 7 S T O 7 S T O 6 S T O 6 S T O A 0 A 1 A 2 A 3 A 4 A 5 A 6 A 7 D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 T IM E IT R D E C O D E R S H IF T C T R L R E G IS T E R A S T A T U S R E G IS T E R B S T A T U S D E C O D E R F IL T E R R U N M U X F IL T E R R U N F IL T E R R U N F IL T E R S T A T U S R E G IS T E R A D D R E S S R E G IS T E R D A T A F S M 0 a F S M 1 a F S M 2 a F S M 3 a F S M 0 b F S M 1 b F S M c

9. Hierarki Desain Dan Timing Dalam SystemC

Emulasi hardware dari systemc memerlukan perhatian dalam timing desain. Signal dalam VHDL bisa di-read dan di-write secara simultan. Dalam systemc, akses read dan write pada sc_signal dilakukan secara bergantian dengan akses read dilaksanakan terlebih dahulu.

DFFE DFFE

IN OUT A OUT B

CLOCK

ENABLE

Gambar 16. Simulasi Rangkaian Register Dalam SystemC

Percobaan desain dalam SystemC untuk rangkaian register pada gambar 9 dengan code: ….…

sc_signal<int> sample;

sc_signal<int> Aresult; sc_signal<int> Bresult; ….…

dffes dffa1 ( "registerA" ); dffa1.clk(clock1); dffa1.ena(ena); dffa1.clr(reset); dffa1.din(sample); dffa1.dout(Aresult);

dffes dffa2 ( "registerB" ); dffa2.clk(clock1);

dffa2.clr(reset); dffa2.din(Aresult); dffa2.dout(Bresult); ….…

Dan tiap modul dffes mempunyai code : ………. sc_signal<int> qwire; void do_ffes() { if (clr) { qwire = 0; } else if (clk.event()) { if (ena.read()==true) { qwire = din.read(); } else { qwire = qwire; } dout.write(qwire); } }; ……….

Maka terdapat empat signal (sc_signal) bertautan yang harus dilalui data dari port input DFFE pertama hingga port output DFFE kedua, mengakibatkan latency clock = 4. Pada VHDL, latency yang terjadi untuk rangkaian pada gambar 9 adalah sama dengan 2.

Signal qwire Signal Aresult Signal qwire Signal Bresult

Gambar 17. Rantai Signal

Latency akibat rantai signal pada gambar 11 dapat dihilangkan dengan menggantikan sc_signal<int> qwire dengan int qwire. Hasil simulasinya adalah seperti pada gambar 12.

Gambar 18. Simulasi Rangkaian Register Dengan Reduksi Rantai Signal

Penggunaan variable sebagai pengganti sc_signal memberikan konsekuensi modul harus mempunyai initial value bagi variable. Konsekuensi dari penggunaan variable dalam VHDL adalah desain tidak lagi generik dan tidak reliable. Ketidakreliable-an modul juga terjadi dalam SystemC seperti diperlihatkan pada gambar 12. Solusi dari masalah ini adalah menggunakan sc_buffer untuk menggantikan sc_signal. Signal sc_buffer mirip dengan signal dalam VHDL, konsekuensi dari penggunaan sc_buffer adalah waktu kompilasi yang jauh lebih lama (terutama jika menggunakan Cygwin).

Gambar 19. Simulasi Rangkaian Register Dengan Reduksi Rantai Signal Dan Driving Port Enable

Gambar 20. Latency akibat penggunaan sc_signal.

Latency juga disebabkan oleh hirarki desain, walaupun sc_signal telah digantikan dengan dengan sc_buffer. Pada gambar 14. Timing Diagram Wavelet Core Dalam DSP Engine, terlihat latency akibat hirarki desain. Address register dihasilkan oleh komponen control_filter_a dalam modul wavecore baru menghasilkan data yang siap pada dua clock berikutnya.

![Diagram flowchart dari filter bank pertama dari Transformasi wavelet Daubechies Empat dengan menggunakan 8 multiplier dan 8 accumulator, dapat digambarkan pada gambar 3 sebagai berikut: START i=0 LOAD DATA MULTACC HPF[1] REG[1] MULTACC LPF[1] REG[1]i=0S](https://thumb-ap.123doks.com/thumbv2/123dok/4375252.3192401/5.918.141.790.224.664/diagram-flowchart-transformasi-daubechies-menggunakan-multiplier-accumulator-digambarkan.webp)

![Diagram flowchart dari filter bank kedua dari Transformasi wavelet Daubechies Empat dengan menggunakan 4 multiplier dan 4 accumulator, dapat digambarkan pada gambar 5 sebagai berikut: START i=0 i++ LOAD DATA MULTACC HPF[1] REG[1] MULTACC LPF[1](https://thumb-ap.123doks.com/thumbv2/123dok/4375252.3192401/7.918.136.784.191.889/diagram-flowchart-transformasi-daubechies-menggunakan-multiplier-accumulator-digambarkan.webp)

![Diagram flowchart dari filter bank ketiga dari Transformasi wavelet Daubechies Empat dengan menggunakan 2 multiplier dan 2 accumulator, dapat digambarkan pada gambar 6 sebagai berikut: START i=0 i++ LOAD DATA MULTACC HPF[0] REG[0] MULTACC LPF[](https://thumb-ap.123doks.com/thumbv2/123dok/4375252.3192401/8.918.189.728.239.982/diagram-flowchart-transformasi-daubechies-menggunakan-multiplier-accumulator-digambarkan.webp)